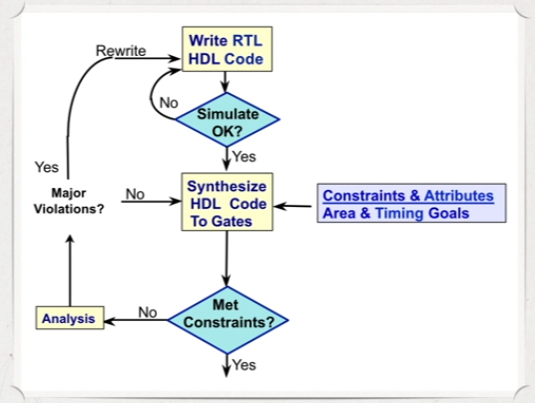

(9)逻辑综合添加约束(时序、DRC)

一、前言

dc综合是一个不断迭代的过程,如果设计的RTL代码不满足时序约束的需求,则需要重新进行修改,然后再去综合,一直迭代到时序满足需求。

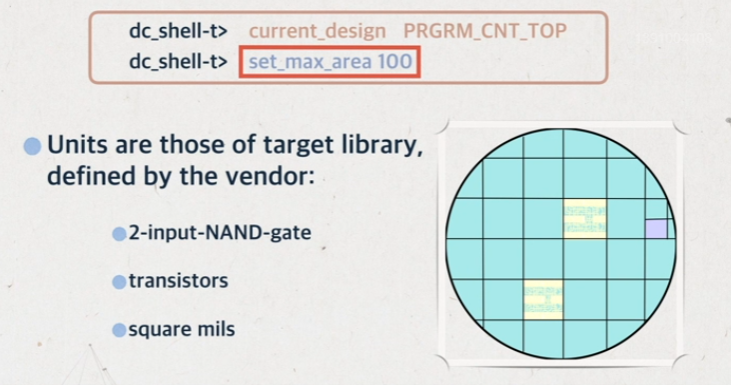

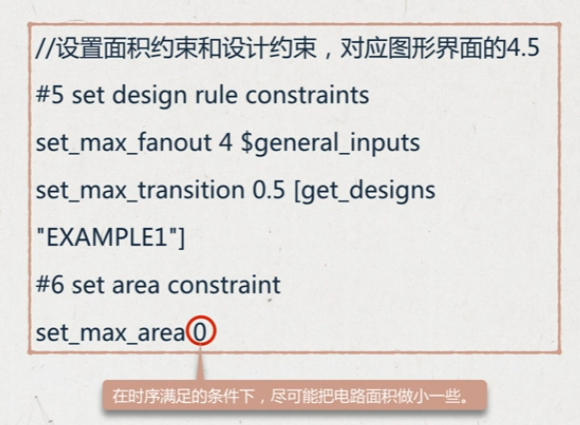

二、面积约束

面积约束指令:set_max_area 100

面积约束的定义有三种,一种指的是两输入与非门的个数,一种是晶体管的个数,第三种是平方微米(实际面积)。

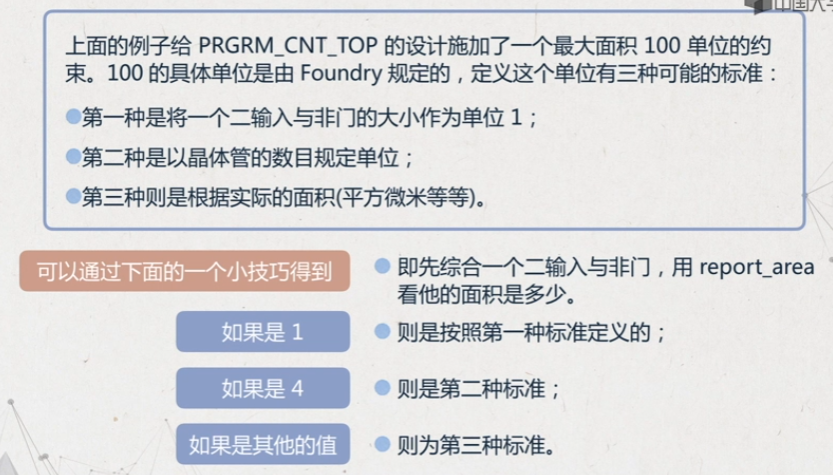

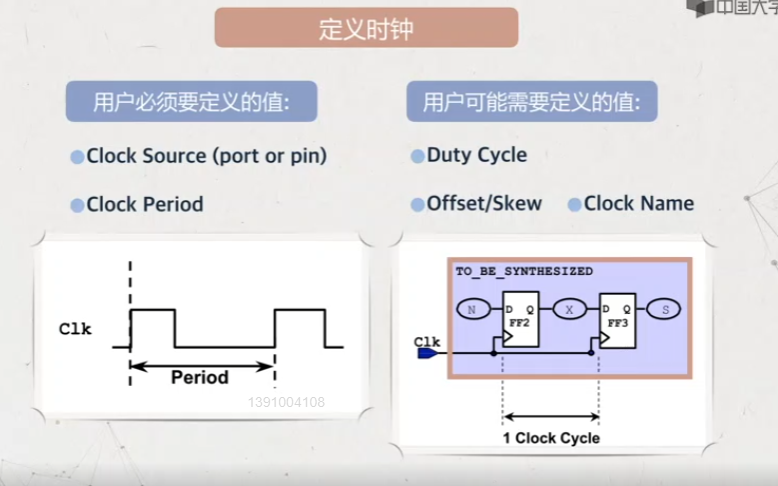

三、时序路径约束

目标:约束电路中的所有时序路径

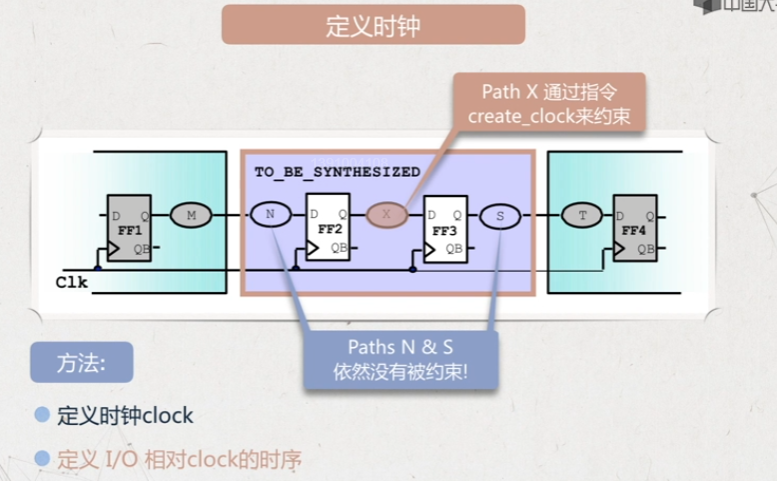

四种路径:输入到寄存器;寄存器到寄存器;寄存器到输出;输入直接到输出的路径。

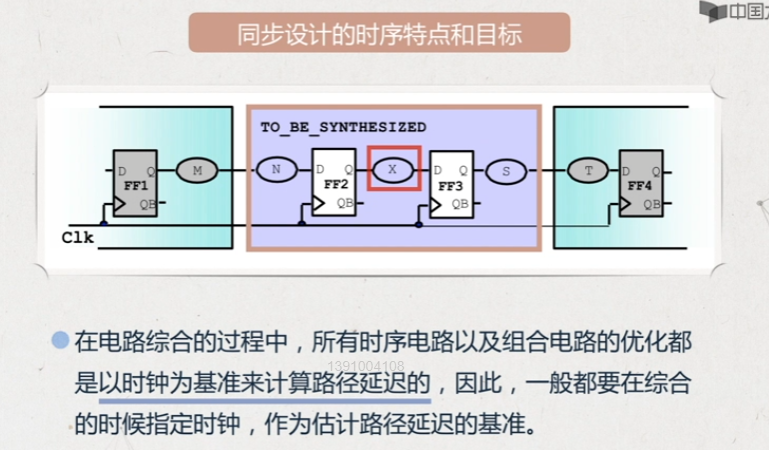

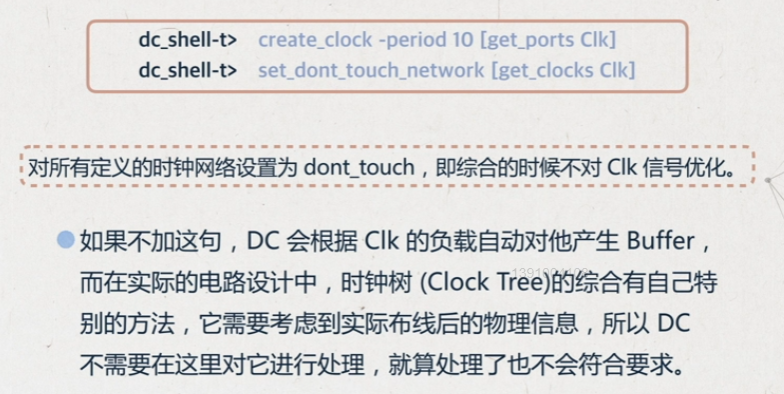

get_ports:设计中的时钟端口,使用create_clock定义了时钟的周期10ns

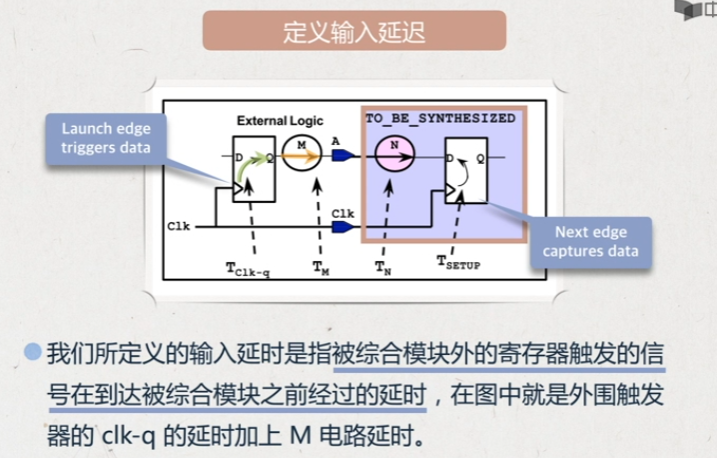

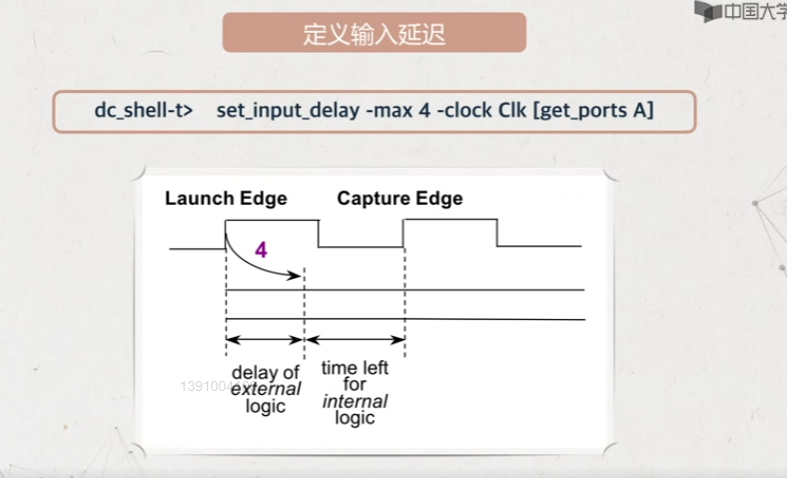

get_ports A:将输入延迟施加在A端口上

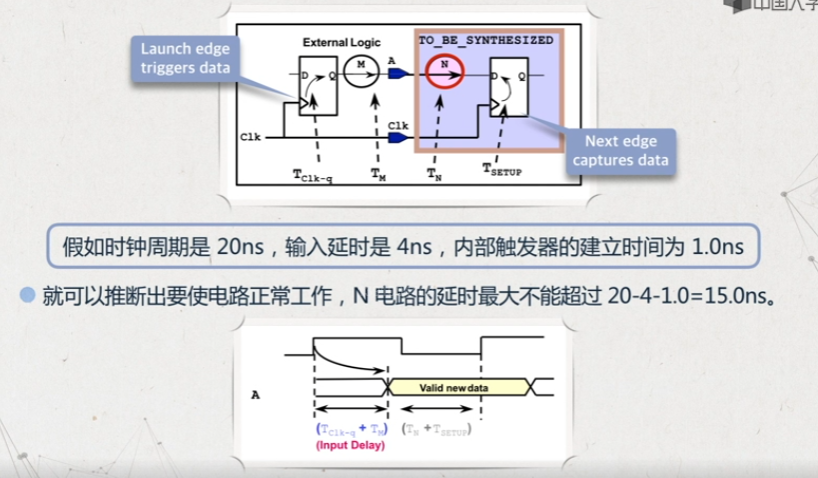

max:该端口最大的延迟是多少(最大延迟通常用来计算建立时间)

clock:该端口的延迟是针对哪个时钟域

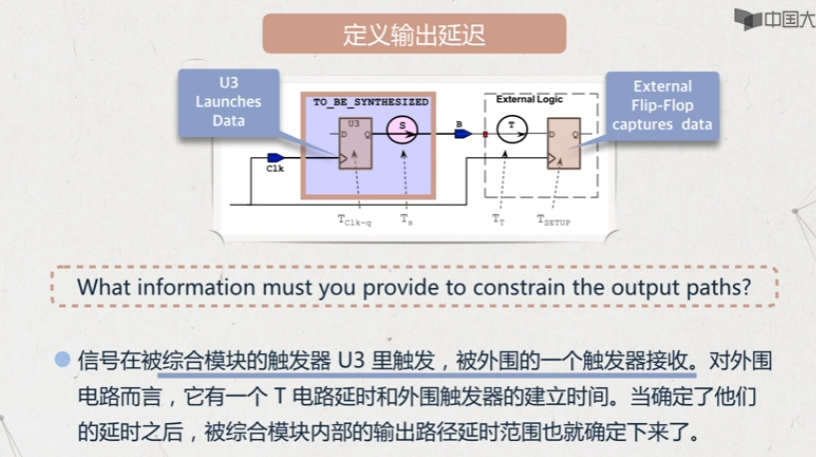

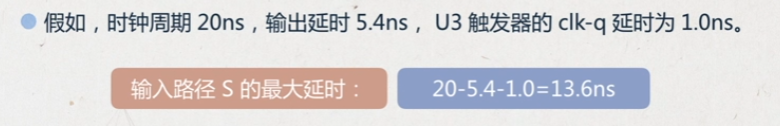

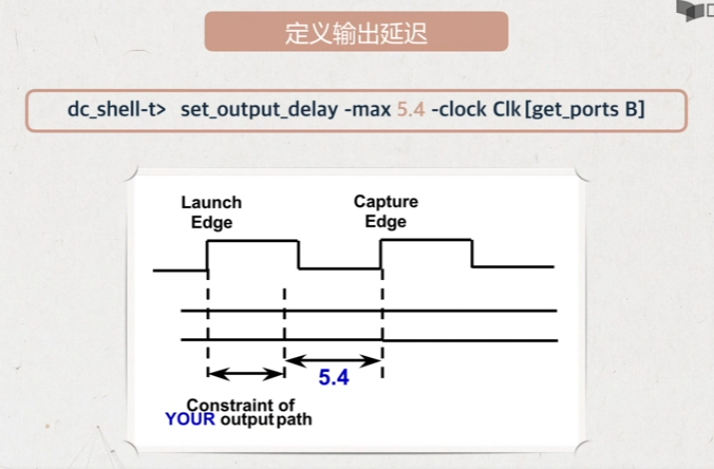

例:待综合的电路为右边红框中的电路,如何对其进行时序约束?

/*********************************************************************/

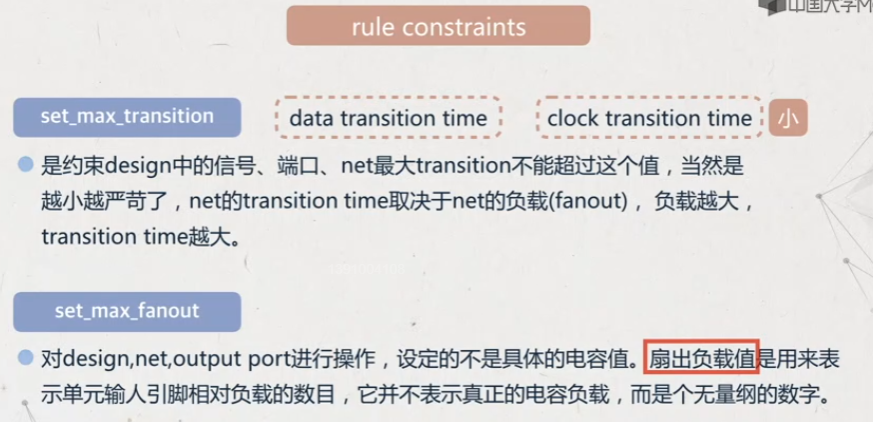

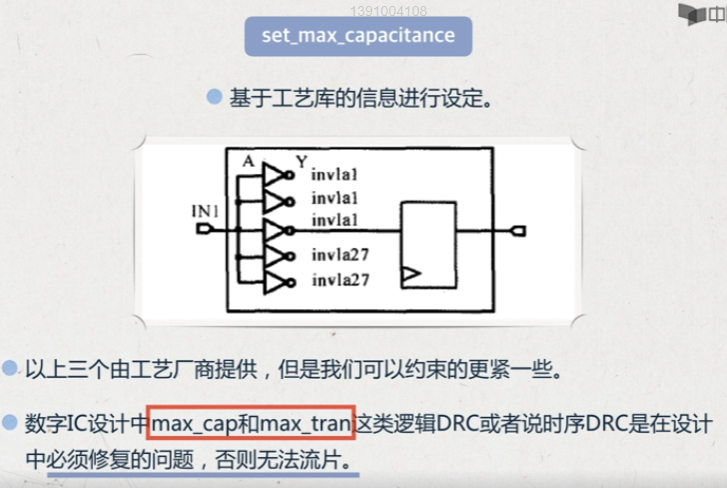

四、DRC约束

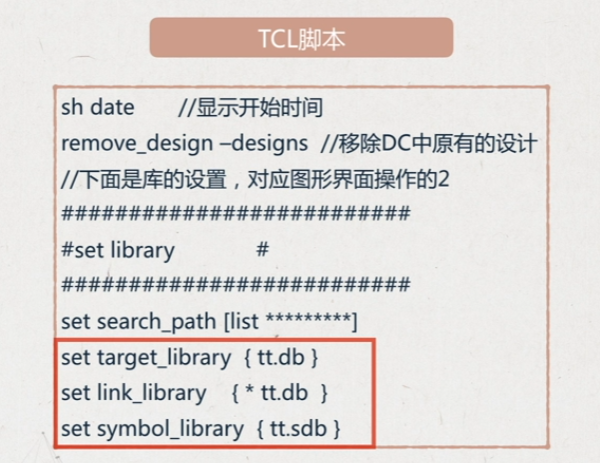

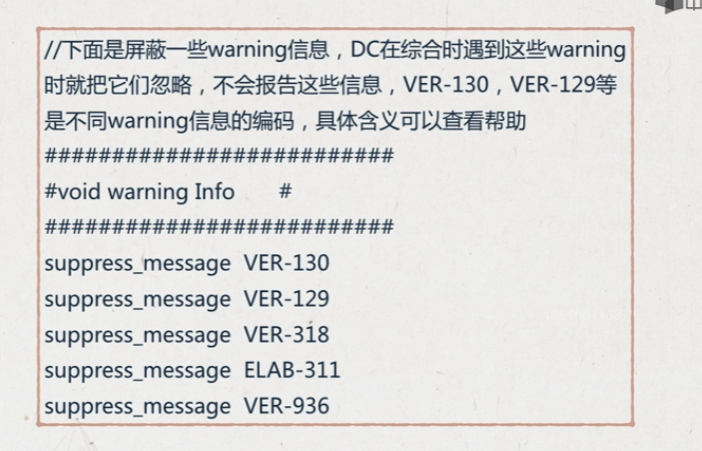

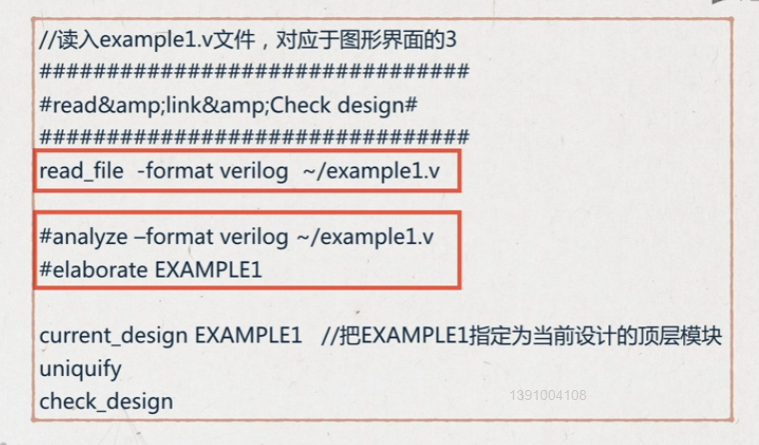

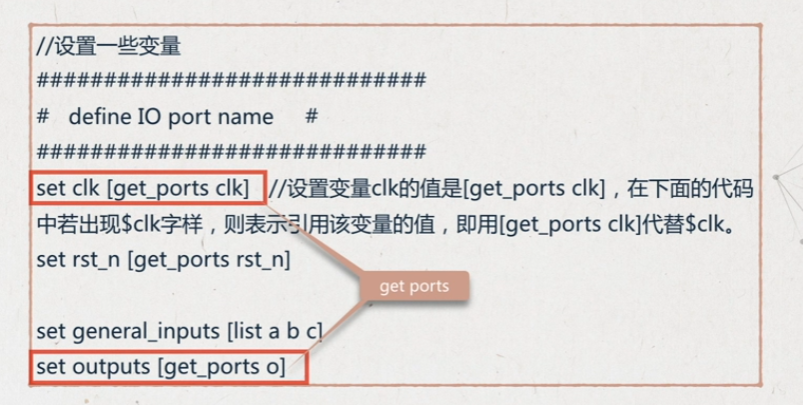

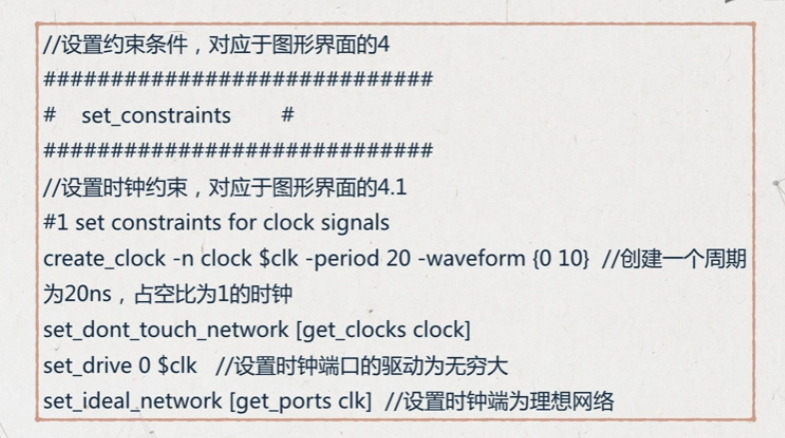

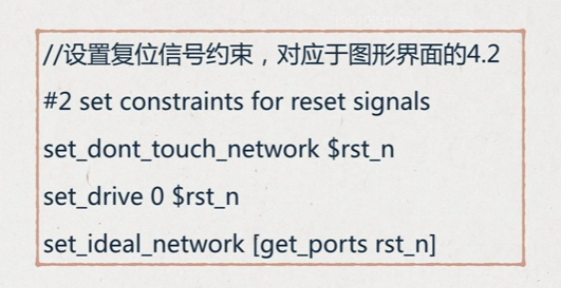

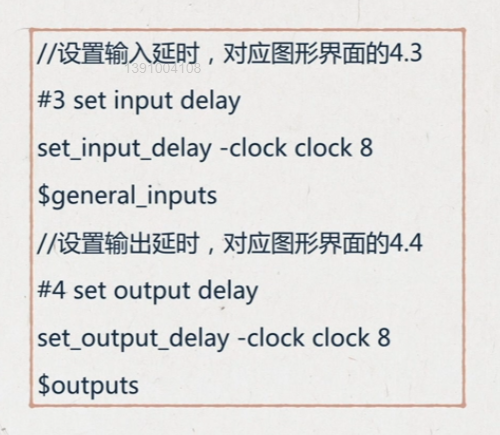

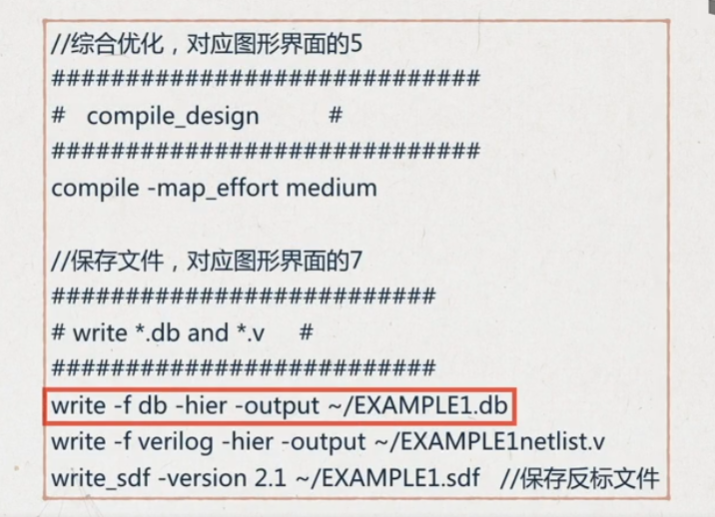

五、一个具体的tcl脚本

注意这里dont_touch和理想网络的区别,dont_touch是让dc不综合

将整个工程以ddc的形式保存,方便后续查询

保存网表文件,用于之后的布局布线和后仿真

需要保存sdf文件,该文件标注了用到的标准单元的延迟值,同时在后仿时也需要sdf文件

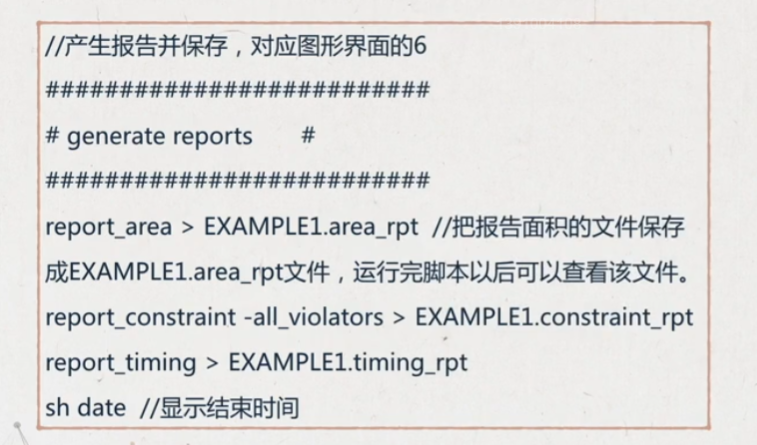

保存报告:面积、约束违例、时序

面积报告中包括时序电路面积、组合电路面积以及总面积

时序报告主要观察建立时间和保持时间是否满足要求

约束违例报告反应了逻辑综合过程中哪些约束没有达到要求

/*********************************************************************/

重点讲一下时序报告

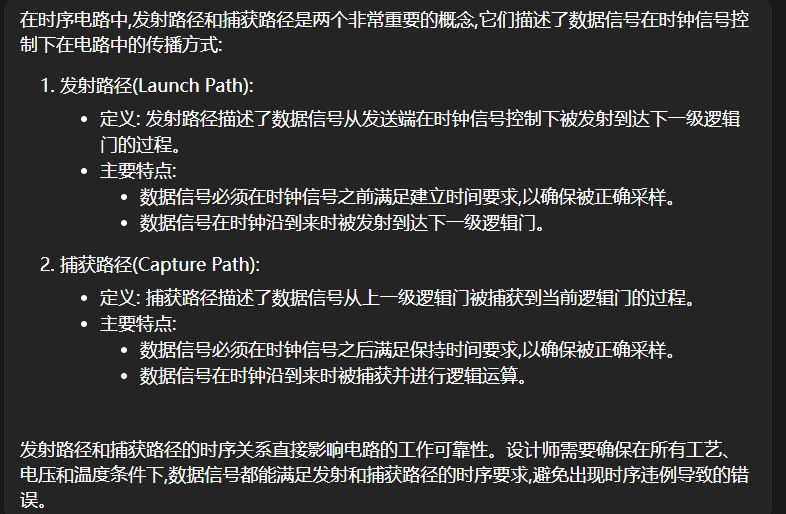

主要包括:表头、数据发射路径、数据捕获路径、时序结果

max说明是建立时间报告,若为min则说明是保持时间报告

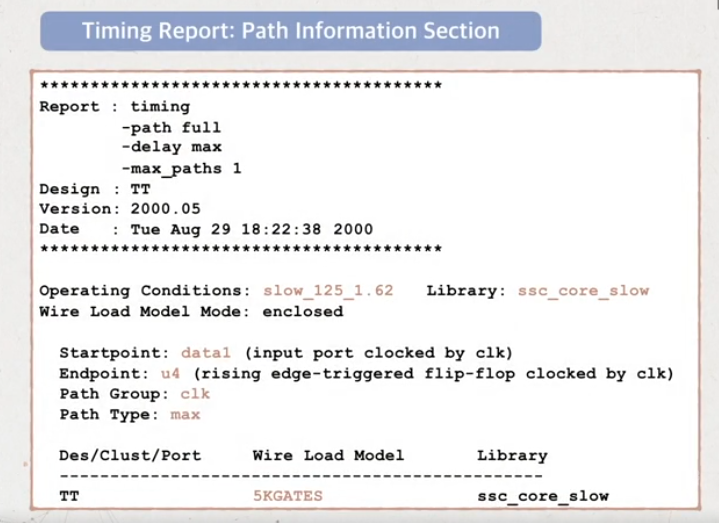

第一段是操作条件的信息,可以看到环境的选取和设置

wire load model反映了线载模型的设置

通常,时序报告给出的路径为关键路径,即延迟最大的路径,图中的path group为clk

startpoint和endpoint给出了关键路径的起点和终点

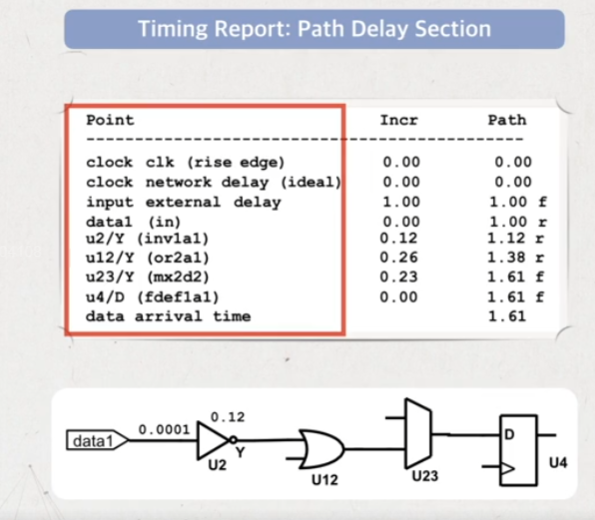

发射路径报告

第一列:路径上经过的各个点

第二列:Incr,指的是路径中每个点自身的延迟

第三列:该路径累积的延迟值

data arrival time:该路径结束的时间点

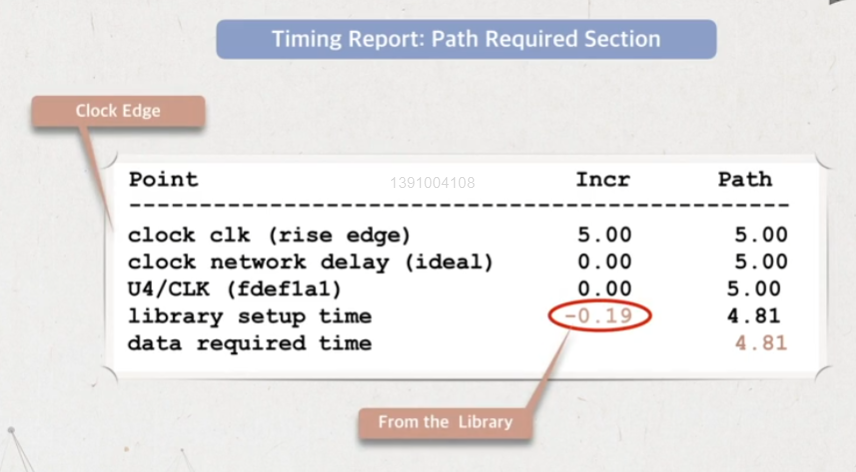

捕获路径报告

因为是建立时间路径,所以需要减去一个建立时间(library setup time)

data required time:要求到达的时间点

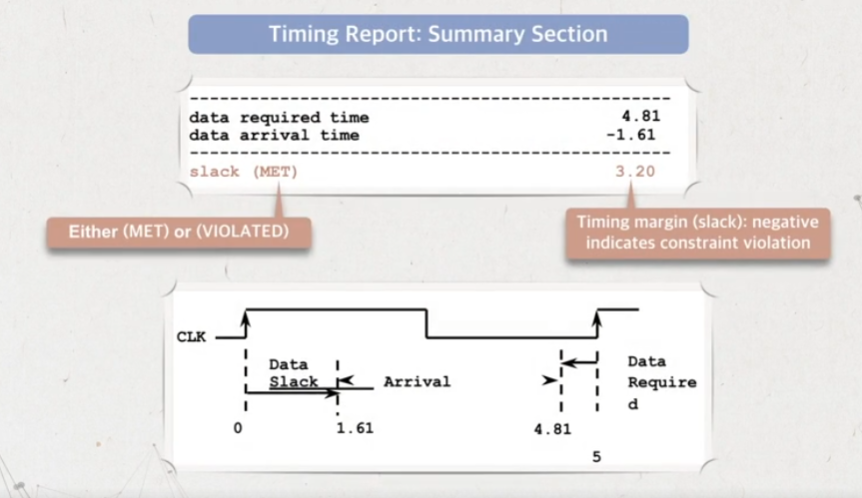

时序报告结果

以一个slack的形式表示,对于建立时间,等于data required time-data arrival time。大于0表示满足时序要求,

/*********************************************************************/

附: