【项目2:高速数据采集】

概要

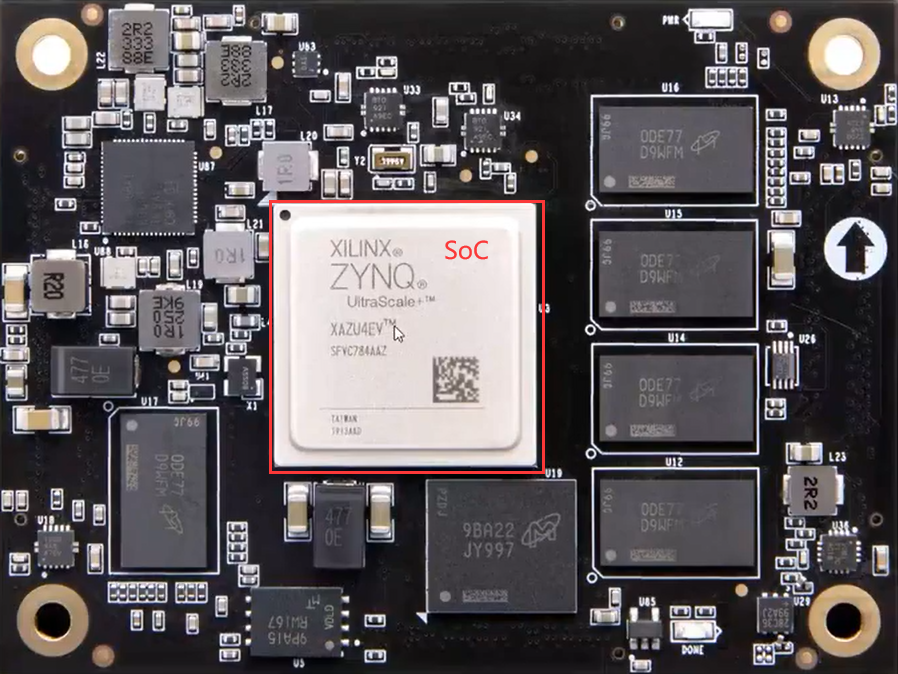

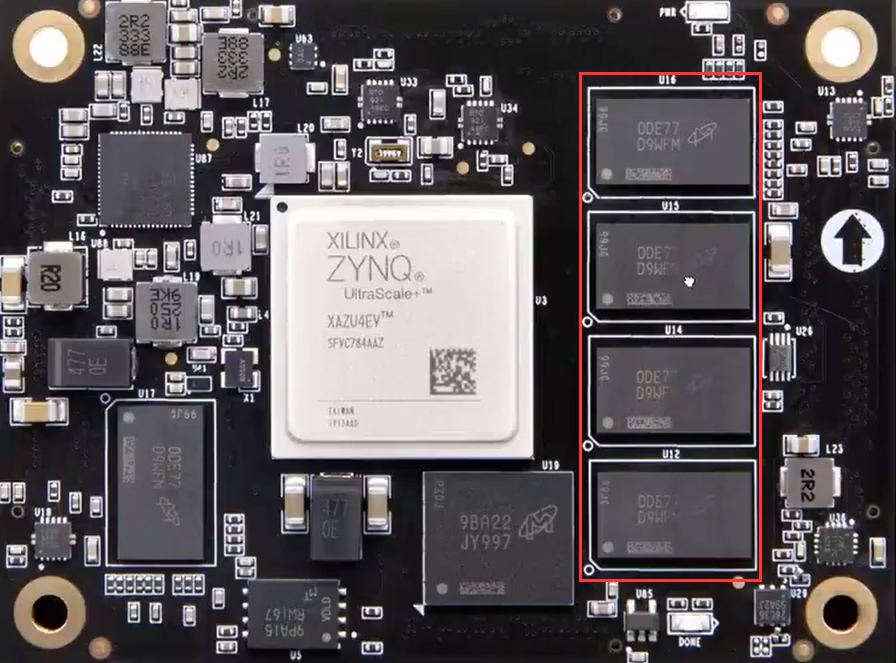

使用的核心板:开发板使用的是 Xilinx 公司的 Zynq UltraScale+ MPSoCs EV 系列的系列的芯片,型号为 XCZU4EV-1SFVC784I

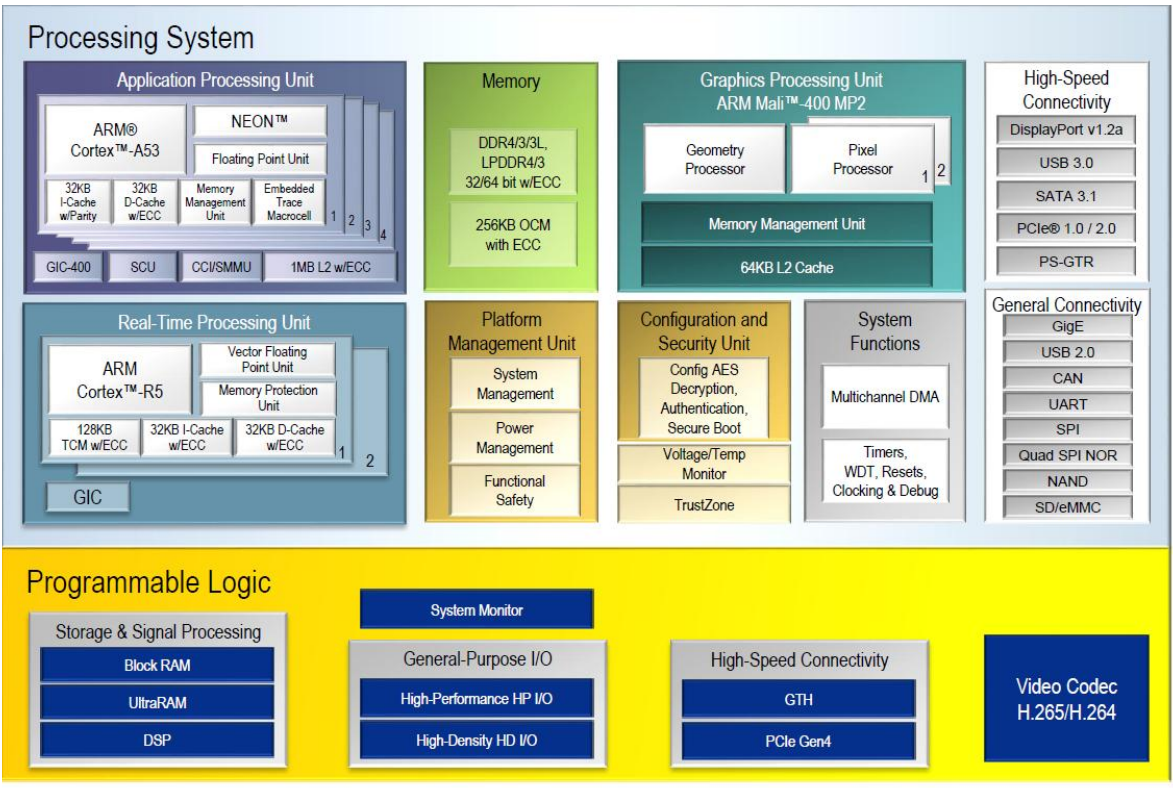

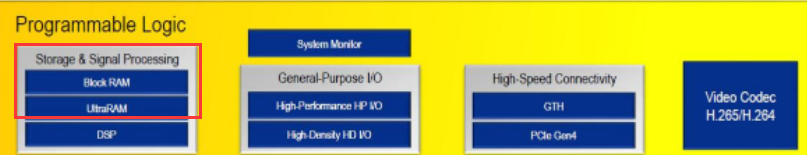

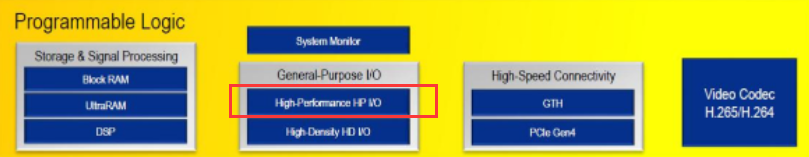

在明确了使用的核心板后,需要翻看芯片手册,看看有什么资源可以使用

ZU4EV 芯片的总体框图如下:

使用PCIe高速接口

数据流向

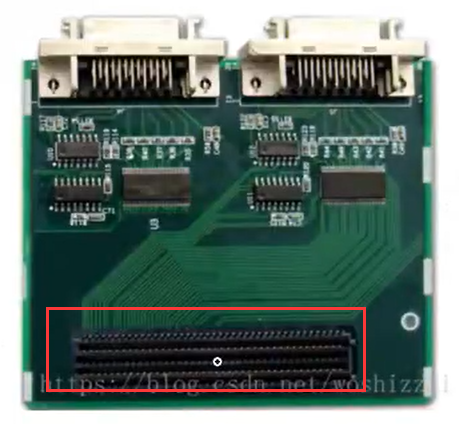

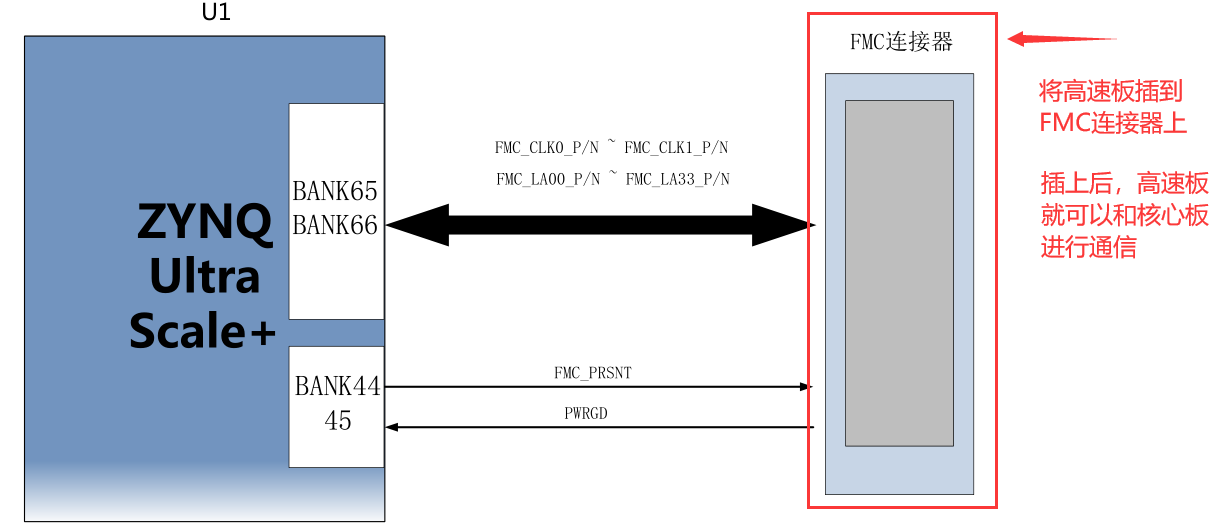

扩展板

使用扩展板上的FMC连接器,使用下图中的接口实现硬件连接,

FMC扩展口有36对差分信号

数据存储

由于从高速板传到FPGA上的数据很多,FPGA内部存不下,需要使用外部存储器;由于数据是异步,所以需要缓存

数据输入后,暂时缓存到RAM中

高速IO

数据要进入芯片,首先通过高速IO传入,

DDR控制器

然后数据通过总线存放到DDR4存储芯片里,ZU4EV中有4片DDR4存储芯片挂在PS部分;其实DDR也是起到缓存作用,先把数据写进去,然后再读出来

APU

软件上起到控制作用,APU可以通过总线访问PL部分去做控制,读写PL中的寄存器;

在PL中有SPI模块,APU通过控制SPI模块实现读和写

高速

PCIe-IP核

RPD、LPD

通过这两个总线接口,可以实现FPGA和APU的通信

带S的是从机,只能被动得写入和被别人读

带M的是主机,可以主动写入数据和读数据

数据传输的方向只能是从M到S