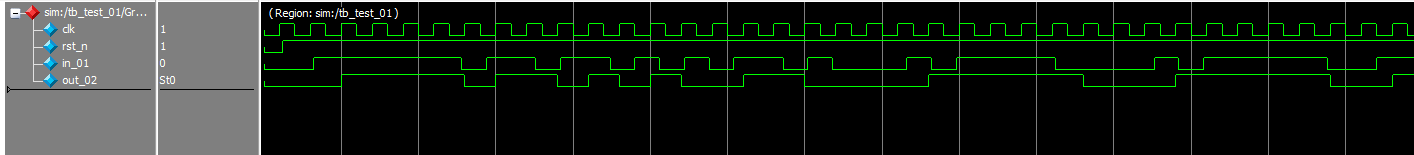

【D触发器】— 时序图

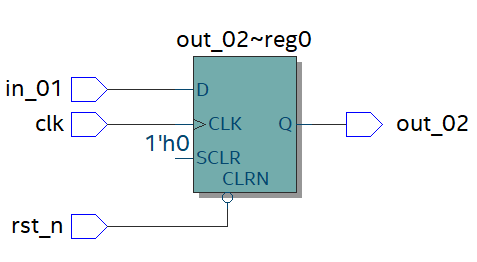

一个非阻塞赋值可以综合成一个D触发器

module test_01 ( input clk, input rst_n, input in_01, output reg out_02 ); always@(posedge clk or negedge rst_n)begin if(rst_n == 1'b0) out_02 <= 1'b0; else out_02 <= in_01;// 综合成D触发器 end endmodule

测试文件

`timescale 1ns/1ns module tb_test_01; reg clk; reg rst_n; reg in_01; wire out_02; initial begin clk = 1'b0; rst_n = 1'b0; in_01 = 1'b0; #12; rst_n = 1'b1; end always #16 in_01 = {$random}%2; initial begin $display("in_01 = %d ",in_01); end always #10 clk = ~ clk; test_01 test_01_inst ( .clk(clk), .rst_n(rst_n), .in_01(in_01), . out_02(out_02) ); endmodule