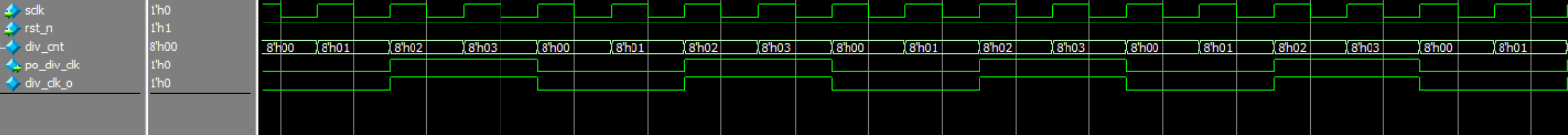

【时钟分频】— 50MHz产生12.5MHz的4分频时钟

一、设计文件

module div_clk( input wire sclk, input wire rst_n, output wire po_div_clk ); parameter DIV_END = 8'd3; reg [7:0] div_cnt; reg div_clk_o; //div_cnt always @ (posedge sclk or negedge rst_n) if(rst_n == 1'b0) div_cnt <= 'd0; else if(div_cnt == DIV_END) div_cnt <= 'd0; else div_cnt <= div_cnt + 1'b1; always @ (posedge sclk or negedge rst_n) if(rst_n == 1'b0) div_clk_o <= 1'b0; else if(div_cnt == 'd1) div_clk_o <= 1'b1; else if(div_cnt == 'd3) div_clk_o <= 1'b0; assign po_div_clk = div_clk_o; endmodule

二、测试文件

`timescale 1ns/1ns module tb_div_clk; reg sclk,rst_n; wire po_div_clk; initial begin sclk = 0; rst_n = 0; #100 rst_n <= 1; end always # 10 sclk = ~sclk; div_clk div_clk_inst( .sclk (sclk), .rst_n (rst_n), .po_div_clk (po_div_clk) ); endmodule

三、波形图