MIPI D-PHY简述

1 概述

- mipi接口在视频领域广泛使用

- sensor和soc的接口是mipi csi-2

- soc和mipi屏的接口是mipi dsi

- D-PHY是广泛使用的物理层协议,除此之外,还要C-PHY和M-PHY。 我们只用到D-PHY,本文对D-PHY的简要说明。

2 接口简述

2.1 lane

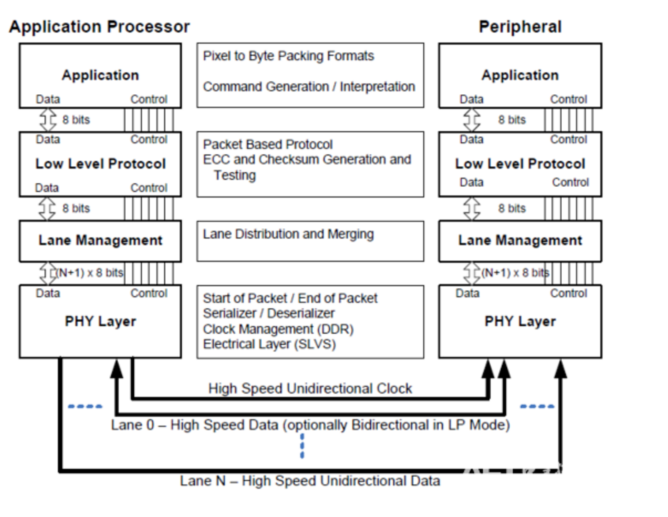

如下图:

- 两个通过MIPI通信的硬件,最底层由若干lane组成

- D-PHY支持最少1个clock+1个data lane,最多1个clock+4个data lane

- 公司的视频芯片,2和4 lane指data lane,clock是必须的,没有包含在内

- clock lane总是单向的,data lane可双向,但实际应用中,只有DSI lane0实现为低速双向

2.2 lane内部

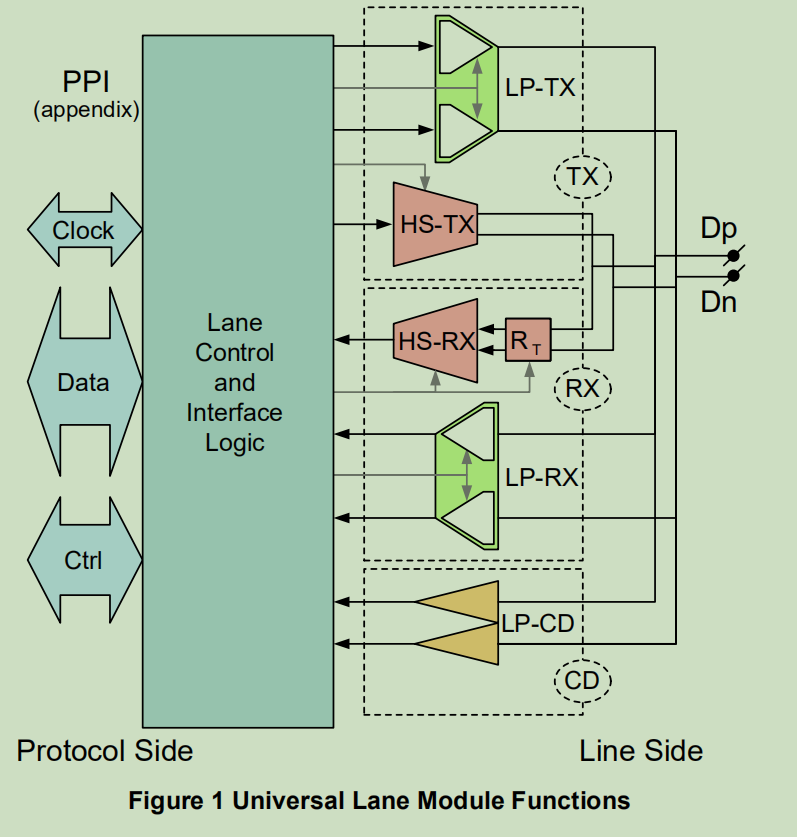

如下图:

- HS是high speed

- LP是low power

- LP和HS都可以配置为双向

- CSI-2实际配置, HS单向, LP单向

-

DSI实际配置,DATA0 有LP双向,HS单向,其他DATA LANE HS单向,LP单向

- 针对这个全集的裁剪,有个表格,CIL-**表示裁剪内容,知道就好了

2.3 Dp、Dn电特性

- HS 差分,LP单端

- HS 80~1500 Mbps, 带deskew capability是最大到2500Mbps

- LP 最大10Mbps

3 各种Lane State

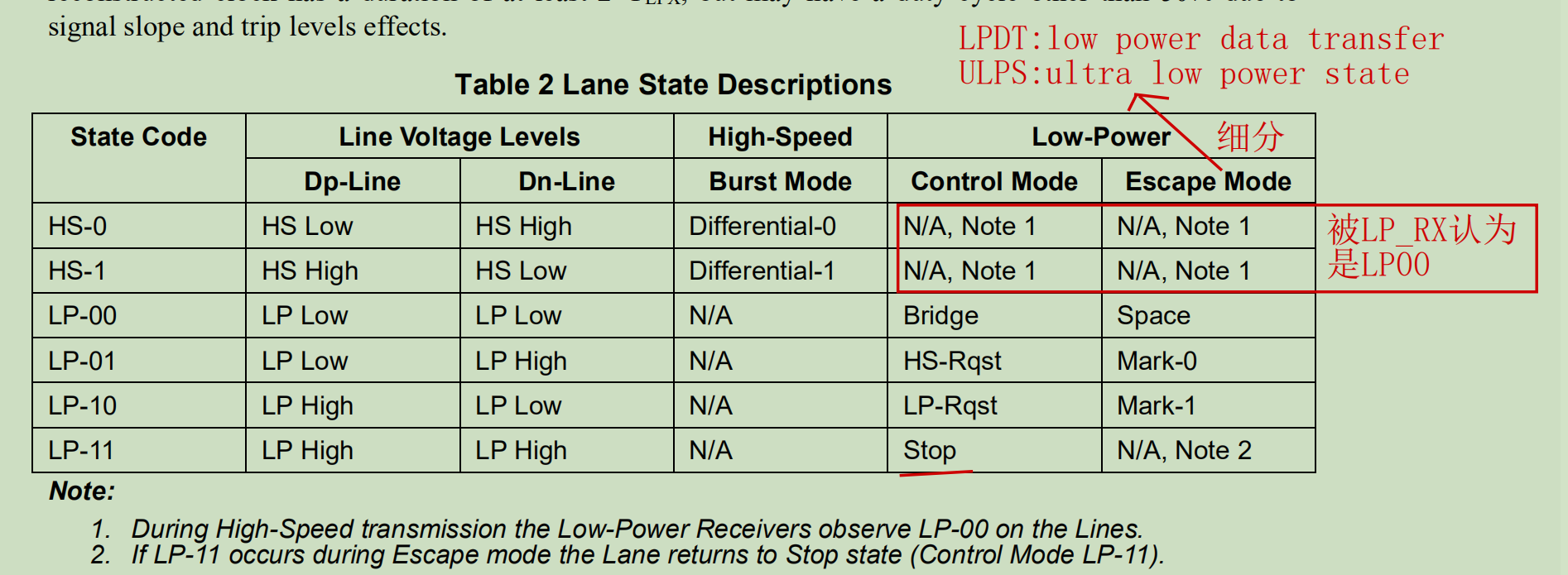

如下图:

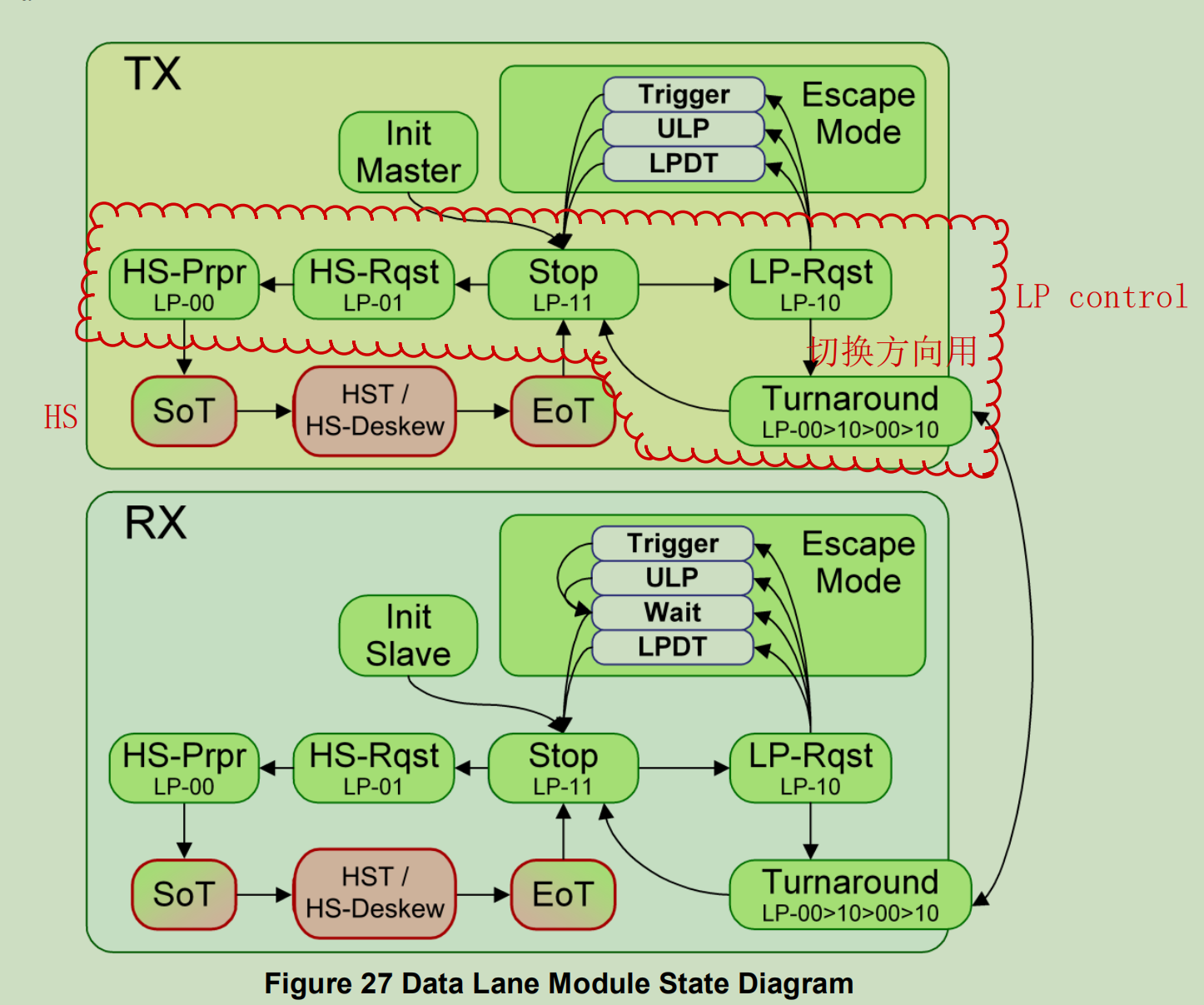

- HS模式用于高速传输,进入和退出HS模式时,都需要在LP的control模式下做若干LP**操作

- 一般在HS和LP的control模式之前切换

- Escape模式的作用是实现低速模式的通信,例如DSI的低速命令收发就是Escape的LPDT模式

- 即使没有Escape模式,一般LP单向也是需要的,因为进出HS模式需要LP的control模式进行操

- 只有从LP control模式才能进入Escape模式

- LP模式下,RX端不需要clk,但TX端需要用到,所以escape clk也是要配置的

- ULPS模式我们暂时没有用到

下图是各个状态转换的状态机:

参考

Specification for D-PHY V1.2