xilinx vivado DDR3 MIG IP核中系统时钟、参考时钟解释及各个时钟的功能详解

注:在使用xilinx的MIG 核时,会有许多关于时钟的配置,时间长了容易混淆,特意记录一下为以后快速回忆,如有错误请留言指正。

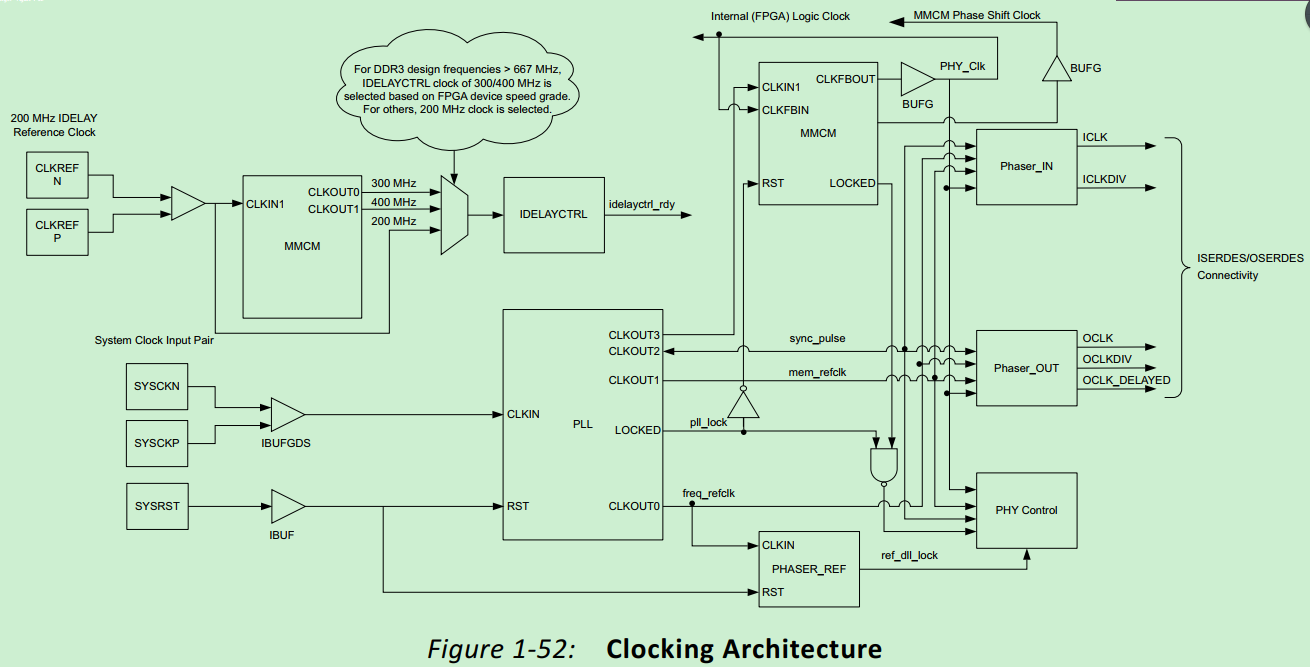

0、先贴出来DDR3的时钟树,这个图展示了参考时钟设置的强制规定。

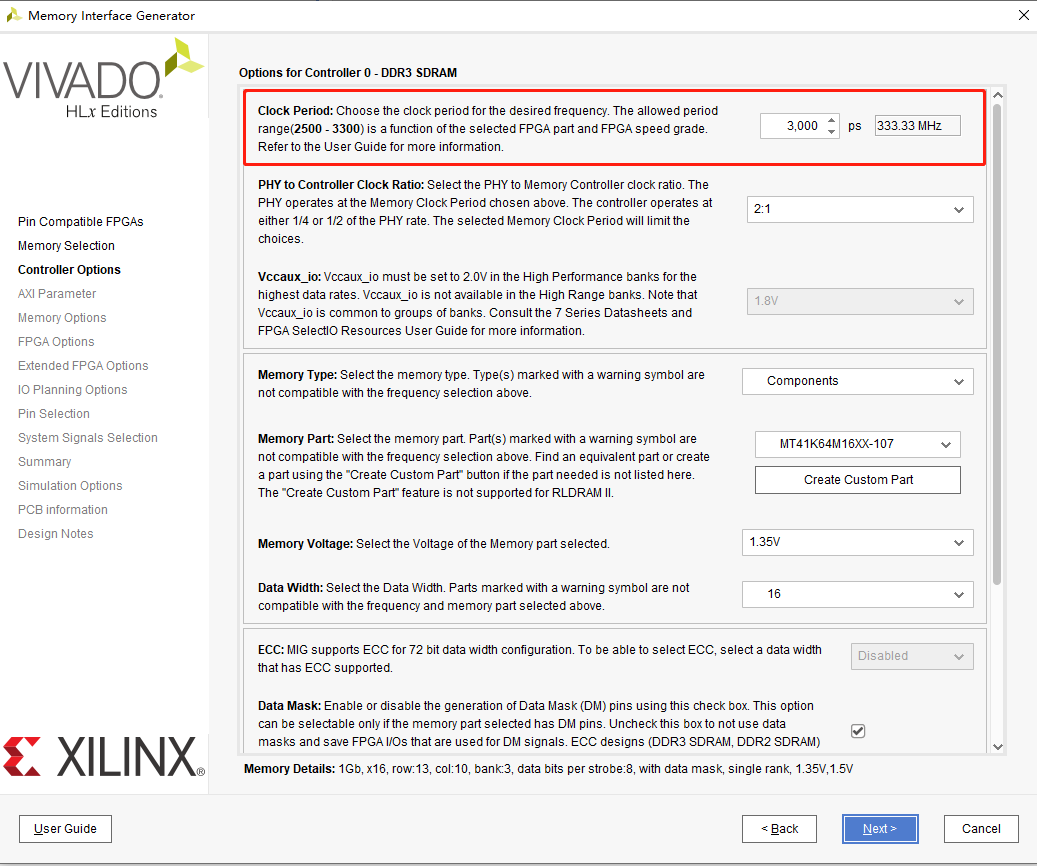

1、Clock Period ,是设置DDR3的工作频率,这个速率与FPGA的速度等级相关

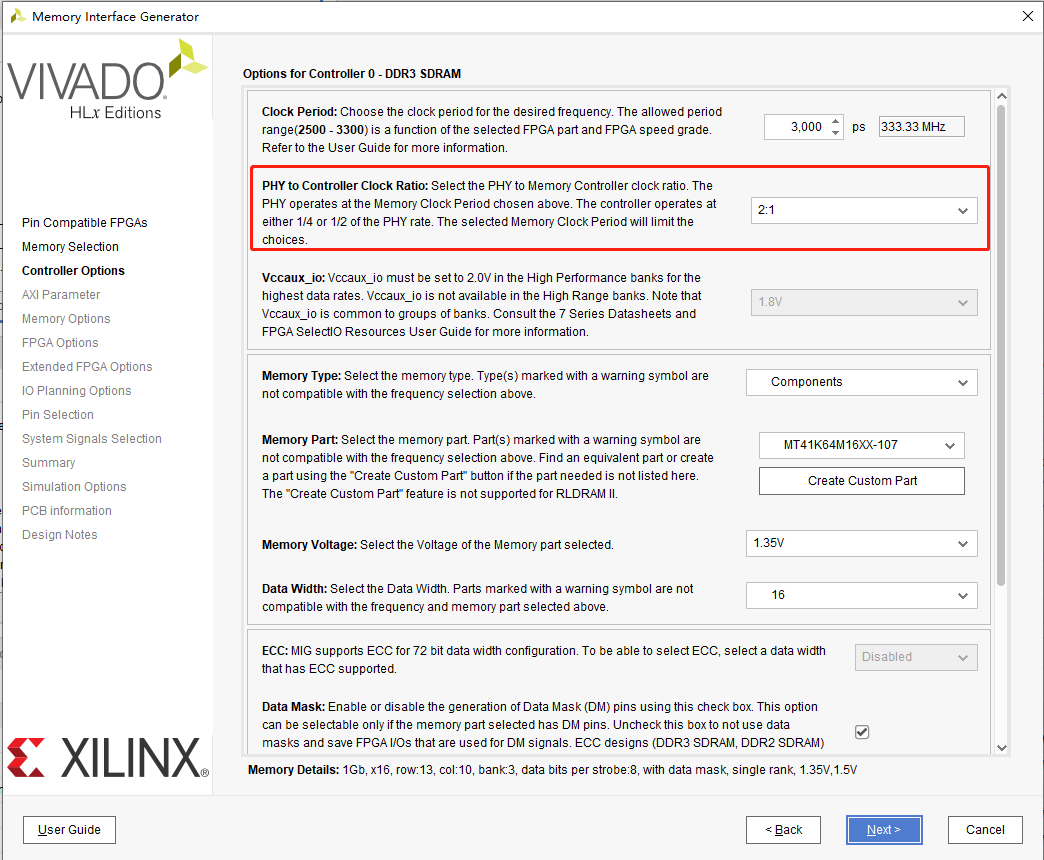

2、PHY to Controller Clock Ratio,该时钟是MIG输出给UI的时钟,为了避免跨时钟域的问题,我们用这个ui_clk驱动自己逻辑代码

这个速率可以设置4:1 /2:1,我设置的2:1,则 ui_clk=333.33/2=166.665MHz

a、我设置的为333.33MHz,因为是双边沿,实际速率=333.33*2=666.66MHz

b、ui数据接口位宽:同时这个比例会影响到ui接口的数据位宽;

2:1时:ui位宽是物理层位宽的4倍(16*4=64), 4:1时:ui位宽是物理层位宽的8倍(16*8=128)。

注:这个图中物理data位宽配置的是16bit。

从时钟频率和数据匹配的角度也能得出这个计算关系是正确的。

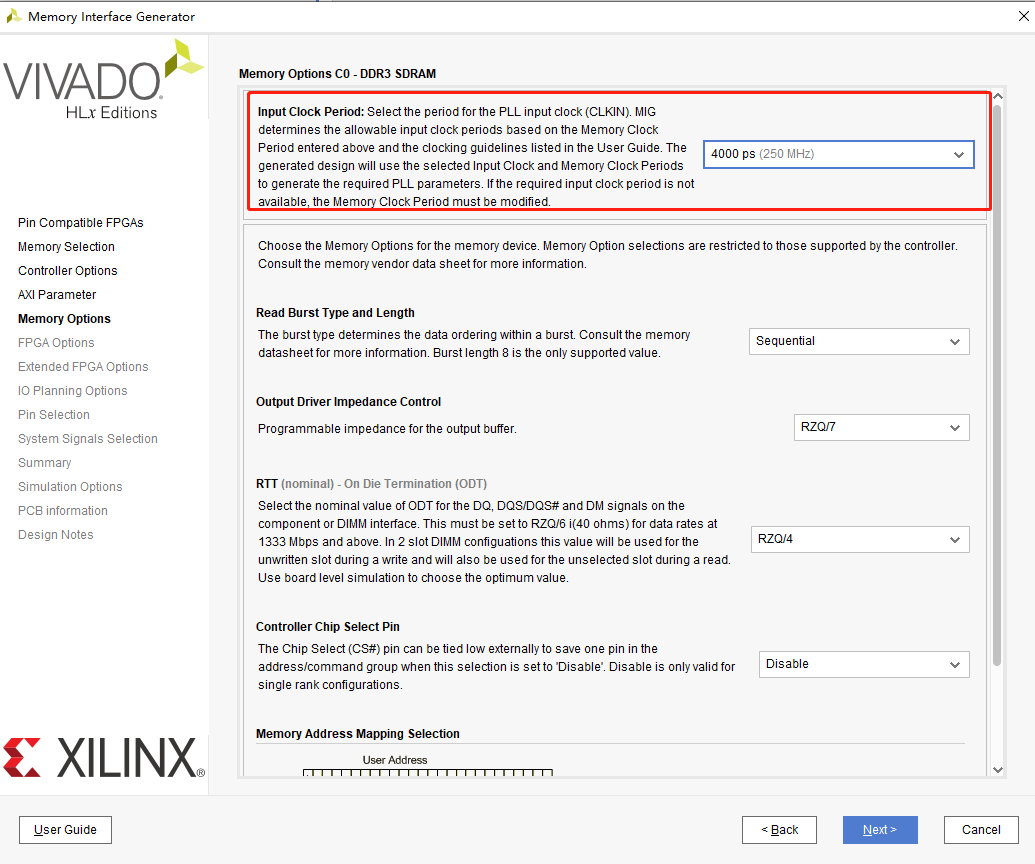

3、input clock period,输入时钟频率,这是输入给MIG 核的时钟,IP核内部会自己调用pll和MMCM 来产生自己的工作时钟

我设置的是250MHz

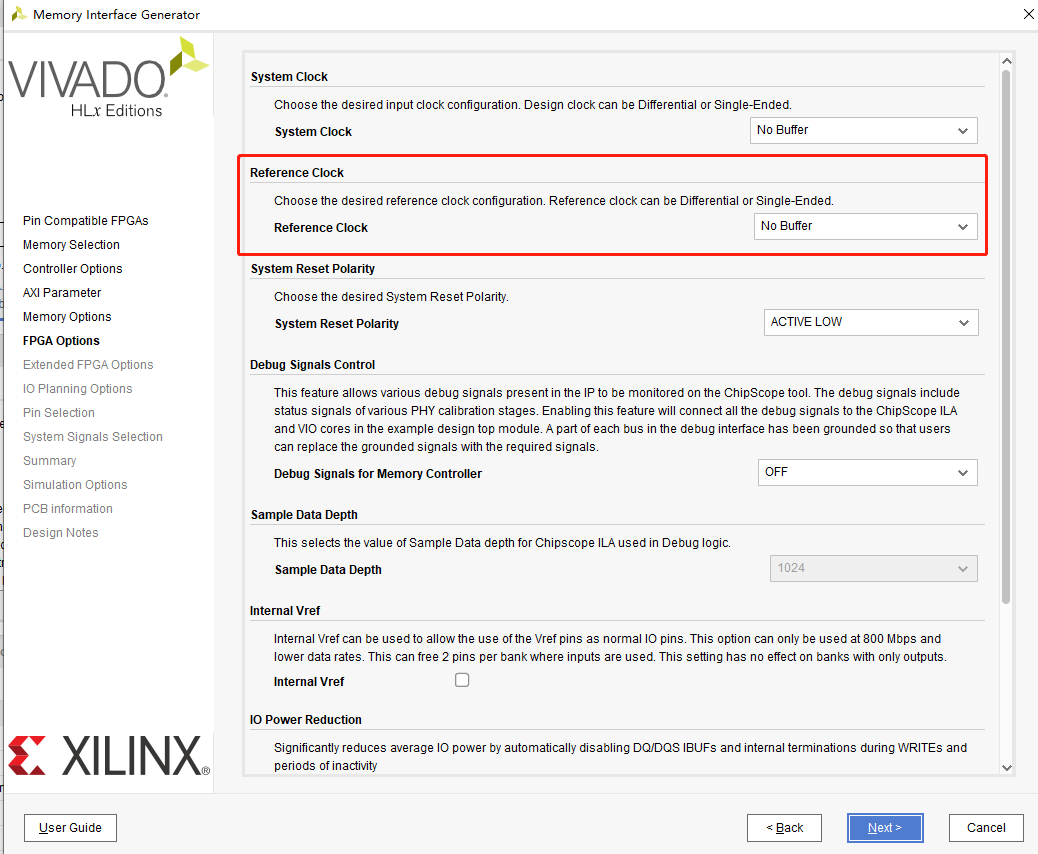

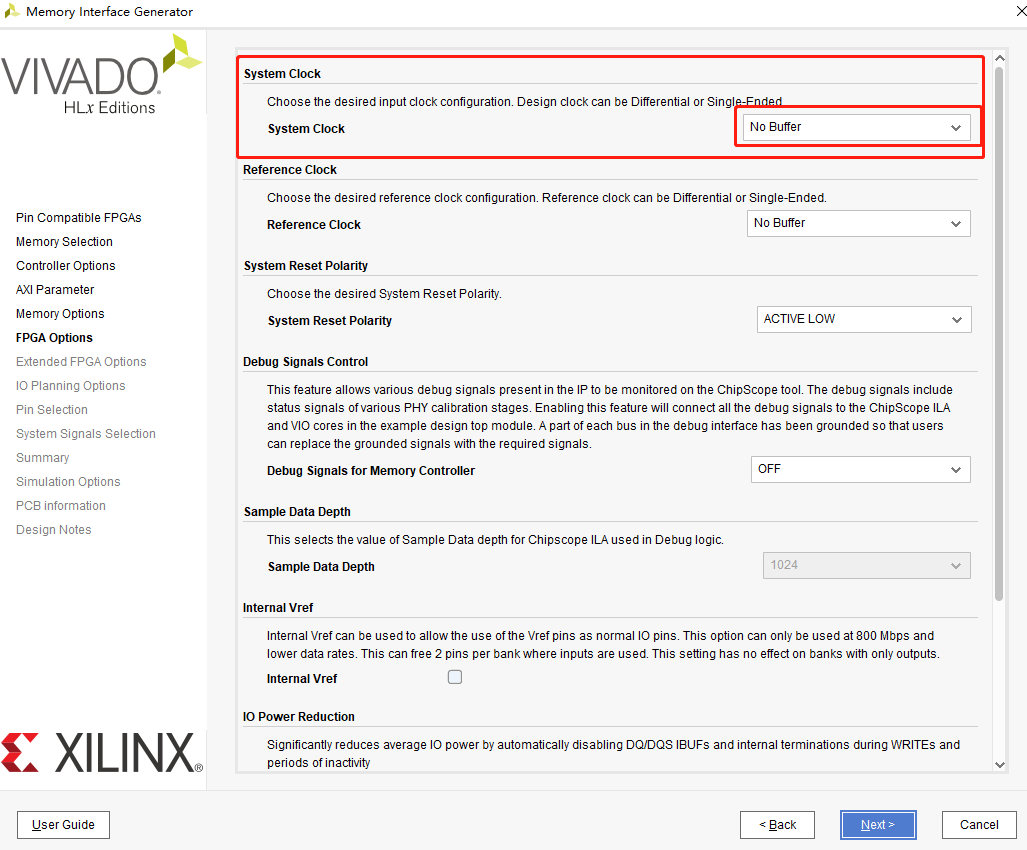

4、system clock,是设置步骤3的输入时钟的属性,可以是外部晶振(差分、单端)或者是PLL输出的时钟

我用的是PLL输出的时钟,PLL输出时配置GBUFF,所以这里选择No Buffer

5、Reference clock,是设置MIG的参考时钟,这个时钟频率是固定的,如果工作频率>666MHz ,参考时钟固定为300MHz/400MHz,

其他工作频率固定为200MHz,这里设置时钟的属性,可以是外部晶振(差分、单端)或者是PLL输出的时钟

我用的是PLL输出的时钟,PLL输出时配置GBUFF,所以这里选择No Buffer

注:如果system clock的频率在199-201MHz之间,这里会出现一个use system clock 的选项,意思就是用系统时钟作为参考时钟