scan详解

在可测性设计(DFT)技术中,scan可以说是最重要的一部分。由于对时序电路直接进行测试十分困难,而扫描测试方法通常能很好地解决这一问题。

Scan 技术最初由Kobayashi等人提出来的,它的优点是基本原理是时序电路可以模型化为一个组合电路网络。

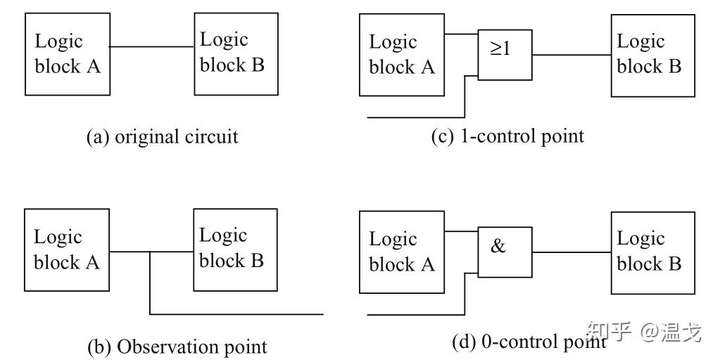

Scan design的设计目标是能够提高可控性和可观测性,如下图所示:

图(a)是原始电路。通过在逻辑A和逻辑B之间插入一些额外的硬件电路,便可观测&控制逻辑A传递到逻辑B的值。

在深入了解scan技术之前,我们先来比较下分别针对组合电路和时序电路的测试过程。很显然,在芯片制造出来后,我们只能通过其输入输出端口来对芯片进行各项检测。

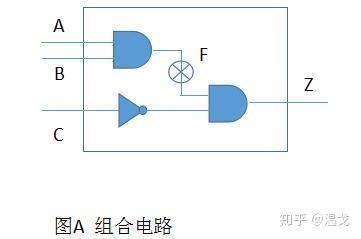

如图A所示的组合电路中,假设F处有一短接电源地的固定0故障 (stuck-at 0 fault) 。要检测到这样的物理缺陷,首先要在A端和B端给1的输入激励,这样在F处可以得到1值从而激活目标fault。而要将F处的值传递到输出端进行观测,C端就要有一个0的输入。这样我们就得到了一个能检测到目标fault的结构性测试向量:110 (ABC). 在该组合电路没有故障 (fault) 的情况下,我们应该可以在输出Z端观测到一个正确的1值。而在F处有stuck-at 0 故障的情况下,我们在输出Z端就会观测到0值从而检测到该fault。

接下来,假设在图B的时序电路中包含如图A的组合电路结构及同样的fault。而现在要检测到F处的故障,我们需要遍历各个level的时序单元以确保能激活目标fault并能将其值传递到芯片输出端进行观测。产生结构性测试向量的时间及难度大大增加而且更重要的是,在绝大多数情况下,没办法只依靠一个测试向量,而是需要一个测试向量序列才能最终检测到目标fault。

比较下来,组合电路的测试过程更为简单,通常情况下只需要单个的测试向量就可以检测到目标fault,测试时间更短。而测试时间是测试成本的直接体现。另外,相比较时序电路而言,组合电路往往能得到更高的测试品质。但在实际芯片项目里,实现的往往都是时序电路,我们怎样才能在测试过程中受益于组合电路带来的上述低成本高品质的测试效果呢?

Scan技术就是为解决上面的问题而来。Scan所能带来的好处就是把一个difficult-to-test的时序电路转变为easy-to-test的组合电路。

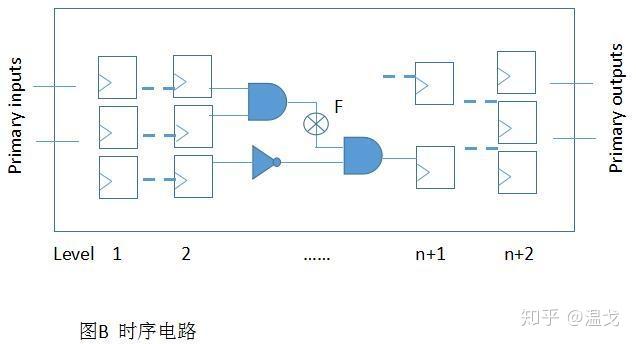

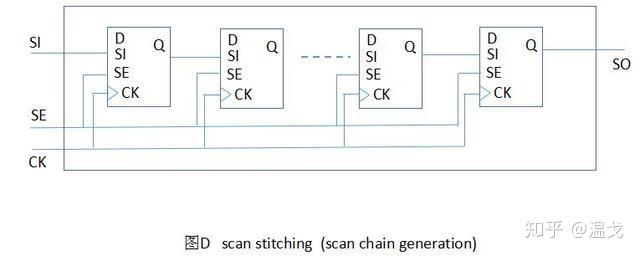

下面我们首先来具体看看实现scan要做些怎样的辅助性设计。其过程包含图C中的scan replacement 及图D中的scan stitching两步,此处以Muxed-D Scan cell 为例。

Scan replacement就是把电路中的normal时序单元(如DFF)替换为一个scan 时序单元(SDFF)。其SE端值为0时,电路工作在正常功能状态并能把D端的值锁存下来;当SE为1时,电路工作在所谓scan mode并锁存SI的值。

Scan stitching 是把上一步中得到的Scan DFF的Q和SI连接在一起形成scan chain。在芯片的顶层有全局的SE信号,以及scan chain的输入输出信号:SI 和 SO。通过scan chain的连续动作,就可以把问题从对复杂时序电路的测试转化成测试组合电路。

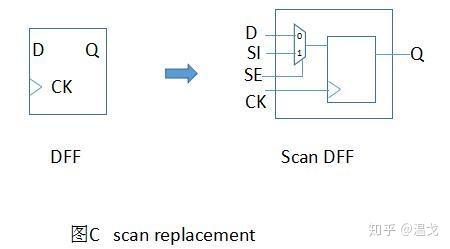

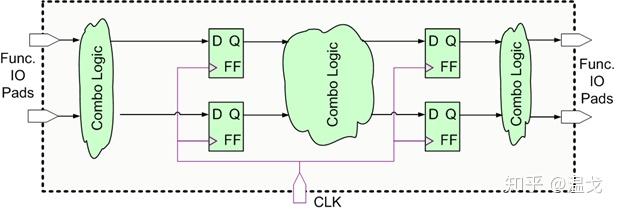

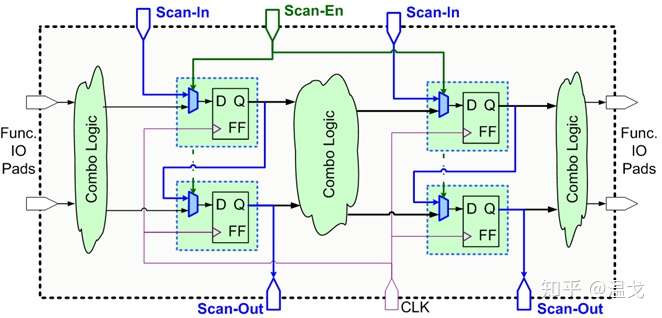

下面我们把时序逻辑和组合逻辑放在一起,来看一下scan insertion 之前和之后的区别:

Before scan

After scan insertion

Scan test 的步骤:

- 把Scan-En设成0,此时电路工作在正常状态(function mode)下, scan insertion对电路的正常功能没有影响。

- 把Scan-En设成1,然后把enable clock来驱动寄存器,在Scan-In端输入测试数据,然后在输出端Scan-Out观测,用此种方法便可以测试Flip-Flop.

- 测试组合逻辑的时候,把Scan-En设成1,然后enable clock来驱动寄存器,在Scan-In端输入测试数据,两个时钟周期后,数据便会送到组合逻辑的输入端。

- 然后把Scan-En设成0,时钟打一拍,经过组合逻辑的输出值便会送到右侧的寄存器中。

- 再把Scan-En设成1,此时scan chain 工作在shift mode,此时便可以把组合逻辑的输出值shift出来,和期望值进行比较。

经过这样一个周期,图中的组合逻辑和时序逻辑便都被测试到了。

Scan作为DFT最为核心的技术,是每个DFT工程师,测试工程师,甚至是前端设计工程师都必须要理解的一个概念。