FPGA工具篇vivado

在电子技术飞速发展的今天,熟练使用相关工具软件是学习SoC的必经之路。但是,由于SoC是一个完整的系统,既包含处理器核、总线、外设等硬件,也包含处理器需要执行的指令,所以对于“软件编程”和“硬件编程”的概念必须要区分清楚。关于“软件编程”和“硬件编程”的概念在很多基础课程(如C语言、数字设计等课程)中已有介绍,但在学习SoC时,由于“软件编程”和“硬件编程”的概念“混”在一起,并且一开始不熟悉工具软件,可能会感觉难以上手。

本文介绍在使用Arm DesignStart计划开放的处理器核搭建SoC并通过FPGA实现的过程中所用工具软件(不介绍如何操作),理清“软件编程”和“硬件编程”的概念,熟悉SoC设计的流程。

软硬件关系

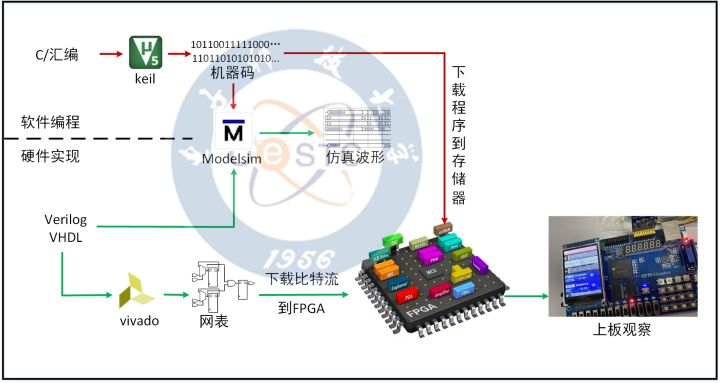

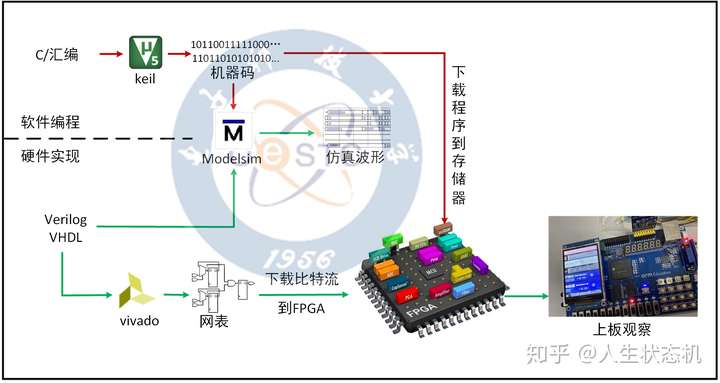

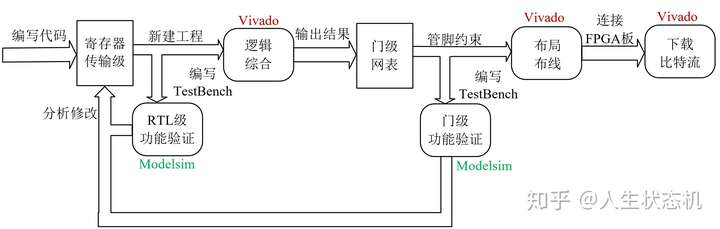

在搭建SoC的过程中需要使用的工具软件有Modelsim,Vivado,Keil,实现流程如下图。

实现流程

实现流程

我们通过Arm DesignStart获取的是一个Verilog语言描述的软核,我们通过添加一些IP实现一个完整的描述SoC的工程。这些IP可以是用IP工具生成的,也可以是我们通过硬件描述语言(Verilog/VHDL)描述的。

Vivado负责将硬件描述语言(Verilog/VHDL)所描述的SoC编译、综合、实现,将FPGA内部本身无序的各种逻辑资源(如查找表、触发器、RAM等)配置成为有序的电路,实现SoC功能。而Keil负责将编写的软件编程语言(C/Assembler)编译成为机器码十六进制文件。将机器码作为RAM的初始化内容,即可进行仿真,在Modelsim软件中观察SoC工作时各个信号的波形。若将机器码通过工具下载到由FPGA实现的SoC中,那么就可以让SoC执行编写的程序,通过FPGA开发板观察执行结果。

从流程中也可以理解“软件编程”和“硬件编程”的区别,“软件编程”编的其实是一条条的指令,描述的是硬件的“动作”,而“硬件编程”编的是一个个的门电路和它们的连接关系,描述的是是硬件的结构。

以下对这三个工具做详细的介绍。

Modelsim

Modelsim主要用于硬件描述语言(Verilog,VHDL等)的仿真,并且支持VHDL和Verilog混合仿真。仿真分为前仿(RTL级仿真)和后仿(综合后门级仿真),这里使用Modelsim仿真属于前仿,也就是功能仿真,主要目的是通过看输出波形图,验证硬件逻辑是否正确。

Modelsim既可以独立使用,也可以和Intel Quartus Prime,Xilinx Vivado软件协同使用。

在官网上可以下载免费版本。

Vivado

Vivado是一个用于FPGA实现的综合工具,由FPGA厂商Xilinx提供,如果使用Intel(Altera)公司的FPGA,需要使用Quartus Prime软件。

从前述内容中知道,Vivado负责将硬件描述语言(Verilog/VHDL)所描述的SoC编译、综合、实现,将FPGA内部本身无序的各种逻辑资源(如查找表、触发器、RAM等)配置成为有序的电路,实现SoC功能。

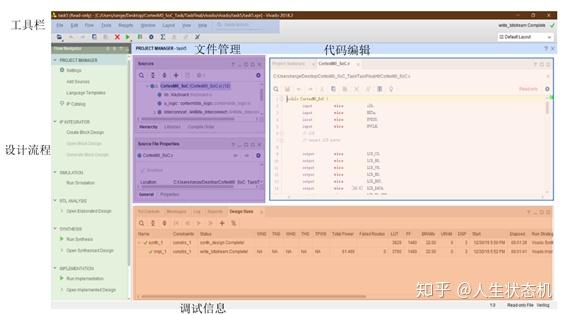

Vivado的软件界面如下图。最上方为工具栏,左侧为设计流程各个的步骤,中间是文件管理和代码编辑的区域,下方为调试信息和输出的一些报告,使用时需注意阅读,以免被一些只报warning但很“神奇”的错误坑了。

Keil

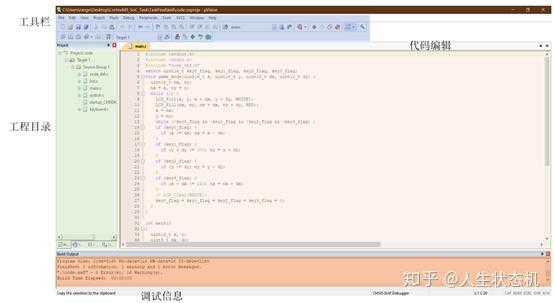

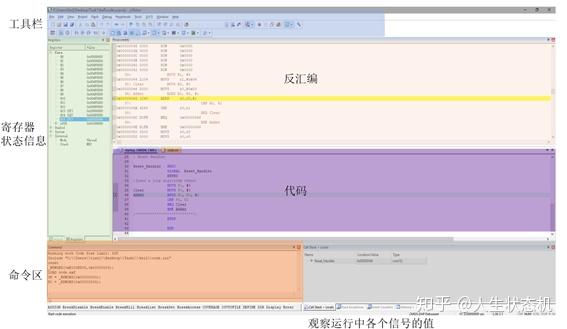

Keil MDK是用于一系列基于Arm Cortex-M的微控制器设备的一个完整的软件开发环境。界面如下图所示,与Xilinx Vivado软件类似,主界面也是由工具栏、工程目录、代码编辑、调试信息组成。Keil软件的主要作用是将C语言/汇编语言写的程序编译成机器码,在进入调试模式时,通过调试器下载机器码到RAM中,CPU启动后,开始一条条地从存储器中取指执行。

Keil主界面

Keil主界面

调试界面可以看到的信息更多,包括执行过程中的寄存器状态信息、反汇编代码,还可以通过右下角的窗口看到运行过程中系统内部一些信号的值,如下图。调试过程中可以设断点,也可以单步运行。

从图中可以看出,Vivado负责将硬件描述语言(Verilog/VHDL)所描述的SoC编译、综合、实现,将FPGA内部本身无序的各种逻辑资源(如查找表、触发器、RAM等)配置成为有序的电路,实现SoC功能。而Keil负责将编写的软件编程语言(C/Assembler)编译成为机器码十六进制文件。将机器码作为RAM的初始化内容,即可进行仿真,在Modelsim软件中观察SoC工作时各个信号的波形。若将机器码通过工具下载到由FPGA实现的SoC中,那么就可以让SoC执行编写的程序,通过开发板观察程序的运行结果。

安装流程

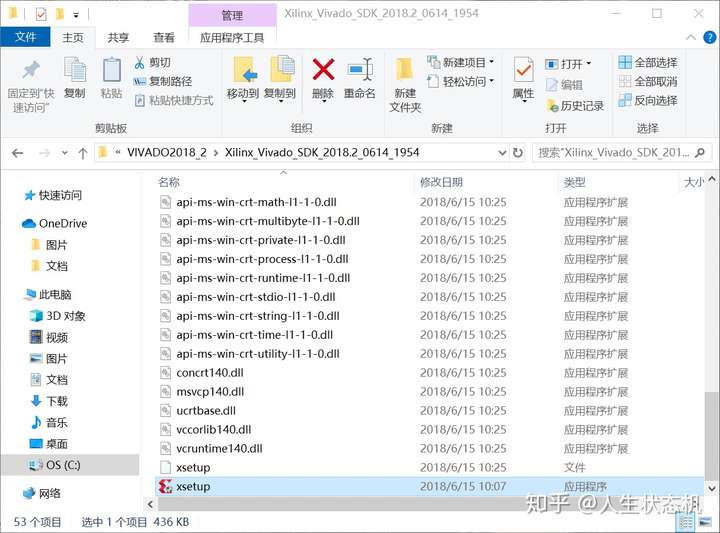

安装流程以vivado 2018.2为例(其他版本安装过程是类似的)。

1.打开下载好的安装包,找到xsetup,双击启动安装过程。

开始安装过程

开始安装过程

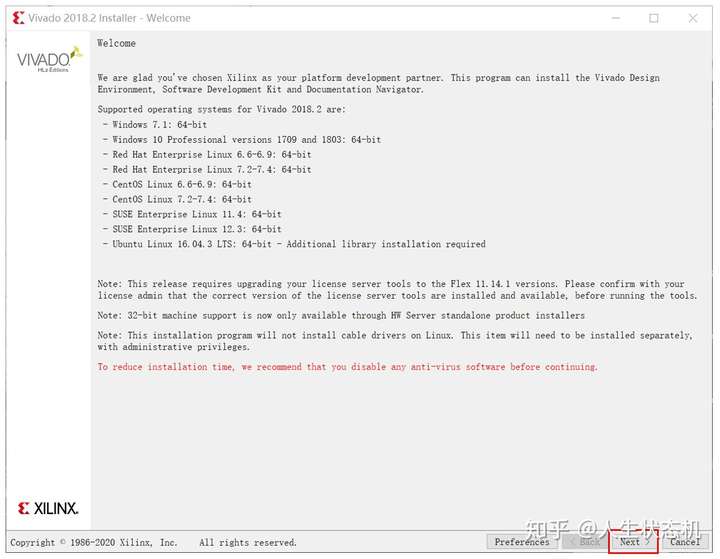

2.Welcome界面直接点击Next跳过。

直接跳过

直接跳过

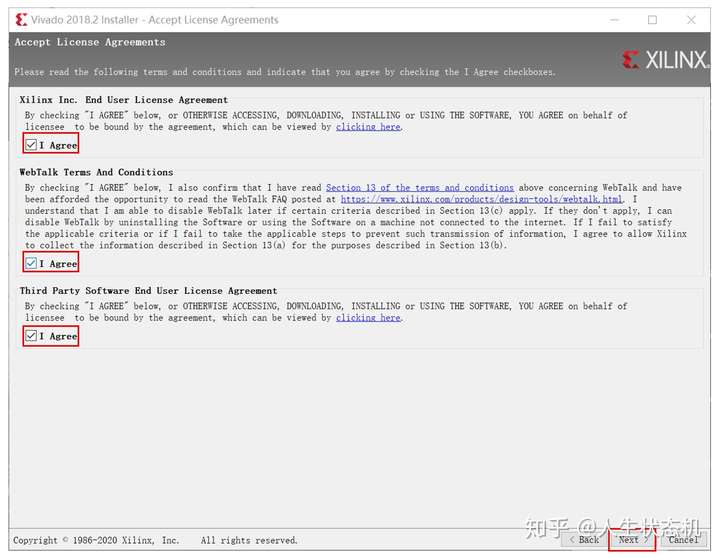

3.相关条款选择“I Agree”,之后点击Next继续。

经典 I Agree

经典 I Agree

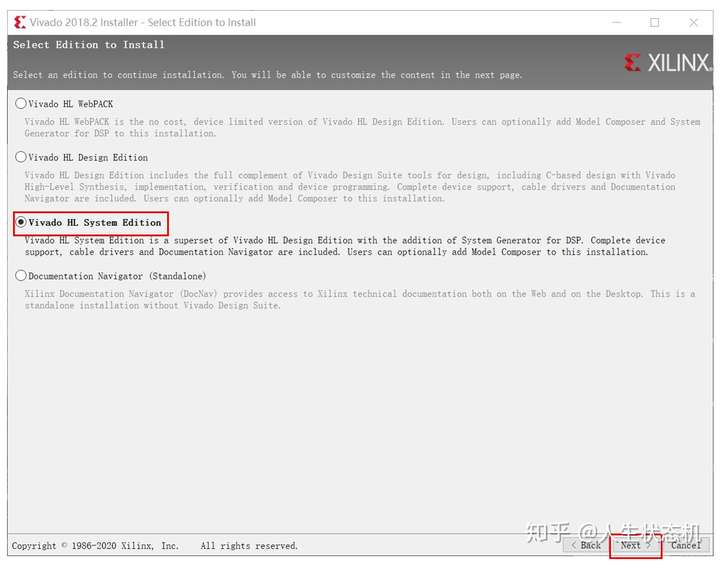

4.选择安装版本时,选择Vivado HL System Edition进行安装。

选择 System Edition

选择 System Edition

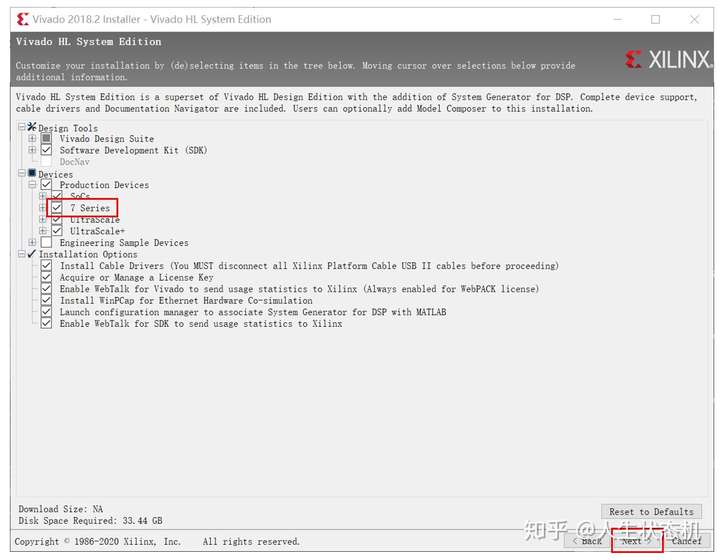

5.这一步将会遇到一些可选的安装选项,在Devices栏下,需要选择7 Series,或者按照默认的选项继续下一步也可以。当然,如果不需要使用其他系列的FPGA的话,也可以把除了7 Series以外的器件前面的勾叉掉,同时为了进一步节约存储空间,也可以选择不安装Design Tools栏下的Software Development Kit(SDK),这样选择的话需要的磁盘空间大约只有12GB。

按需选择需要安装的器件

按需选择需要安装的器件

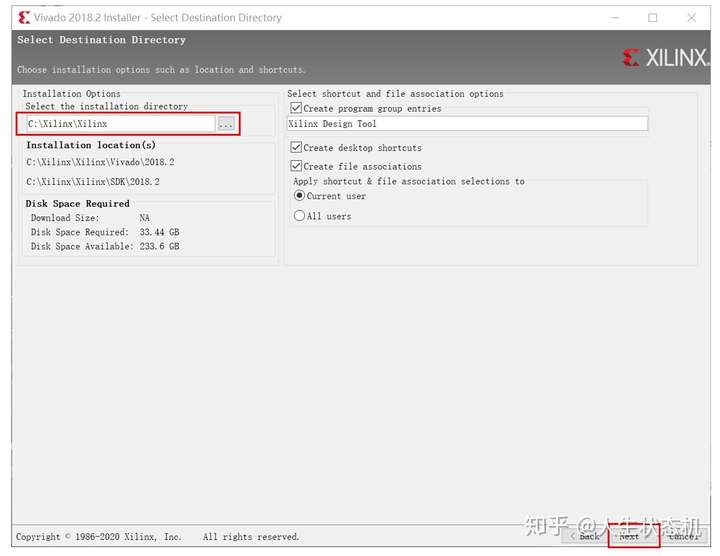

6.选择安装路径,注意路径中不能含有中文,然后确认进入下一步。

选择安装路径

选择安装路径

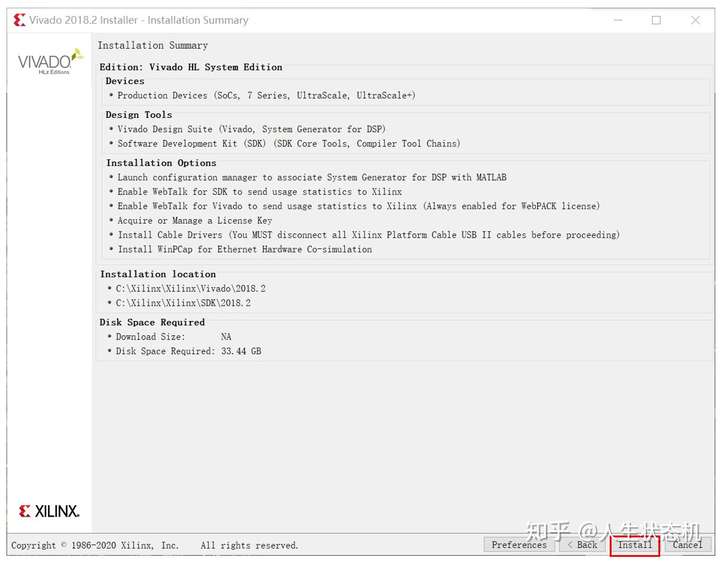

7.最后一步便是确认之前的选择和设置,确认无误后点击Install开始安装。

之后便是一段时间的等待,建议这种时候玩会游戏,负罪感没那么强(不要问我怎么知道的)。

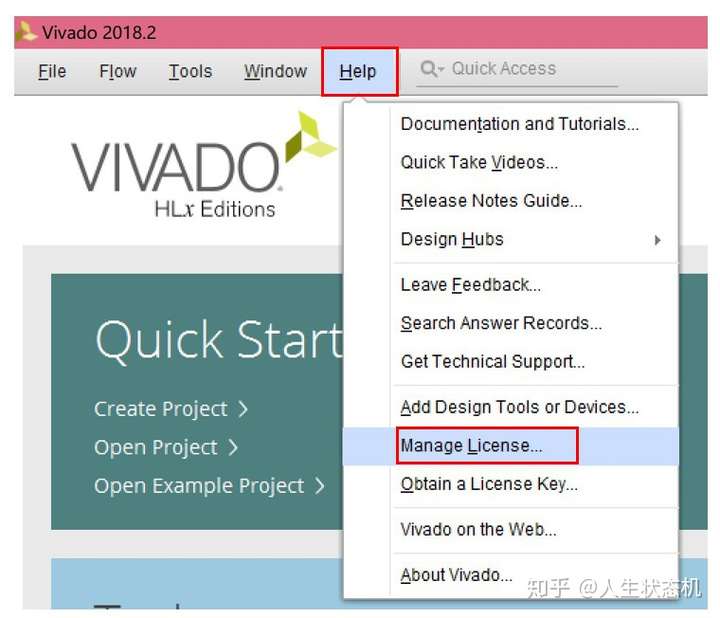

8.安装完成后打开Vivado,在Help菜单栏下选择Manage License打开。

打开License Manager

打开License Manager

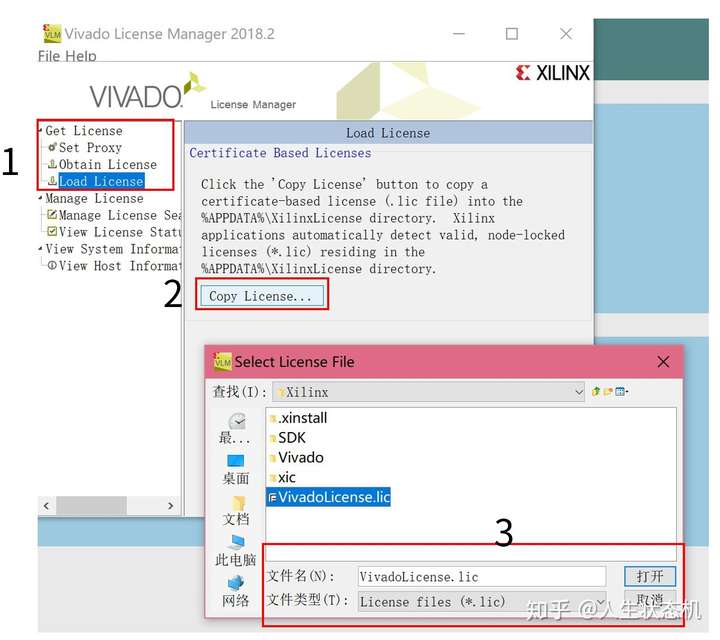

9.在License Manager左侧的Get License栏下选择Load License,然后点击Copy License,在弹出的对话框中选择Lincese文件(VivadoLicense.lic),点击打开。

选择License

选择License

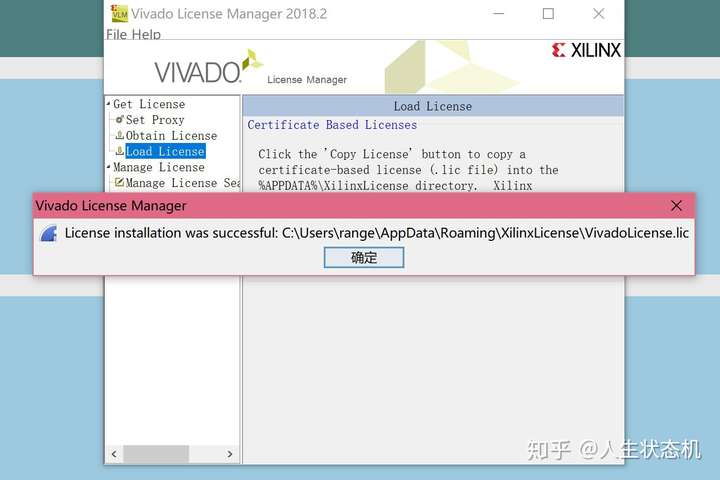

最后显示成功,点击确定即完成安装操作。

Done!

Done!

此处附上安装软件的视频。

新建工程

在软件安装完成后,虽然已经跃跃欲试,但是根据本人刚开始学习时的经(jiao)验(xun),越是心急的时候,越要冷静下来按步骤完成操作,不然可能会弄糟自己学习新东西时愉快的心情。

为了提高学习新工具时的舒适程度,本文以一个简单流水灯的工程为例,介绍从新建工程开始,到下载到板上并观察现象的整个流程。

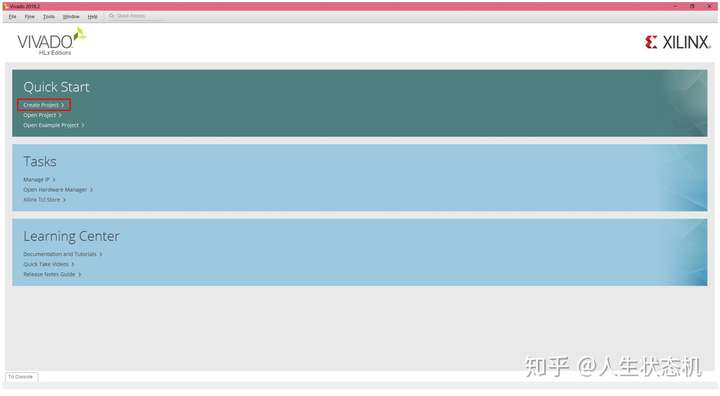

1.首先打开安装好的Vivado软件,可以看到如下界面,在Quick Start一栏里点击Create Project开始创建一个新的工程。

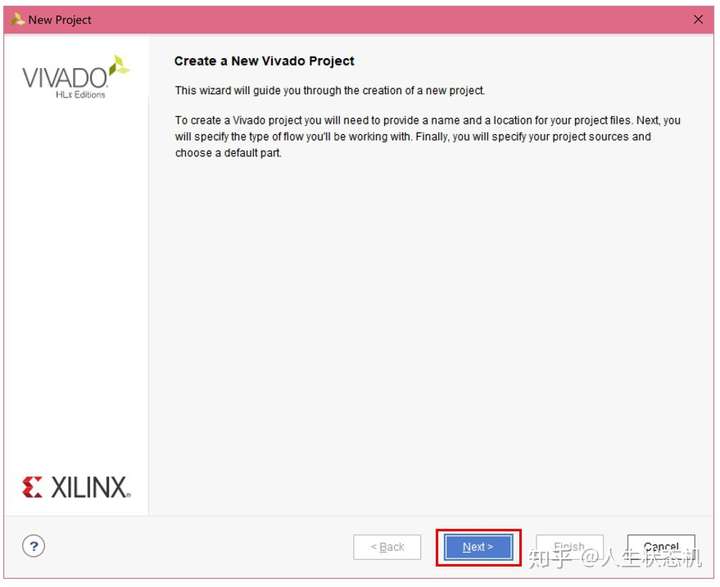

2.第一个界面是介绍界面,直接跳过

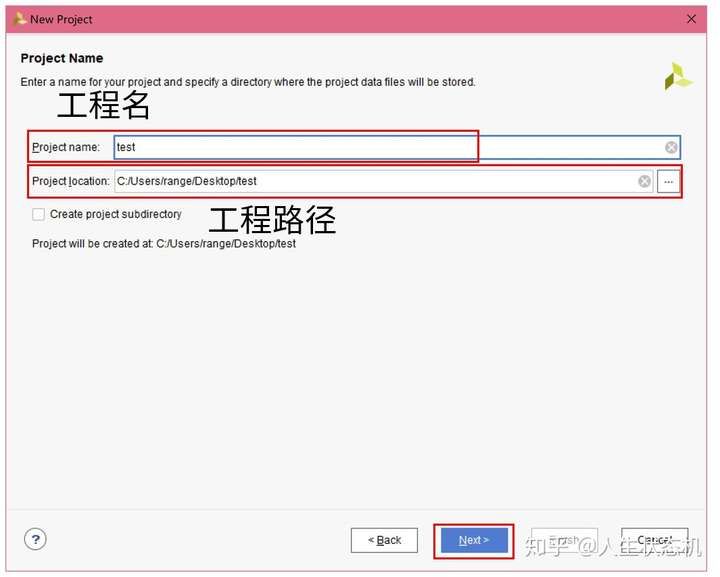

3.设置工程名称及存储路径,注意不能含有中文。

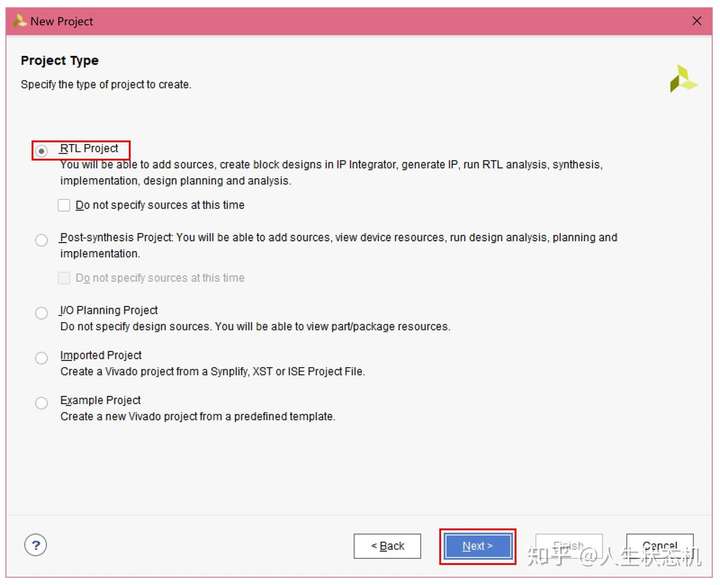

4.选择工程类型时,选择第一项RTL Project,然后继续。

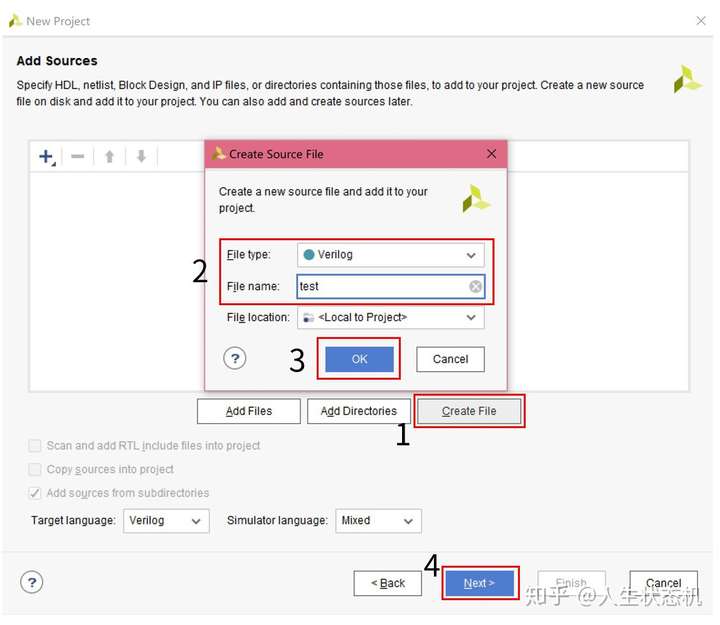

5.添加源文件时点击Create File,在弹出的对话框中选择源文件类型为Verilog文件,输入文件名后点击OK。最后点击Next进入下一步。

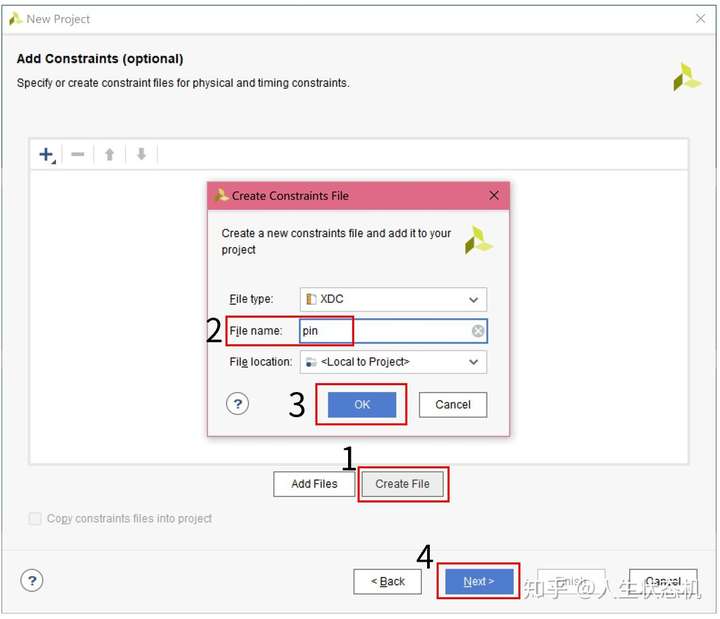

6.添加管脚约束文件时和添加源文件类似,点击Create File,在弹出的对话框中输入文件名后点击OK。最后点击Next进入下一步。

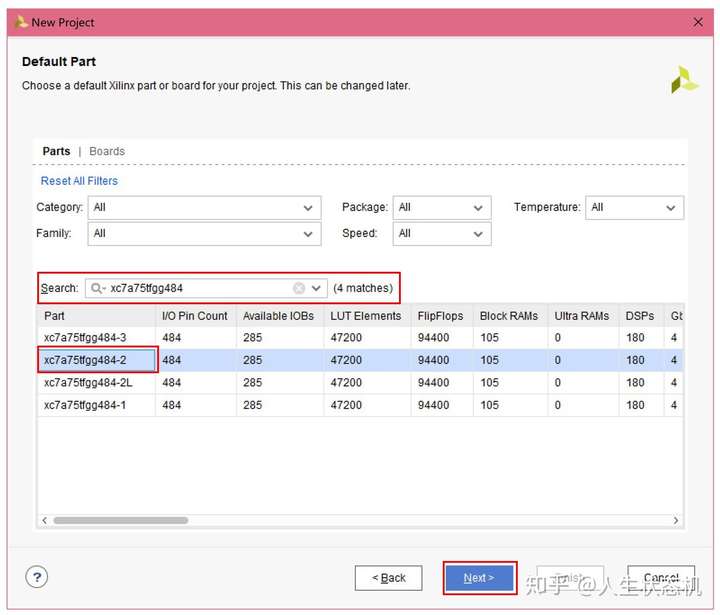

7.选择器件时,在搜索框中输入xc7a75tfgg484,在下方选择xc7a75tfgg484-2一项,然后点击Next进入下一步即可。

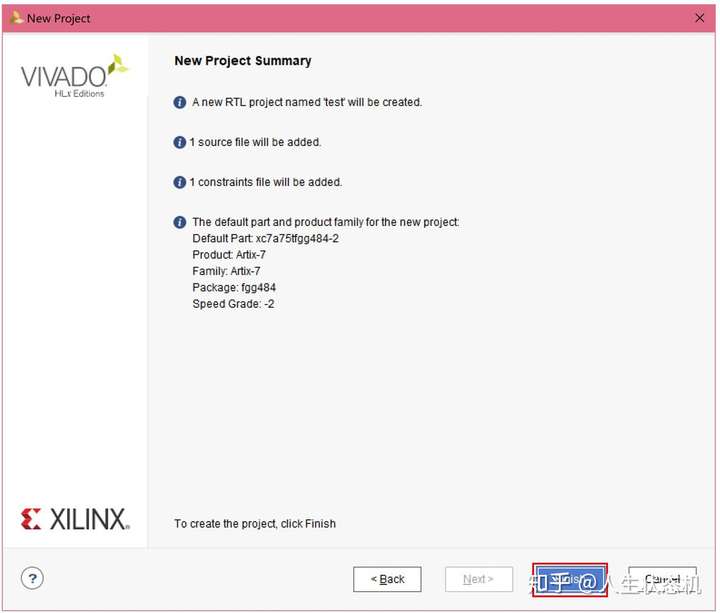

8.最后确认前面所选择的信息都无误后,点击Finish即可完成工程的创建。

Vivado界面介绍

在介绍Vivado的界面前,首先需要说明一下FPGA开发的基本流程,以便更好地掌握工具的使用。

基本流程如下图,首先编写RTL级代码,接着编写TestBench后在Modelsim里观察波形,如果有bug就进行分析修改。在debug结束后,即可在Vivado中新建工程,通过逻辑综合工具得到门级网表,之后进行门级功能验证,同样的,如果有bug就分析修改并重复之前的步骤。Debug结束后可以对模块的端口进行管脚约束,并启动Vivado的布局布线工具,最终可以生成比特流下载到FPGA板上观察现象。

FPGA开发流程

FPGA开发流程

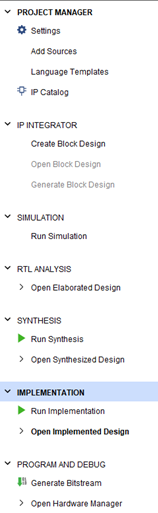

Vivado左侧的侧边栏中有很多功能,其中Project Manager栏下的功能主要用于工程管理,包含工程设置(综合、实现设置,以及一些常规的如编辑器界面设置等),添加文件以及调用IP的入口(IP Catalog)。

Vivado侧边栏

Vivado侧边栏

IP Integrator下的功能主要是用于block design,这种方法可以在框图中添加IP,并将端口连线。Simulation主要用于仿真,但是本人一般选择更轻量级的Modelsim进行仿真,下一篇文章也会详细介绍Modelsim。RTL Analysis提供查看RTL原理图的入口,在Open Elaborated Design下点击Schematic下可以查看。

Synthesis对RTL代码进行综合,将RTL代码转化为网表,RTL代码中如果有语法问题,这一步就会报错,同时,综合工具报告中的warning也是值得注意的,经常会有手误但是能综合通过的情况,所以一定要仔细查看综合报告。完成了综合过程之后,才可以约束管脚。

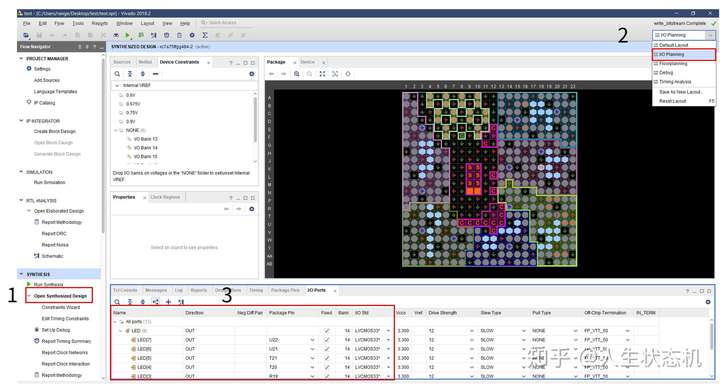

管脚约束主要有2种方式,第一种是可视化的,第二种是编写管脚约束文件。可视化的方式如下图,综合完成后首先在侧边栏中选择Open Synthesis Design,然后在右上角标示处选择IO Planning,最后在下方IO Ports栏下变可以看到信号名及对应的管脚编号(由于已经通过编写管脚约束的方式分配了管脚,所以可以在Package Pin处看到对应的管脚编号)。编写管脚约束文件的方式将在下一节进行介绍。

可视化管脚约束界面

可视化管脚约束界面

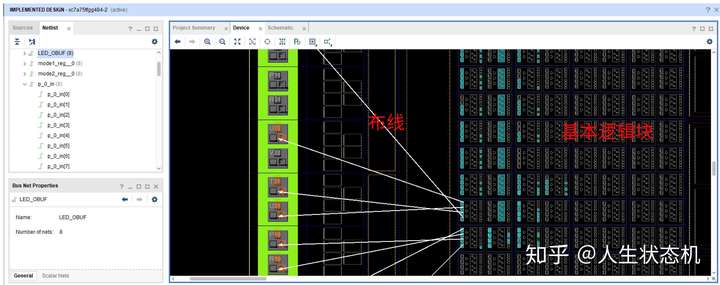

Implementation主要包含布局布线两个过程,布局主要将综合后的基本单元放到FPGA中合适的位置,而布线则是将这些基本单元连接起来。在这一步中也可以检查器件资源是否足够,IO电平设置是否正确。实现完成后点击Open Implementation Design也可以看到布局布线的结果,如下图。

实现界面

实现界面

Program and Debug主要用于下载比特流文件到FPGA板上对FPGA进行配置,调试功能主要结合Vivado的ILA(Integrated Logic Analyzer),调试功能一般在很复杂的设计中才会用到,在工程中遇到了再进行详细的介绍。

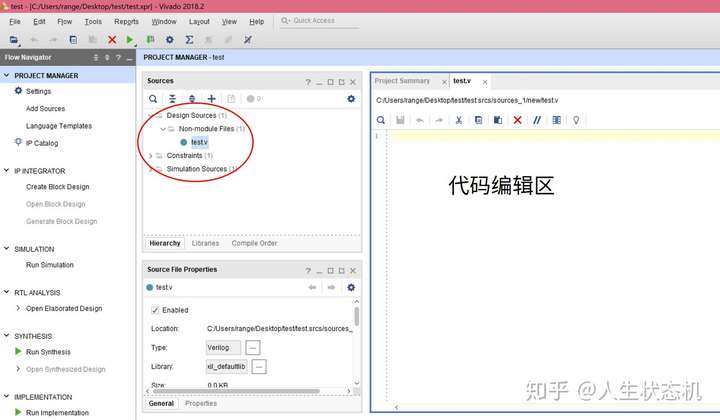

代码编写及生成比特流

在建立好工程之后,接下来便需要编辑RTL代码和管脚约束文件。画红圈的部分为工程文件目录管理,在Design Source栏下存放的便是设计文件,双击test.v,即可在右册代码编辑区中进行编辑。

编辑test.v

编辑test.v

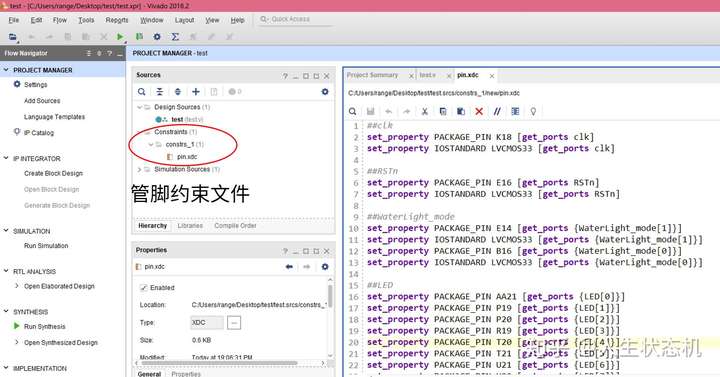

编辑完成test.v并保存后,在Constraints下双击pin.xdc,编辑完成后保存。

编辑pin.xdc

编辑pin.xdc

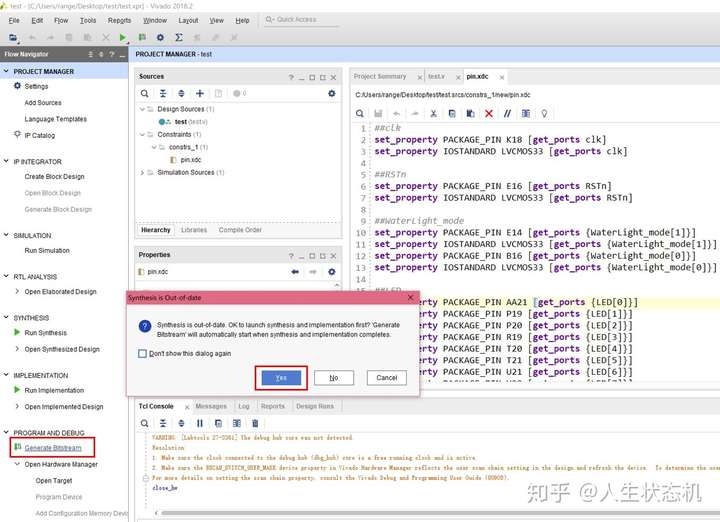

接着在左下角的PROGRAM AND DEBUG一栏下点击Generate Bitstream开始生成比特流,在弹出的对话框中选择Yes即开始。这里生成比特流时会先进行综合和实现过程,综合是把RTL代码生成网表的过程,而实现主要包含布局布线两个过程,布局主要将综合后的基本单元放到FPGA中合适的位置,而布线则是将这些基本单元连接起来,最后生成比特流用于配置FPGA。

生成比特流

生成比特流

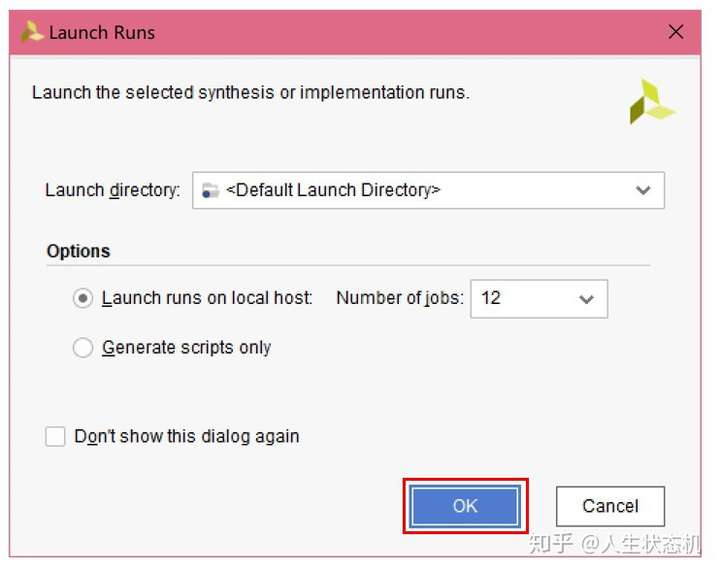

选择启动选项时,保持默认点击OK即可。

默认启动选项

默认启动选项

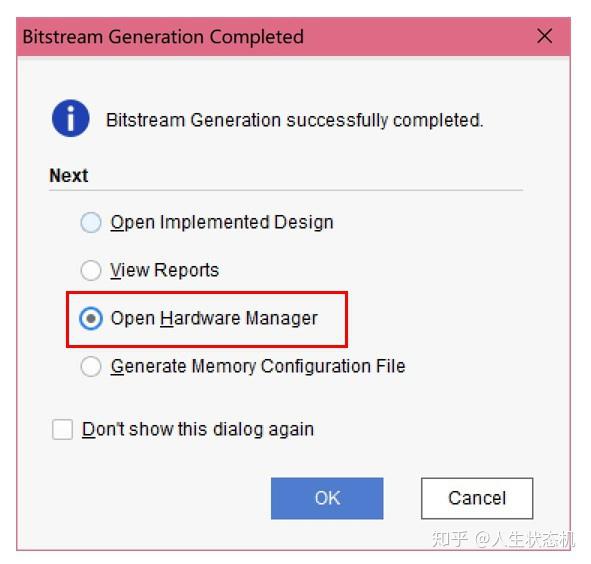

在比特流生成完成时,会弹出如下对话框,选择Open Hardware Manager后点击OK即可完成比特流生成过程,下一步需要将FPGA板与PC连接,以下载比特流到FPGA板并观察。

成功生成比特流后打开Hardware Manager

成功生成比特流后打开Hardware Manager

此处附上新建工程到生成比特流的视频。(注:视频中选择的FPGA芯片型号与文中有所不同,以文中介绍为准)

下载并观察现象

在进行接下来的步骤前,请确保FPGA板已与PC连接。

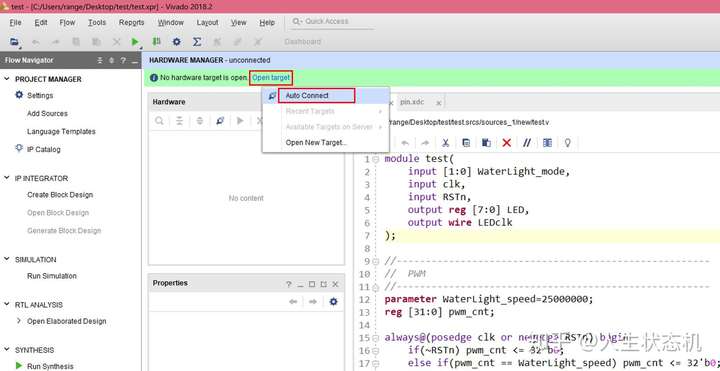

打开Hardware Manager以后,在上方HARDWARE MANAGER处点击Open Target,然后点击Auto Connect。

连接FPGA板

连接FPGA板

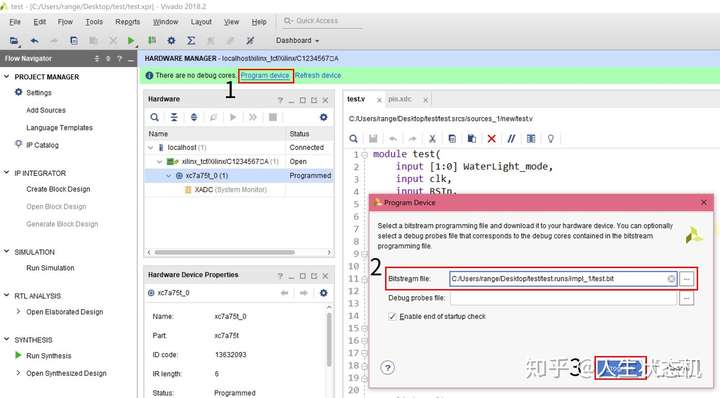

之后在同样的位置点击Program Device,Bitstream File一栏为默认,文件名与工程名相同,后缀为.bit,最后点击Program,完成后即可在FPGA板上观察到现象。

下载比特流到FPGA板

下载比特流到FPGA板

此处附上下载比特流到FPGA板的操作视频。(注:视频中选择的FPGA芯片型号与文中有所不同,以文中介绍为准)

之后便可以在FPGA板上观察到流水灯的现象。