同步FIFO 原理及verilog仿真实现(保姆级)

FIFO可根据读写时钟是否为同一时钟域可分为同步FIFO和异步FIFO,本文主要介绍同步FIFO,异步FIFO将在下篇介绍

1 什么是FIFO

FIFO全称 First In First Out,即先进先出。

FIFO主要用于以下几个方面:

- 跨时钟域数据传输

- 将数据发送到芯片外之前进行缓冲,如发送到DRAM或SRAM

- 存储数据以备后用

FIFO是异步数据传输时常用的存储器,多bit数据异步传输时,无论是从快时钟域到慢时钟域,还是从慢时钟域到快时钟域,都可以使用FIFO处理。

2 重要参数

FIFO中重要的参数有深度、宽度、空标志、满标志、读时钟、读时针、写时钟和写时针

我看到过一个很形象的比喻:

把FIFO比作汽车进入一个单向行驶的隧道,隧道两端都有一个门进行控制,

FIFO宽度就是这个隧道单向有几个车道,FIFO的深度就是一个车道能容纳多少辆车,当隧道内停满车辆时,这就是FIFO的满标志,当隧道内没有一辆车时,这便是空标志

读时钟: 读操作所遵循的时钟,时钟沿到来时读取数据

写时钟: 写操作所遵循的时钟,时钟沿到来时写入数据

读指针: 指向下一个要读出的地址,读完自动加1

写指针: 指向下一个要写入地址,写完自动加1

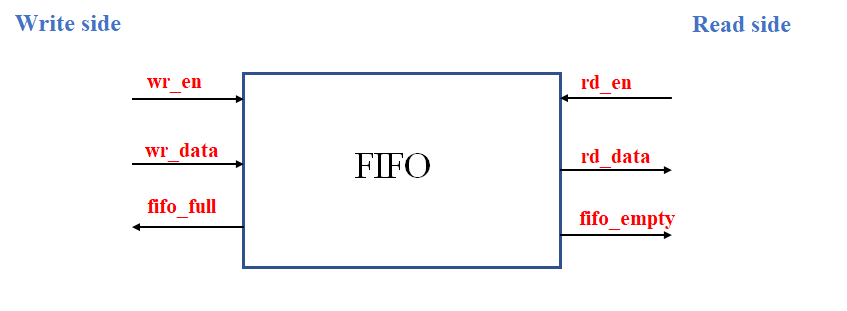

下面从FIFO接口开始说起,下图适用于任何FIFO的基本接口框图

FIFO基本接口

FIFO基本接口

FIFO可分为读数据一端和写数据一端

wr_en和rd_en分别为写/读使能端,就像上面隧道的例子,两个使能端就好像是两边的门,只有门打开的时候才允许车辆进出wr_data和rd_data分别是要写入FIFO的数据和要从FIFO中读取的数据fifo_full和fifo_empty分别为FIFO的满/空标志位

3 FIFO设计的重要原则

- 任何FIFO都不要向满FIFO中写入数据(写溢出)

- 任何FIFO都不要从空FIFO中读取数据(读溢出)

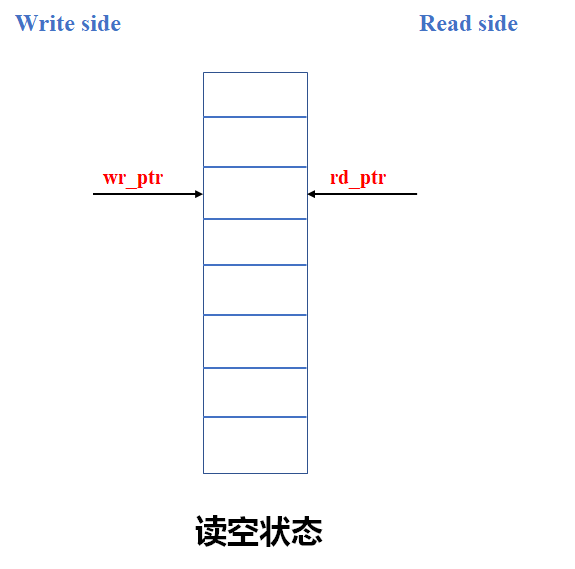

FIFO设计的核心便是空满的判断,如何判断FIFO是否写满(或读空),这里我们可以利用地址指针,如下图:

每写入一次数据,写地址指针会加1,每读取一次数据,读地址指针会加1

就像上图所示,当读地址指针追上写地址指针,FIFO便是读空状态

同理,当写地址指针再次追上读地址指针,FIFO便是写满状态,就像下图

4 同步FIFO设计