异步FIFO 原理及verilog仿真(保姆级)

1 异步FIFO结构

文章转自:

https://baijiahao.baidu.com/s?id=1724030588865450475 感谢老铁!

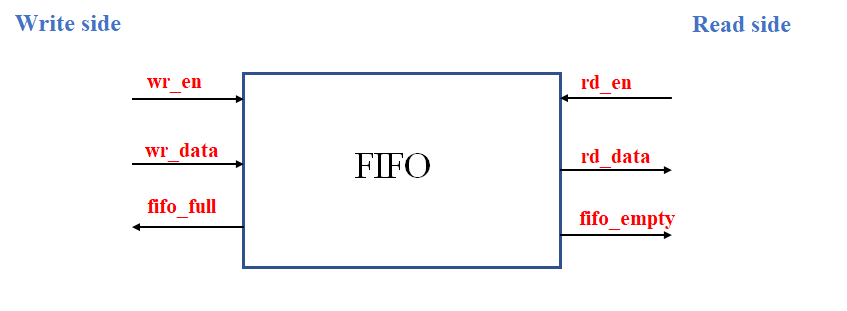

在上篇文章中我们给出了FIFO的基本接口图

并且指出,该图适用于所有的FIFO,这次我们先看看异步FIFO内部的大体框图

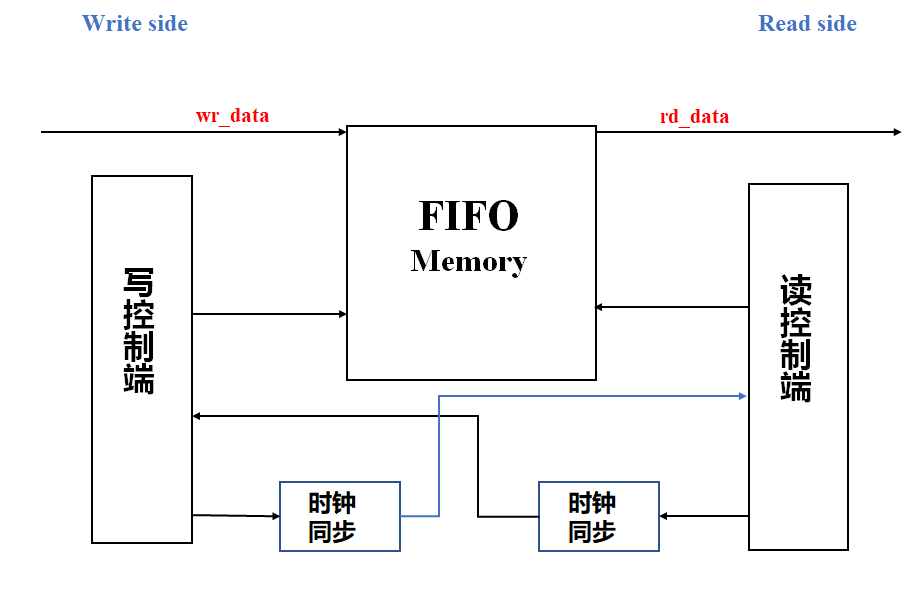

异步FIFO主要由五部分组成:写控制端、读控制端、FIFO Memory和两个时钟同步端

写控制端用于判断是否可以写入数据

读控制端用于判断是否可以读取数据

FIFO Memory用于存储数据

两个时钟同步端用于将读写时钟进行同步处理

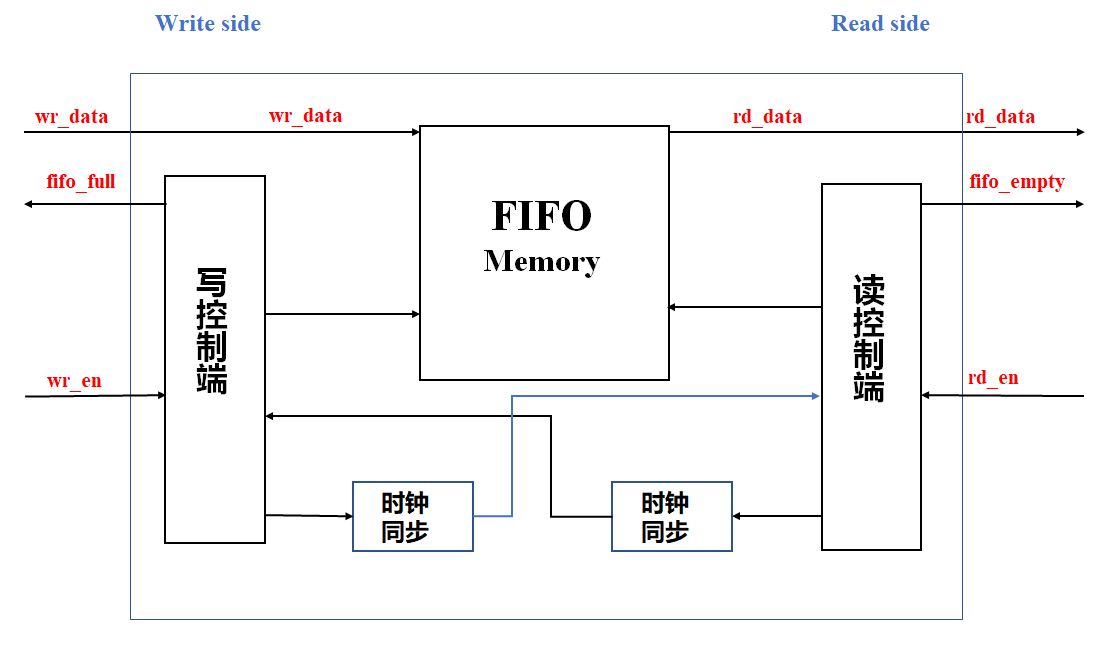

介绍完内部结构,我们在和基本接口图做个联动

刚才说过,读/写控制端用于判断能否写入/读取数据,判断能否写入/读取数据关键在于:

- 写操作时,写使能有效且FIFO未满

- 读操作时,读使能有效且FIFO未空

因此两个使能信号和空满判断信号都连接到控制端上

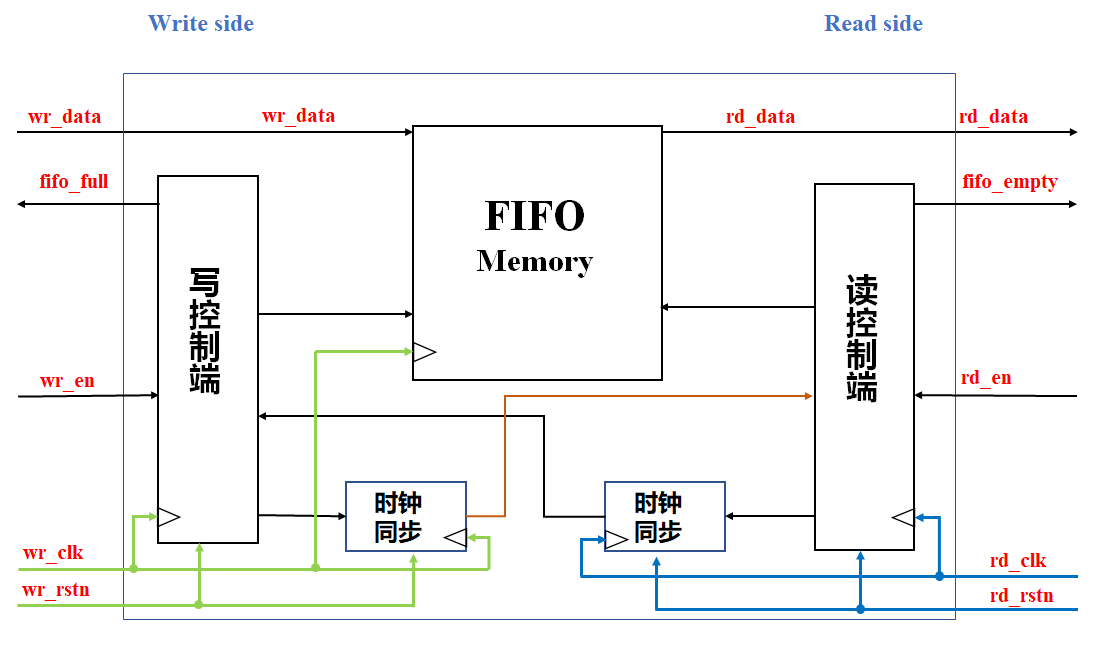

最后我们再加上时钟信号和复位信号

这便是完整的异步FIFO简化框图

2 空满判断

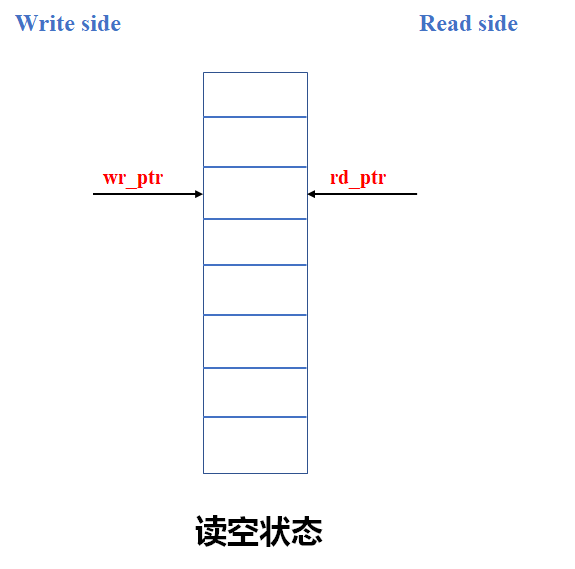

在同步FIFO篇中,我们给出了两个判断空满状态的图

并且也有指出,读空状态可以理解为读地址指针追上写地址指针,写满状态可以理解为写地址指针再次追上读地址指针

在同步FIFO中,因为读写都是在同一个时钟信号下进行的,因此两个地址指针可以直接进行比较

但在异步FIFO中,读写是在不同的时钟信号下进行的,因此在进行比较之前,应当先进行跨时钟与同步

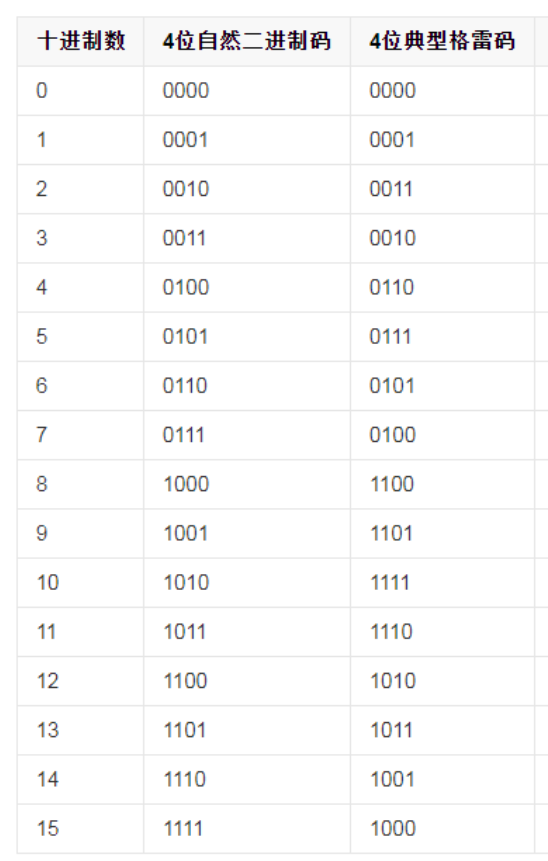

在时钟同步之前,我们应当先将二进制地址转换为格雷码,因为格雷码相邻的两个状态之间,只有1 bit数据发生翻转

下面给出二进制数与格雷码的对照图

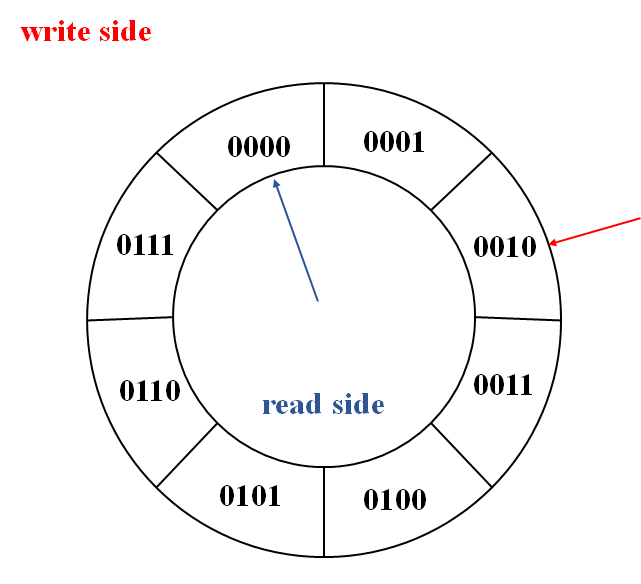

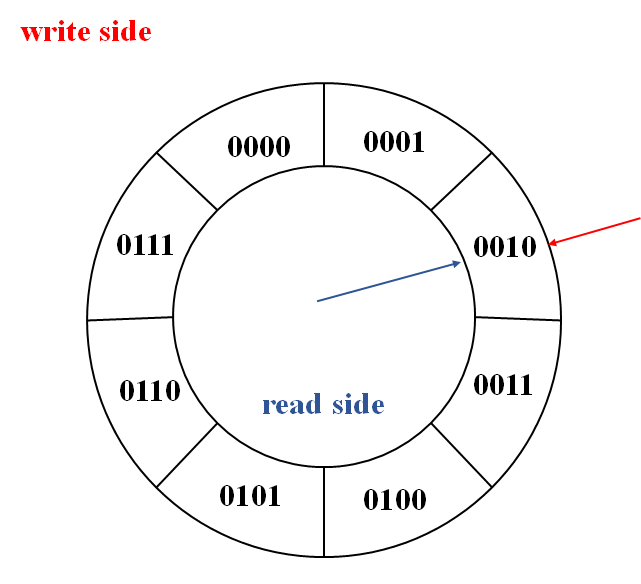

上面也有说到,读指针追上写指针是读空,写指针再次追上读指针是写满,为了便于理解,我们做一个环形图

假设内圈为读,外圈为写,读空时是读写指针应当指向同一个地址,就像这样

此时,读地址应当和写地址完全相同,就以0010为例,0010的格雷码为0011,可以看出对于读空状态,无论是二进制还是格雷码均是所有位都相同

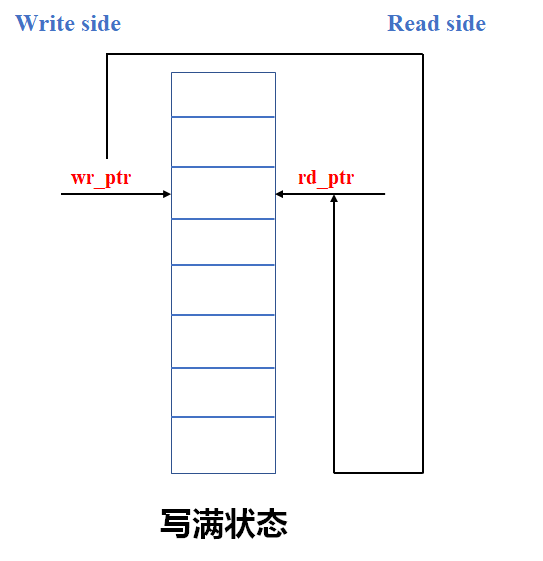

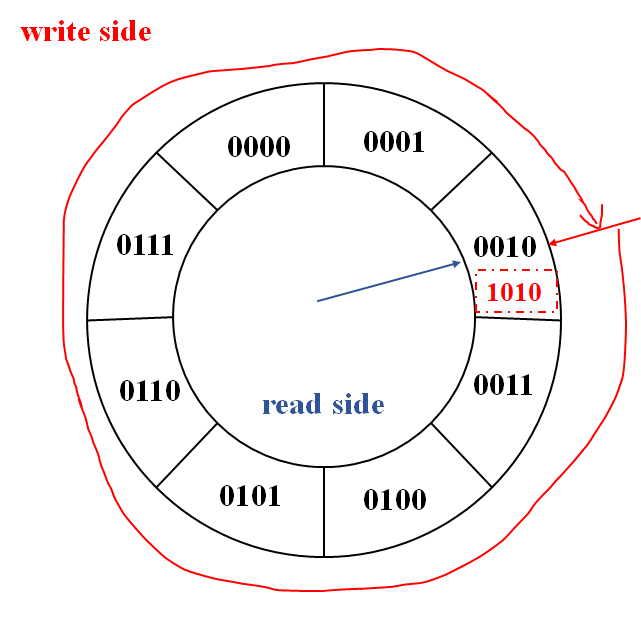

写满和读空略有不同,应当是下面这样

细心的小伙伴应该可以发现,上面在提到写满时,说的是写指针再次追上读指针,也就是说,写满时,写指针比读指针多走一圈,为了便于区分,将地址位宽从3 bit拓宽到4 bit,因此此时的写指针地址可以认为是1010

1010的格雷码是1111, 0010的格雷码是0011,对比两个格雷码是不是可以发现,此时高两位相反,低两位相同,这便是格雷码下写满的判断条件

Verilog中表示为

//写满判断

always @ (posedge wr_clk or negedge wr_rstn) begin

if(!wr_rstn)

fifo_full <= 0;

else if((wr_ptr_g[$clog2(DEPTH)] != rd_ptr_grr[$clog2(DEPTH)]) && (wr_ptr_g[$clog2(DEPTH) - 1] != rd_ptr_grr[$clog2(DEPTH) - 1]) && (wr_ptr_g[$clog2(DEPTH) - 2 : 0] == rd_ptr_grr[$clog2(DEPTH) - 2 : 0]))

fifo_full <= 1;

else

fifo_full <= 0;

end

//读空判断

always @ (posedge rd_clk or negedge rd_rstn) begin

if(!rd_rstn)

fifo_empty <= 0;

else if(wr_ptr_grr[$clog2(DEPTH) : 0] == rd_ptr_g[$clog2(DEPTH) : 0])

fifo_empty <= 1;

else

fifo_empty <= 0;

end

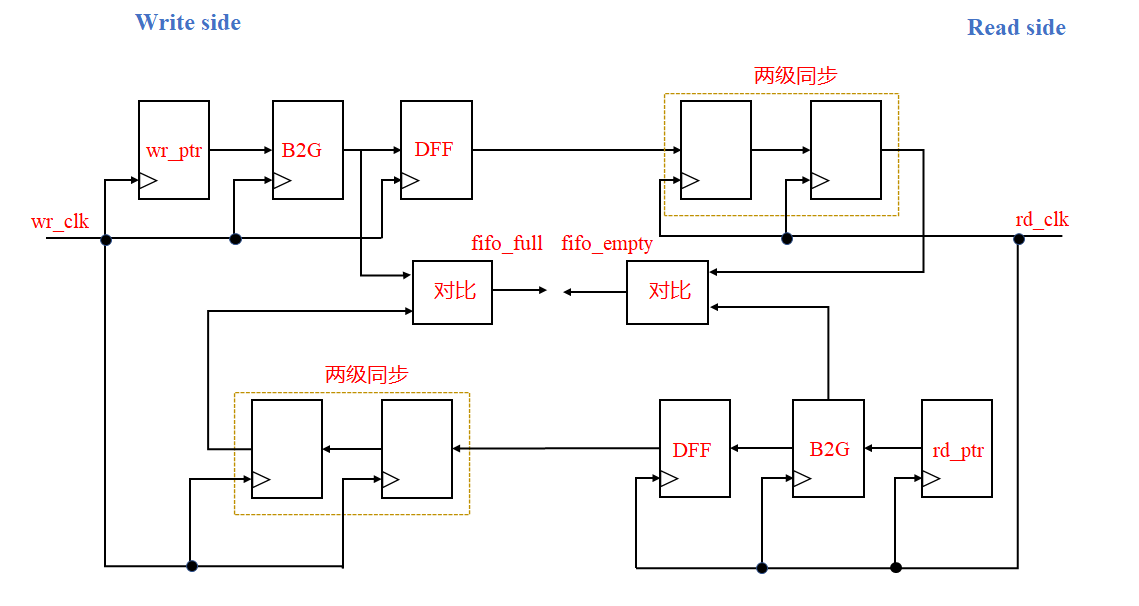

3 时钟同步

在同步FIFO设计中,因为读写指针在同一个时钟下,因此可以直接进行比较

但在异步FIFO中,由于读写指针在不同的时钟下,因此需要将两个地址指针进行时钟同步操作

在异步FIFO中,常用的同步方法是两级同步打拍延迟,同步地址指针的大致过程如下:

写操作时,先将写地址指针转换成格雷码,然后通过两级同步(两级同步在读时钟下进行),将写地址指针同步到读时钟域下;读操作类似

根据这个过程图,也可以看出空满判断的方式:

- 写满在写时钟下判断,将写地址指针的格雷码与同步过来的读地址指针格雷码进行比较,符合写满条件,即FIFO

虚满 - 读空在读时钟下判断,将读地址指针的格雷码与同步过来的写地址指针格雷码进行比较,符合读空条件,即FIFO

虚空

留意下,这里我说的是虚空/满,并不是输入错误哟,具体解释我放在文章最后,爱思考的朋友现在可以思考一下原因

下面给出时钟同步的Verilog代码

assign wr_ptr_g = wr_ptr ^ (wr_ptr >> 1); //B2G

assign rd_ptr_g = rd_ptr ^ (rd_ptr >> 1);

//写指针同步到读时钟域

always @ (posedge rd_clk or negedge rd_rstn) begin

if(!rd_rstn) begin

wr_ptr_gr <= 0;

wr_ptr_grr <= 0;

end

else begin

wr_ptr_gr <= wr_ptr_g;

wr_ptr_grr <= wr_ptr_gr;

end

end

//读指针同步到写时钟域

always @ (posedge wr_clk or negedge wr_rstn) begin

if(!wr_rstn) begin

rd_ptr_gr <= 0;

rd_ptr_grr <= 0;

end

else begin

rd_ptr_gr <= rd_ptr_g;

rd_ptr_grr <= rd_ptr_gr;

end

end

4 异步FIFO设计

下面给出整体Verilog代码

module asy_fifo#(

parameter WIDTH = 8,

parameter DEPTH = 8

)(

input [WIDTH - 1 : 0] wr_data,

input wr_clk,

input wr_rstn,

input wr_en,

input rd_clk,

input rd_rstn,

input rd_en,

output fifo_full,

output fifo_empty,

output [WIDTH - 1 : 0] rd_data

);

//定义读写指针

reg [$clog2(DEPTH) : 0] wr_ptr, rd_ptr;

//定义一个宽度为WIDTH,深度为DEPTH的fifo

reg [WIDTH - 1 : 0] fifo [DEPTH - 1 : 0];

//定义读数据

reg [WIDTH - 1 : 0] rd_data;

//写操作

always @ (posedge wr_clk or negedge wr_rstn) begin

if(!wr_rstn)

wr_ptr <= 0;

else if(wr_en && !fifo_full) begin

fifo[wr_ptr] <= wr_data;

wr_ptr <= wr_ptr + 1;

end

else

wr_ptr <= wr_ptr;

end

//读操作

always @ (posedge rd_clk or negedge rd_rstn) begin

if(!rd_rstn) begin

rd_ptr <= 0;

rd_data <= 0;

end

else if(rd_en && !fifo_empty) begin

rd_data <= fifo[rd_ptr];

rd_ptr <= rd_ptr + 1;

end

else

rd_ptr <= rd_ptr;

end

//定义读写指针格雷码

wire [$clog2(DEPTH) : 0] wr_ptr_g;

wire [$clog2(DEPTH) : 0] rd_ptr_g;

//读写指针转换成格雷码

assign wr_ptr_g = wr_ptr ^ (wr_ptr >>> 1);

assign rd_ptr_g = rd_ptr ^ (rd_ptr >>> 1);

//定义打拍延迟格雷码

reg [$clog2(DEPTH) : 0] wr_ptr_gr, wr_ptr_grr;

reg [$clog2(DEPTH) : 0] rd_ptr_gr, rd_ptr_grr;

//写指针同步到读时钟域

always @ (posedge rd_clk or negedge rd_rstn) begin

if(!rd_rstn) begin

wr_ptr_gr <= 0;

wr_ptr_grr <= 0;

end

else begin

wr_ptr_gr <= wr_ptr_g;

wr_ptr_grr <= wr_ptr_gr;

end

end

//读指针同步到写时钟域

always @ (posedge wr_clk or negedge wr_rstn) begin

if(!wr_rstn) begin

rd_ptr_gr <= 0;

rd_ptr_grr <= 0;

end

else begin

rd_ptr_gr <= rd_ptr_g;

rd_ptr_grr <= rd_ptr_gr;

end

end

//声明空满信号数据类型

reg fifo_full;

reg fifo_empty;

//写满判断

always @ (posedge wr_clk or negedge wr_rstn) begin

if(!wr_rstn)

fifo_full <= 0;

else if((wr_ptr_g[$clog2(DEPTH)] != rd_ptr_grr[$clog2(DEPTH)]) && (wr_ptr_g[$clog2(DEPTH) - 1] != rd_ptr_grr[$clog2(DEPTH) - 1]) && (wr_ptr_g[$clog2(DEPTH) - 2 : 0] == rd_ptr_grr[$clog2(DEPTH) - 2 : 0]))

fifo_full <= 1;

else

fifo_full <= 0;

end

//读空判断

always @ (posedge rd_clk or negedge rd_rstn) begin

if(!rd_rstn)

fifo_empty <= 0;

else if(wr_ptr_grr[$clog2(DEPTH) : 0] == rd_ptr_g[$clog2(DEPTH) : 0])

fifo_empty <= 1;

else

fifo_empty <= 0;

end

endmodule

下面是tb

module asy_fifo_tb;

parameter width = 8;

parameter depth = 8;

reg wr_clk, wr_en, wr_rstn;

reg rd_clk, rd_en, rd_rstn;

reg [width - 1 : 0] wr_data;

wire fifo_full, fifo_empty;

wire [width - 1 : 0] rd_data;

//实例化

asy_fifo myfifo (

.wr_clk(wr_clk),

.rd_clk(rd_clk),

.wr_rstn(wr_rstn),

.rd_rstn(rd_rstn),

.wr_en(wr_en),

.rd_en(rd_en),

.wr_data(wr_data),

.rd_data(rd_data),

.fifo_empty(fifo_empty),

.fifo_full(fifo_full)

);

//时钟

initial begin

rd_clk = 0;

forever #25 rd_clk = ~rd_clk;

end

initial begin

wr_clk = 0;

forever #30 wr_clk = ~wr_clk;

end

//波形显示

initial begin

$fsdbDumpfile("wave.fsdb");

$fsdbDumpvars(0, myfifo);

$fsdbDumpon();

end

//赋值

initial begin

wr_en = 0;

rd_en = 0;

wr_rstn = 1;

rd_rstn = 1;

#10;

wr_rstn = 0;

rd_rstn = 0;

#20;

wr_rstn = 1;

rd_rstn = 1;

@(negedge wr_clk)

wr_data = {$random}%30;

wr_en = 1;

repeat(7) begin

@(negedge wr_clk)

wr_data = {$random}%30;

end

@(negedge wr_clk)

wr_en = 0;

@(negedge rd_clk)

rd_en = 1;

repeat(7) begin

@(negedge rd_clk);

end

@(negedge rd_clk)

rd_en = 0;

#150;

@(negedge wr_clk)

wr_en = 1;

wr_data = {$random}%30;

repeat(15) begin

@(negedge wr_clk)

wr_data = {$random}%30;

end

@(negedge wr_clk)

wr_en = 0;

#50;

$finish;

end

endmodule

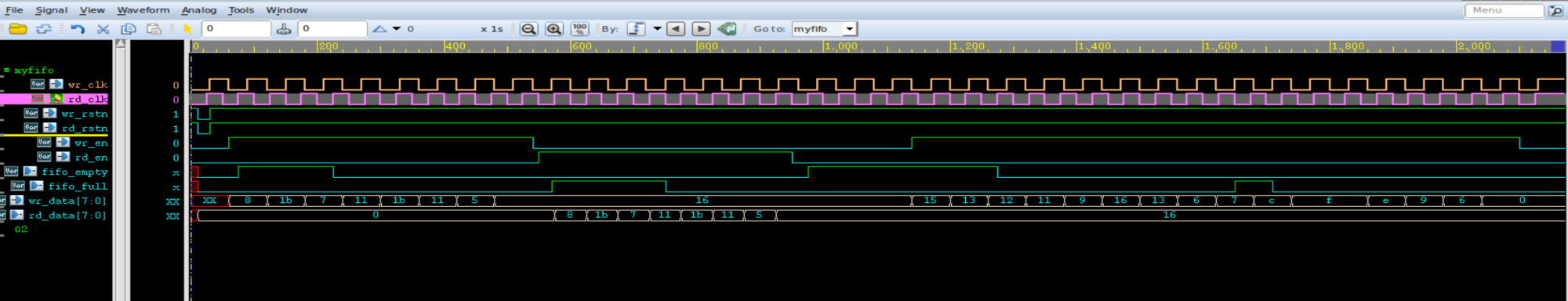

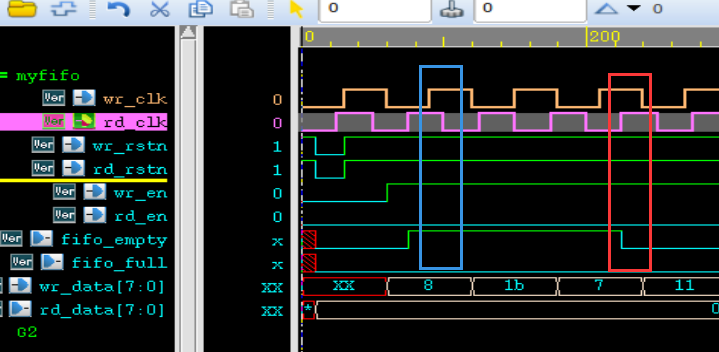

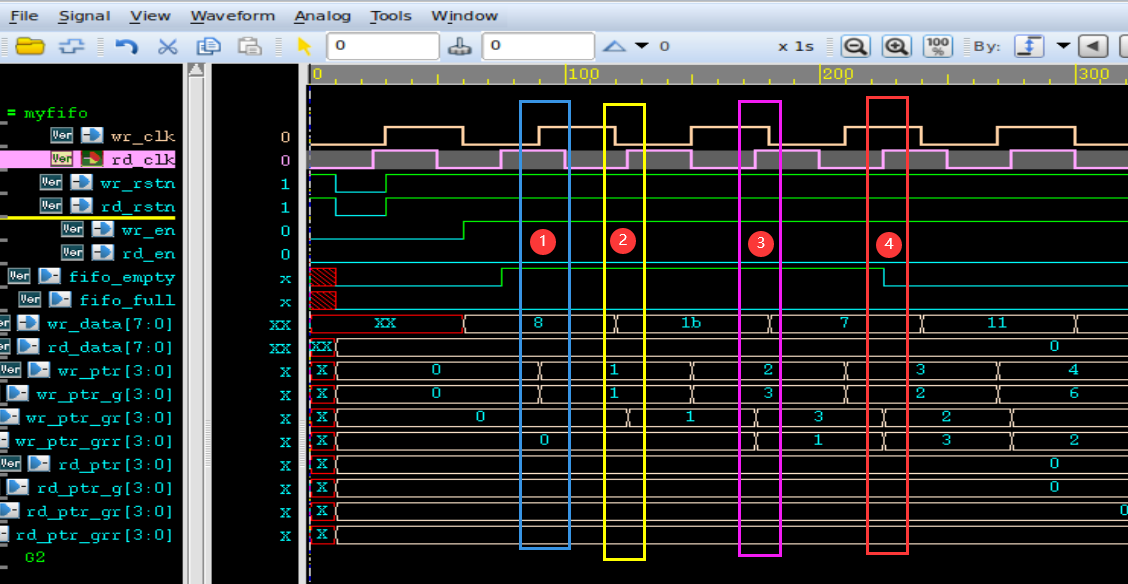

下面贴上运行结果

这里有一点需要说明

蓝色框的位置,已经开始写入数据,但fifo_empty信号并没有被拉低,而是在第三个rd_clk上升沿被拉低,这是因为在判断FIFO是否读空时,是在读时钟下判断,并且,进行判断时,写地址格雷码需要在读时钟域进行两次同步,最后进行比较

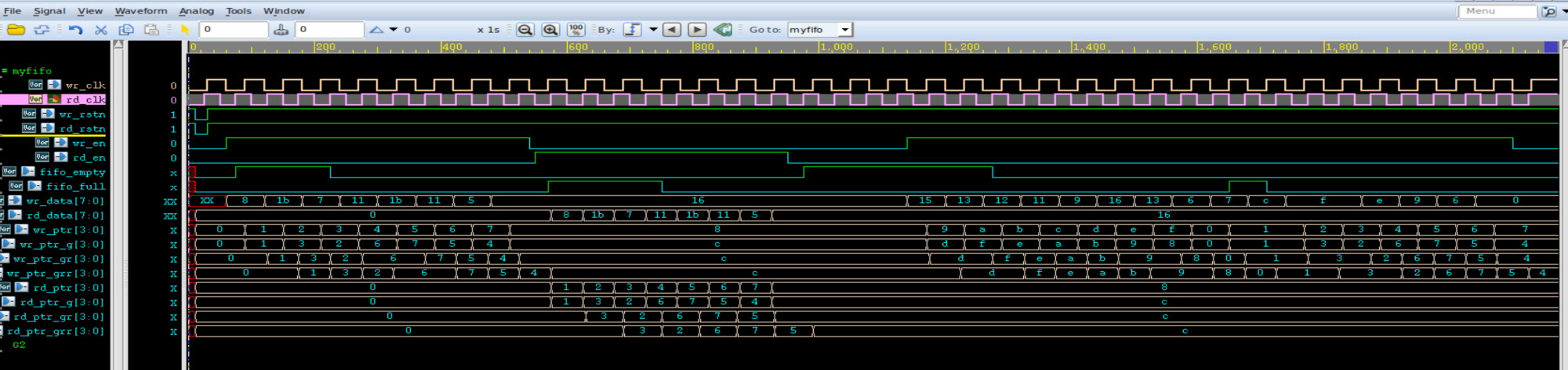

为了更清晰的解释,可以将所有的地址指针也加入到波形图中

注意刚才提到的位置

在位置1,有数据写入,此时wr_ptr和wr_ptr_g都发生了变化,wr_ptr_gr和wr_ptr_grr保持不变

在位置2,wr_ptr_gr变化,wr_ptr_grr保持不变

在位置3,wr_ptr_grr才开始发生变化

在位置4,wr_ptr_grr和rd_ptr_g进行比较,判定此时FIFO非空

还有一个有意思的地方

注意wr_ptr_gr和wr_ptr_grr,这两个保持了两个rd_clk时钟周期,返回查看完整波形图的话,这种情况只出现在写指针的格雷码

这tb文件中,我们设定的是,rd_clk比wr_clk快,打两拍同步的方式,慢时钟域同步到快时钟域和快时钟域同步到慢时钟域处理方式是不同的,后面有时间再做介绍。

有兴趣的小伙伴,可以试下如果rd_clk比wr_clk慢,这种情况会出现在rd_ptr_gr和rd_ptr_grr

5 一个我在面试中被问到的问题

我在面试的时候被问到,如果跨时钟域同步时,同步过来的是一个亚稳态的数据,那么FIFO还能否正常工作?

在空满判断部分说过,读空或写满可以理解为:

- 读空时:可以理解为是读指针在追写指针

- 写满时:可以理解为是写指针在追读指针

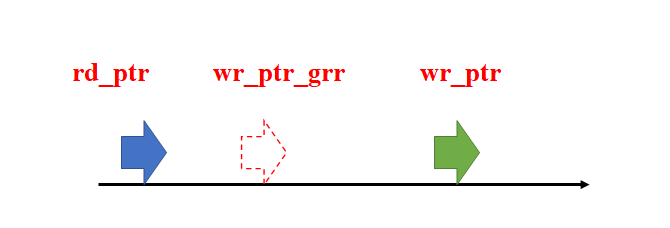

为了方便理解,我们将其抽象成一个追逐运动,以读空为例

先确定读空的判断,读空判断是在rd_clk下,读指针的格雷码与写指针同步过来的格雷码进行比较,实际上,读指针追的是wr_ptr_grr

而wr_ptr_grr又是写指针留在原地的残影(写指针经过两个读时钟周期后得来的),在两个读时钟周期的这段时间,写指针可能会原地不动,也可能继续前行,这便是虚空的概念

虚满的概念同理

疑问1:进行数据空满的对比时,读写时钟域都有读写指针,此时应该怎么对比?为什么?

另外一篇博客中有这样的话:

同步rd_cntr至clk_write时钟域,再与wr_cntr进行对比来决定FIFO是否满;(判断满是wr_cntr - rd_cntr)

同步wr_cntr至clk_read时钟域,再与rd_cntr进行对比来决定FIFO是否空;(判断空是rd_cntr == wr_cntr)

这是结论,那现在我们必须要仔细的思考这句话为什么是这么做的。

首先画个示意图。

那现在我们来设想各种情况下会发生什么,在此我们暂时不考虑亚稳态的事情,认为信号通过同步模块都被采到了但是会有信号丢失。

第一种情况我们假定写时钟特别快,读时钟都采不齐写指针。

那么此时空逻辑会不会出错呢?假设写指针已经跑了1 2 3 4 5 6 7 8 9,而读时钟采到了1 2 6 8;那么如果此时读指针就在8,两边一对比发现一样(当然了这只是假设的一种情况)则会报“空”!那么实际空没空呢,没有因为我写到9了写进去了一个数,不过没关系之后必然会采到9(或者采到10一类的),状态会很快恢复正常,或者说没有空而报了空我们还可以接受,因为这样对于一个将要空的FIFO会停止读数旋即恢复正常,不会使其数据发生紊乱。那会不会有空了而报不空使得读出数据出现问题的情况呢?不会的,你想想看写指针跑的比你采样的快,是趋向与“不空”(越写数据越多嘛)的,因此不会出现这样的错误。

读指针被同步到写时钟域本身不会出现漏采的情况,因此“满”逻辑的判断不会出现问题。

第二种情况我们假定读时钟域特别快,写时钟都采不齐读指针。

此时的满逻辑会出错么?我们来看下。我们同样假设读指针从1跑到了9,而只被采样到了7。如果此时写指针也写到了7,那么二者一比较发现写“满”了,实际呢没有满,不过此时也会停止外部写入(传出了满的信号),这是不会对FIFO中的数据产生影响的,并且很快会恢复到“不满”。如果此时写指针到了5,那么二者对比会得出“不满”的逻辑传出,真实情况呢同样是不满,因为读到7就已经不满了真实情况读到了9自然更加“不满”。这样就解释清楚了。

写指针被同步到读时钟域本身不会出现漏采的情况,因此“空”逻辑的判断不会出现问题。

受到HR的点播或许我们可以选择一种记法:

“满”逻辑是要给谁的——给写信号告诉他你别写了——那么写指针能多跑出去么?跑多了不就把数据覆盖了!——所以必须在写时钟域进行对比;

“空”逻辑是要给谁的——给读信号告诉他你别读了——那么读指针能多跑出去么?跑多了不就读出来错误的数了!——所以在读时钟域进行对比;

我现在先理解到这一步吧。

疑问2:为什么要用格雷码进行同步传输?

我觉得使用格雷码的优势体现在读写时钟差异不是特别大的时候,不能一个是1000M一个是10M那谁也救不了了,无限加长FIFO深度吧。那么我们假定读写时钟频率差异没有过大,例如一个133M一个100M这样的。

我们要知道这个异步时钟采样,再不经过特殊处理的情况下采错了是在所难免的。单个信号可能采错或者没采到,那多个信号的读写指针就更加有可能出问题了。我们来看下如果此时的指针是1011(二进制=2),那么在向1100(2)跳变时候,由于信号走的距离不一样啦触发事件或者逻辑门延时不同啦等等原因,在另外一段时钟域就可能采出多种情况例如1011(2)、1110(2)、1101(2)等,总之每个信号都可能是正确值或者未跳变时候的值。那么在得到“空”“满”逻辑时候很大可能概率会出错,这个我们不能忍。过程如下图所示。

所以说我们就要选择格雷码了,来看下格雷码发生了什么事。1011(2)=1110(g),1100(2)=1010(g),因此格雷码跳变为1110(g)->1010(g)。同样考虑采样出问题了,由于我们提前说好了读写时钟频率差距不是太大,因此采样可能得到两种情况:1110(g)和1010(g),到另外的时钟域后会转换为二进制的1011(2)和1100(2)。看到这里是不是想到了什么!你看如果得到的是1100那没问题呀,这就是真是的值。如果是得到1011呢?我实际跑到了1100你采到了1011是不是类似于上一个问题的“指针实际已经跑到了9而你只采到了7,会不会出问题”,答案是不会呀!原因就在于我们进行对比时时钟域的选择已经解决了这个问题。因此可知使用格雷码即时出现了采样错误的情况,也不会时“空满”判定出现问题。

判断满的方法是拿write_pointer和做完CDC转换过来的read_pointer作比较。CDC转换的方法是采用格雷码过两级flip-flop的同步器。由于read_pointer属于100M的频率, write时钟域有500M,属于快采慢,CDC转换不会有什么问题。因此满的判断不会有问题。 判断空的方法是拿read_pointer和做完CDC转换过来的write_pointer做比较。CDC转换的方法也是采用格雷码过两级flip-flop的同步器。由于write_pointer的变化频率是 500M,而read时钟域只有100M的clk,属于慢采快,CDC的转换就会出问题。 因为read时钟的频率过低,所以write_pointer做完CDC之后得到的将是零星的离散的采样值,而非连续的值,比如说可能会采样到格雷码的5->10->15,而非连续的格雷码的5->6->7->8............ 那么该怎么解决这个问题? 因为快时钟往慢时钟传数据,要想一个不漏,唯一的办法就是hold住(通常来讲,至少hold住目标时钟域2T)。把当前数据牢牢保持住,等到数据被取走了再传下一个。但是很明显write_pointer属于自增型的,只要fifo没有满,它都可以持续增加,并不会hold不变,所以必然会漏采。 为什么不需要解决? 因为只要fifo够大,即便读到的write_pointer是离散的,也不会影响到fifo判空。只要fifo判空不出错,异步fifo的行为就没有问题,只不过效率可能略微降低。 举个栗子: 当read时钟域采样到write_pointer的值是5的时候,真正的write_pointer的值可能是多少?可能已经是5,6,7,8,9等等了。但绝对不可能比5小。 为什么不可能比5小? 因为对于write_pointer而言,它从4变到5,这个沿变在跨CDC的时候,只有没采着和采着两种可能,没采着的话,跨完时钟域得到4,采着了就得到5。绝对不可能得到比5大的值。 也就是说,只要是格雷码跨CDC,跨过去的值只可能比真实值相等或者小,不可能比真实值大! 所以如果在read时钟域已经看到write_pointer等于5了,那么真实的write_pointer必然不小于5。那么基于write_pointer等于5来判断空,将会得到一个很保守的空(也可以叫假空)!也就是说异步fifo明明还有数,读时钟域就判断出空,暂时停止读取数据。 但是这并不会导致出错,因为这种保守的空判断,只是降低了读的效率,并没有导致读出错误的数据或者不存在的数据。

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 百万级群聊的设计实践

· 永远不要相信用户的输入:从 SQL 注入攻防看输入验证的重要性

· 全网最简单!3分钟用满血DeepSeek R1开发一款AI智能客服,零代码轻松接入微信、公众号、小程

· .NET 10 首个预览版发布,跨平台开发与性能全面提升

· 《HelloGitHub》第 107 期