协议SPI:四线同步全双工 W25Qxx

SPI传输速度快80M,富家子弟最简单最快速完成

SCK-时钟

MOSI主机输出(DO),从机输入

MISO(DI)

SS Slave Select(CS Chip Select)从机选择线,低电平有效,从高电平到低电平就是协议起始信号,反之是结束信号

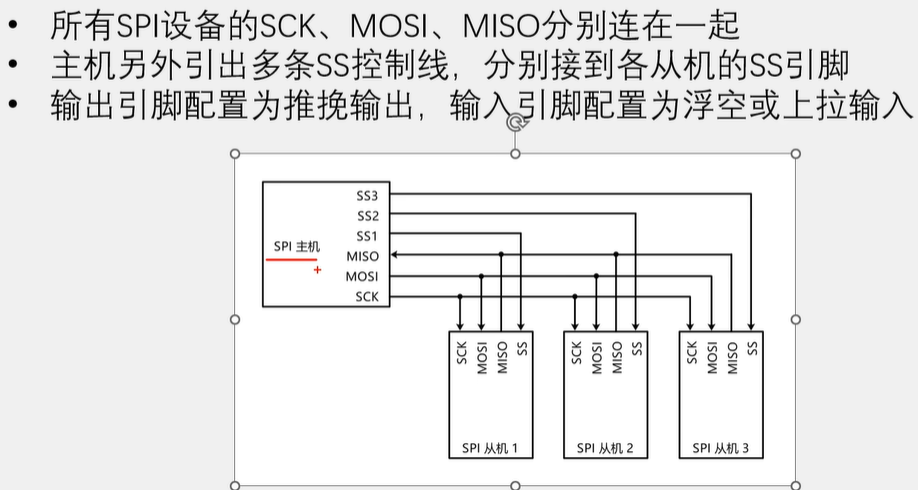

只支持一主多从,

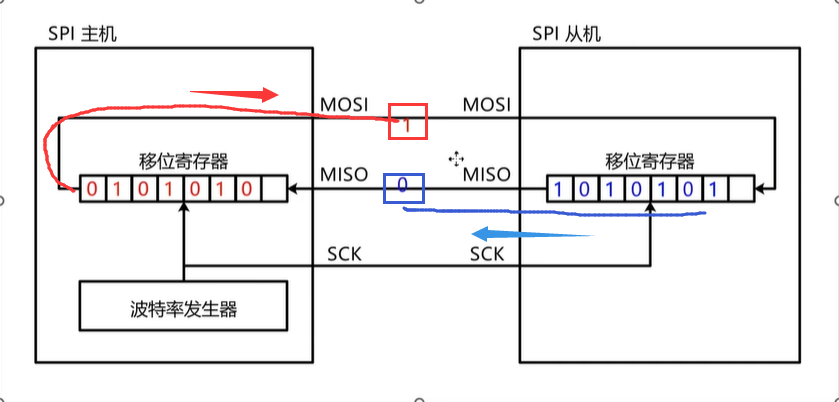

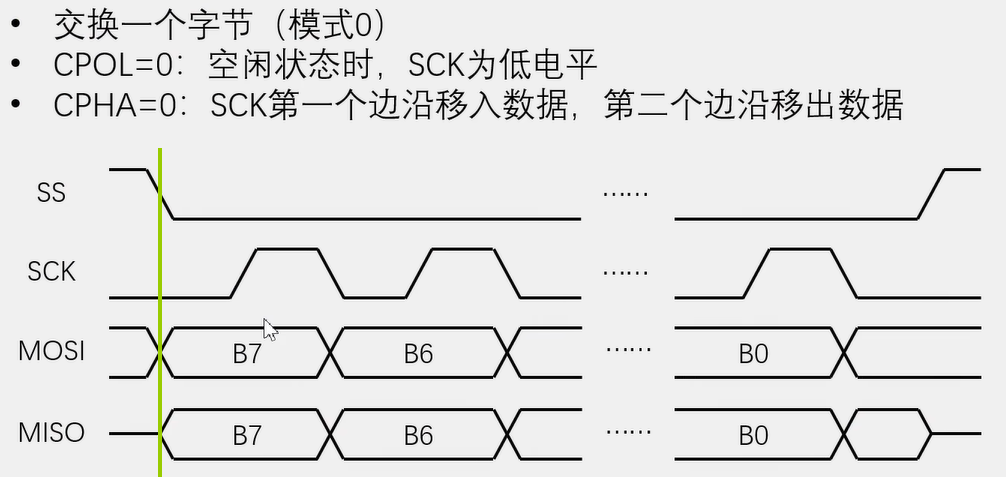

SPI通信基础:主从机的移位寄存器交换字节 (硬件电路的话高低位先行可选择)

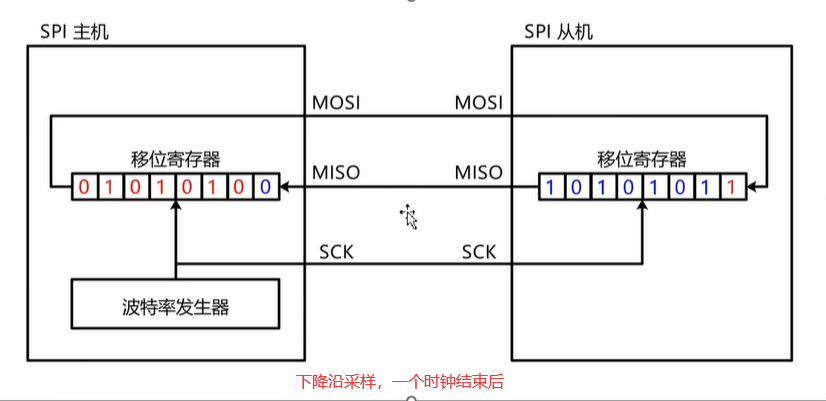

流程(时钟上升沿,移位寄存器向左移位;下降沿采样写入移位寄存器)

只发送:对接收到的数据不处理就行

只接收:发送0XFF

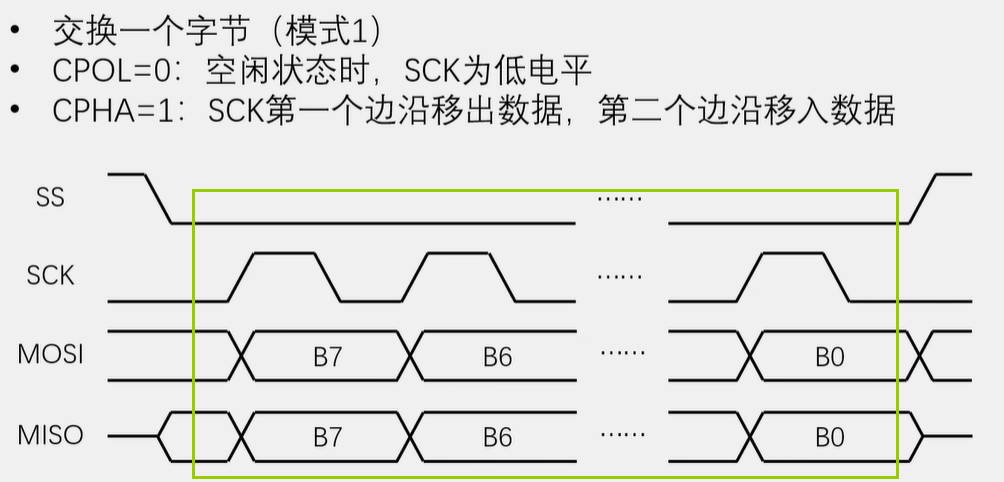

交换多个字节的话,重复绿框内的就行

SPI没有应答机制

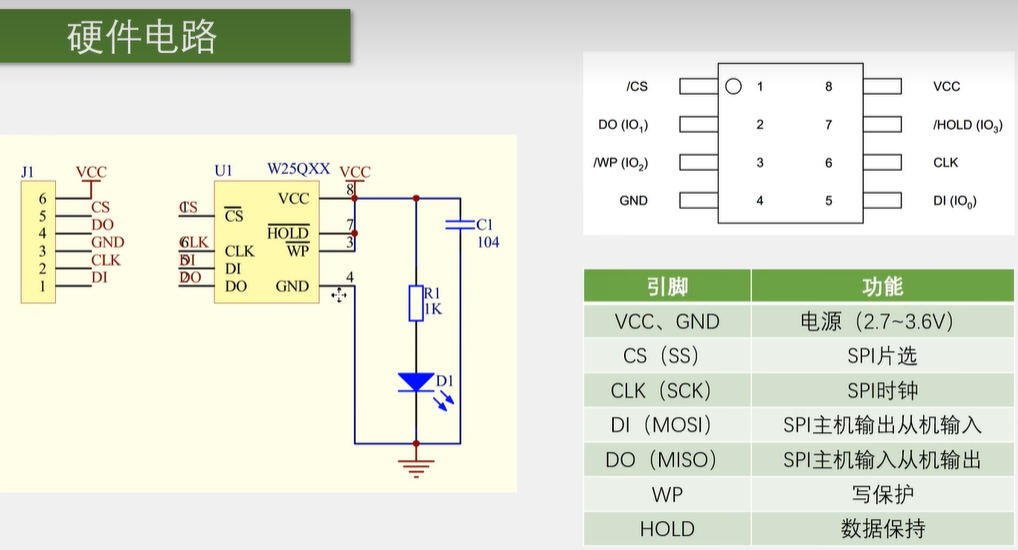

W25Q64 64Mbit/8MByte Nor Flash 非易失

指定地址,读、写入数据;也可以使用地址指针自动+1连续读、写

IO0-3 对应多重SPI

HOLD 数据保持 WP写保护 需要用的话就接GPIO,不需要的话就接VCC

数据划分:块Block(每块64KB - 一共128块) - 扇区Sector(4KB -16 ) - 页(256Bit - 16)[对于整个存储空间]

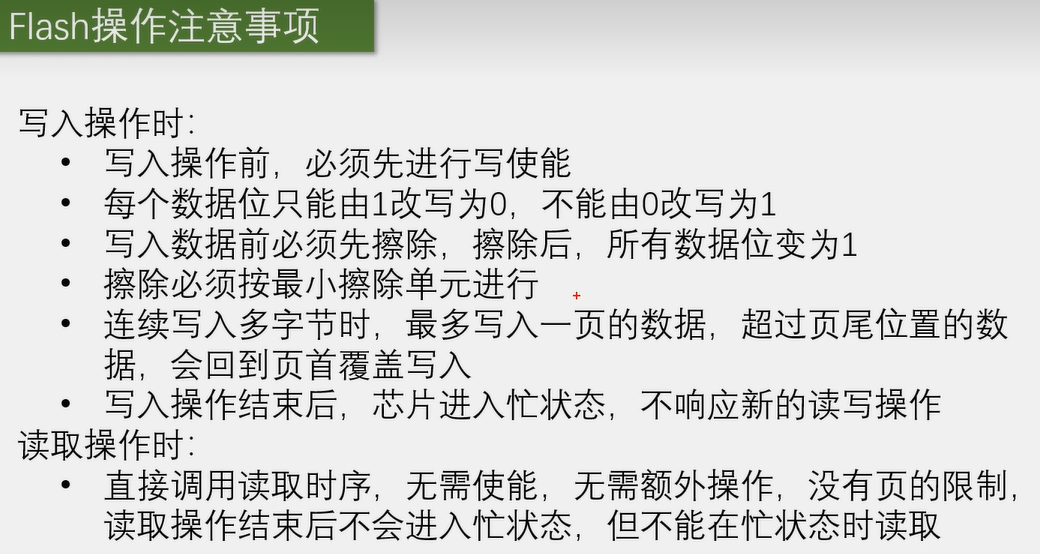

W25Q64的最小擦除单位为一个扇区,也就是每次必须擦除4K个字节

EEPROM 可以按字节修改

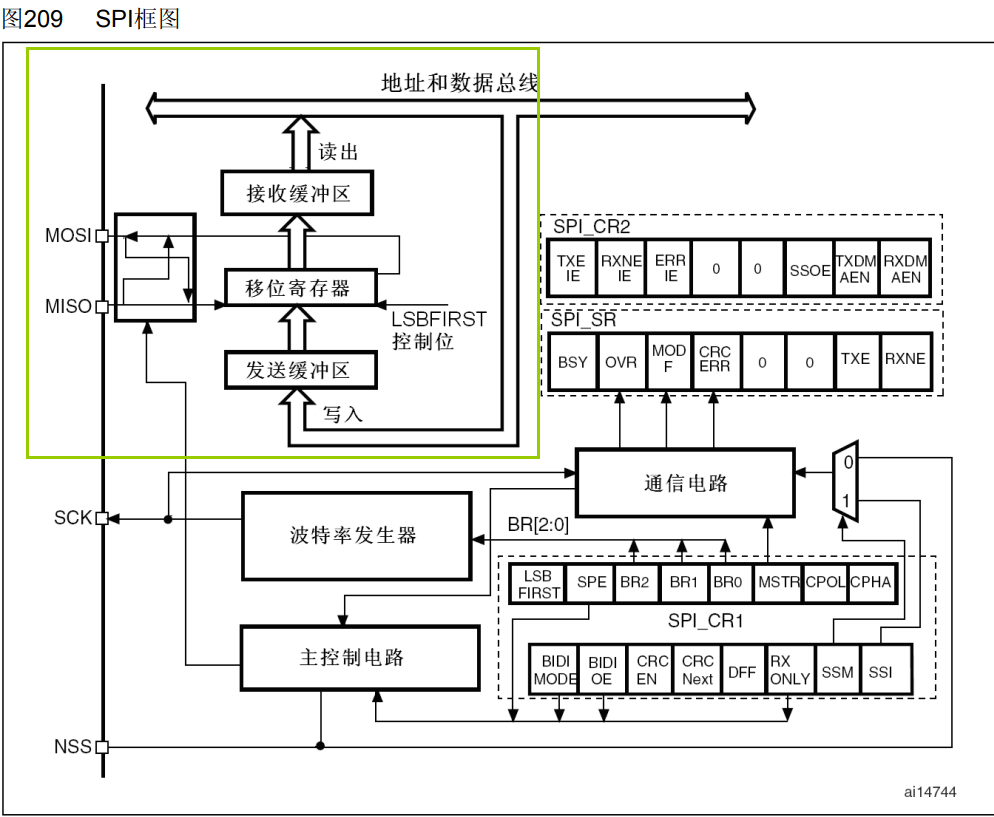

SPI控制逻辑:芯片管理员,执行指令,读写数据

状态寄存器:忙状态,写使能,写保护等

写入芯片的数据会先到特有的256-Byte RAM页缓冲区,然后再花时间刻骨铭心写入FLASH,会置忙碌标志位,此时不会响应新的读写时序

FLASH FF表示空白,还没进行写入 ;最小一个扇区4KB擦除, 使用频率高的数据整体取出来放到RAM,使用完后再写入FLASH

这个芯片不能跨页写入,但可以跨页读

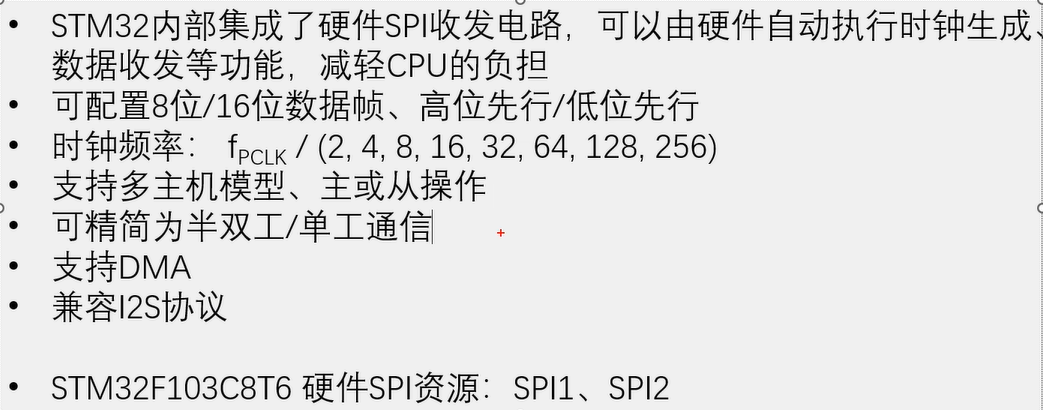

硬件SPI

常用8位数据帧,高位先行

pclk外设时钟,APB2的pclk为72M; 时钟频率为固定的分频后数值

SPI1挂载APB2,SPI2挂载APB1(36M)

IIS是一种数字音频信号传输协议(数据-IIS协议-音频解码器DAC【芯片】)

【移位寄存器右移-低位先行由LSBFIRST控制位决定(0高位。1低位)】数据低位,一位一位从MOSI移出 ;MISO的数据,一位一位移入左边的高位

主从模式变换灵活

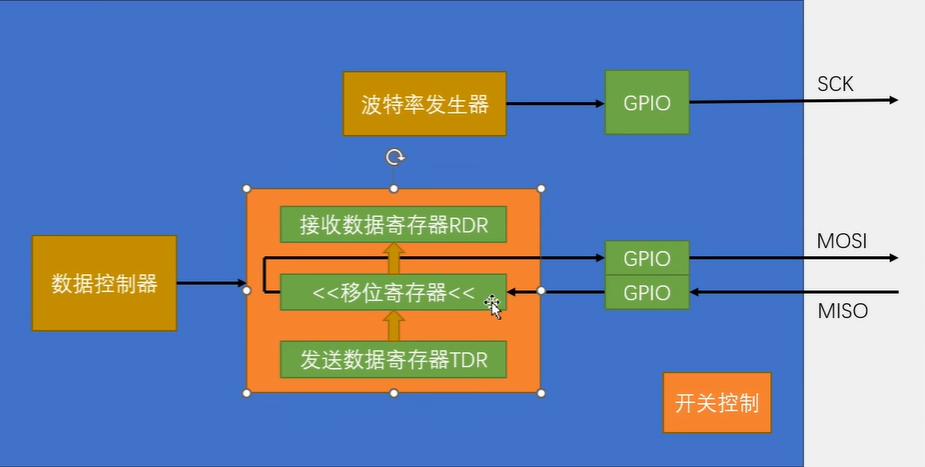

接收缓冲区RDR, 发送缓冲区TDR,占用同一个地址,统称DR

数据传输接收流程:数据先写入TDR,然后移位寄存器空闲的话直接转入移位寄存器(TXE=1)开始移位,同时也进行接收,同时下一个数据也会提前写到TDR中等候

数据移出完成时接收的数据也同时完成,接收的数据会转到RDR(RXNE=1接收寄存器非空),此时需要尽快把数据读出(在下个数据到达之前)

| SPI | 全双工,发送接收寄存器分离,因为数据交换,所以移位寄存器通用 |

| IIC | 半双工,发送接收不同时,共用 发送接收寄存器 与 移位寄存器 |

| USART | 全双工,发送接收寄存器分离,移位寄存器分离 |

NSS主从配置:多个STM32的NSS相连,可配置成输出或输入,当配置为输出,且输出低的时候,自己为主机,其他为从机,也可以配置为输入,接收其他人的输出信号。一旦通过此方法“揪住别人的小辫子”,发送数据就是群发,若要指定还需要地址

硬件SPI,可选择连续传输与非连续传输,后者优点,容易封装,好理解,好用,缺点:性能有些损失(高频下严重) 。前者好用但复杂

前者:发送数据1,发送数据2(等候),接收数据1 后者,发送数据1,接收数据1

解除调试端口的方法:视频6-4

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 【设计模式】告别冗长if-else语句:使用策略模式优化代码结构

· 字符编码:从基础到乱码解决

· 提示词工程——AI应用必不可少的技术