SVA

1、SVA对时序及逻辑较为关心的模块进行直接断言检查。以验证DUT内部信号的时序关系是否符合预期

1、mem 接口:对1r1w的伪双口ram,对2r2w的真双口ram,的读写冲突进行检测。

2、fsm状态机:对状态跳转及状态输出进行监控。

3、coverage收集:某些场景下,信号的组合方式是否进行了测试,需要断言进行cover。

2、SVA 语法及示例:

property a2b_p; @(posedge sclk) $rose(a) |-> [2:4] $rose(b); endproperty a2b_a: assert property(a2b_p); a2b_c: cover property(a2b_p);

当信号a在某一个时钟周期为高电平时,那么在接下来的2~4个时钟周期内,信号b应该为高电平;

assert 检测断言是否满足;

cover检查该场景是否经过测试;

3、断言分类:

1、即时断言:

即时断言基于事件的变化,表达式的计算就像Verilog中的组合逻辑赋值一样,是立即被求值的,而不是时序相关的。

always_comb

immi_a: assert (a && b);

2、并发断言:

并发断言的计算基于时钟周期,在时钟边沿根据变量的采样值计算表达式。进行时序检查时,通常使用并发断言,而很少使用即时断言。

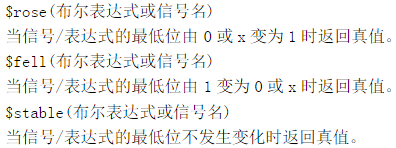

SVA提供了3个内嵌函数,用于检查信号的边沿变化。

sequence rose_s; @(posedge sclk) $rose(a); endsequence

sequence fell_s;

@(posedge sclk) $fell(a); endsequence sequence stable_s; @(posedge sclk) $stable(a); endsequence

上面的sequence会在每个sclk上升边沿检查断言,虽然这些断言是良性的,但它会在一段时间内产生大量的错误信息。

为了避免这种错误的产生,SVA提供了“蕴含”操作符(implication,|->)。其形式为:a |-> b,

当先行算子匹配(成功)时,后序算子才能被计算。如果先行算子不成功,那么整个属性就被默认成功,

蕴含操作符分为两类:交叠蕴含操作符(overlapped implication,|->)表示如果先行算子匹配,后序算子在同一个时钟周期开始计算。

和非交叠蕴含操作符(non_overlapped implication,|=>)如果先行算子匹配,后序算子在下一个时钟周期开始计算。

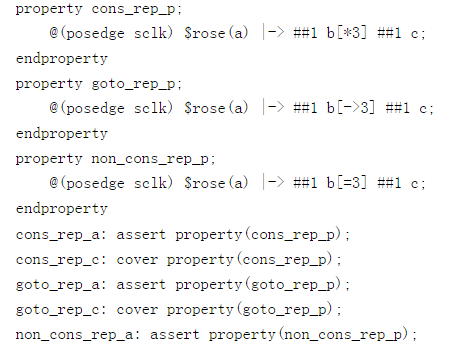

序列的重复操作符分为3类:

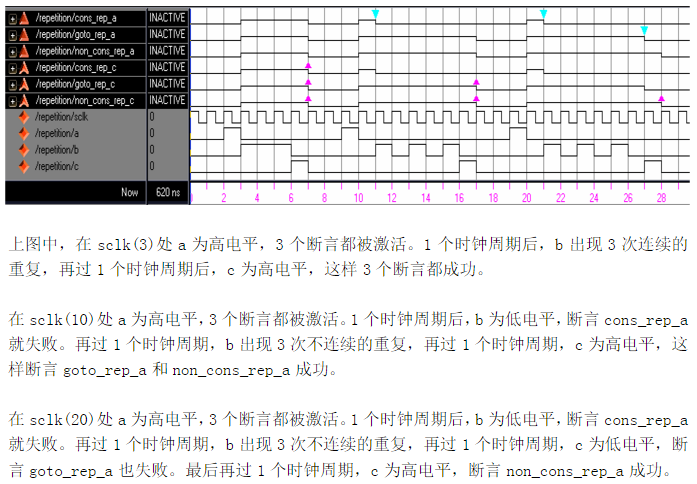

连续重复:a[*3]”表示a被连续重复3次,“a[*1:3]”表示a被连续重复1~3次。连续重复的相邻两次重复之间只有一个时钟间隔。

跳转重复:a[->3]”表示a被跳转重复3次,“a[->1:3]”表示a被跳转重复1~3次。跳转重复的相邻两次重复之间可以有任意时钟间隔。

非连续重复:a[=3]”表示a被非连续重复3次,“a[=1:3]”表示a被非连续重复1~3次。非连续重复的相邻两次重复之间有任意多个时钟间隔。最后一次也可以有任意时间间隔

本文来自博客园,作者:hematologist,转载请注明原文链接:https://www.cnblogs.com/littleMa/p/5832111.html

posted on 2016-09-02 08:59 hematologist 阅读(978) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号