systemverilog 枚举类型

1.定义枚举类型

enum {RED, YELLOW, GREEN} light_1; // int type; RED = 0, YELLOW = 1, GREEN = 2

enum bit[1:0] {RED, YELLOW, GREEN} light_2; // bit type; RED = 0, YELLOW = 1, GREEN = 2

2.定义枚举变量

module tb; // "e_true_false" is a new data-type with two valid values: TRUE and FALSE typedef enum {TRUE, FALSE} e_true_false; initial begin // Declare a variable of type "e_true_false" that can store TRUE or FALSE e_true_false answer; // Assign TRUE/FALSE to the enumerated variable answer = TRUE; // Display string value of the variable $display ("answer = %s", answer.name); end endmodule

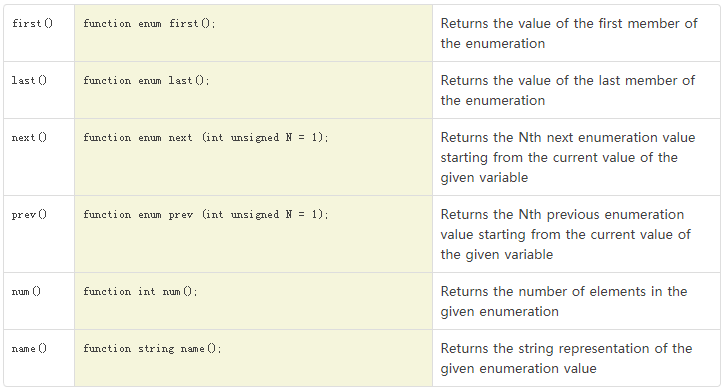

3.枚举变量的方法:

// GREEN = 0, YELLOW = 1, RED = 2, BLUE = 3 typedef enum {GREEN, YELLOW, RED, BLUE} colors; module tb; initial begin colors color; // Assign current value of color to YELLOW color = YELLOW; $display ("color.first() = %0d", color.first()); // First value is GREEN = 0 $display ("color.last() = %0d", color.last()); // Last value is BLUE = 3 $display ("color.next() = %0d", color.next()); // Next value is RED = 2 $display ("color.prev() = %0d", color.prev()); // Previous value is GREEN = 0 $display ("color.num() = %0d", color.num()); // Total number of enum = 4 $display ("color.name() = %s" , color.name()); // Name of the current enum end endmodule

本文来自博客园,作者:hematologist,转载请注明原文链接:https://www.cnblogs.com/littleMa/p/5371210.html

posted on 2016-04-09 11:31 hematologist 阅读(1844) 评论(0) 编辑 收藏 举报