uvm start code

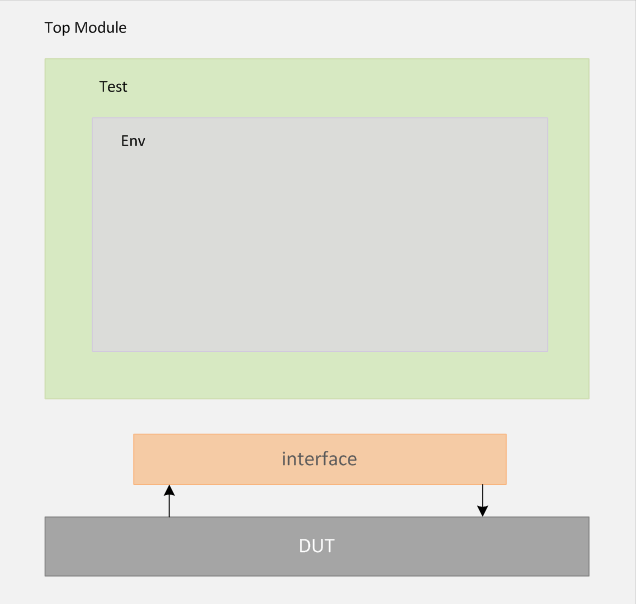

1.基于uvm的验证方法:

1.dut.v

module dut ( input clk, // Clock at some freq input rstn, // Active Low Sync Reset input wr, // Active High Write input en, // Module Enable input wdata, // Write Data input addr, // Address output rdata // Read Data );

2.dut_if.v ,和dut信号和接口一致,没有input output之分,只负责连接。

interface dut_if (input clk); logic rstn; logic [7:0] wdata; logic [7:0] rdata; logic [7:0] addr; logic wr; logic en; endinterface

3.给dut加上dut_if的接口,这样以后dut的连接就只需要传入一个inf的实例化就可以了

module dut_wrapper (dut_if _if); // Instantiate the design module and connect interface signals to DUT dut dsn0 ( .clk (_if.clk), .rstn (_if.rstn), .wr (_if.wr), .en (_if.en), .wdata (_if.wdata), .addr (_if.addr), .rdata (_if.rdata)); endmodule

4.dut_wrapper 的实例化即传入inf的实例。

dut_wrapper dut_wr0 (._if (dut_if1));

5.uvm test部分:面向对象的方式在test内分成几个层次。

class base_test extends uvm_test; `uvm_component_utils (base_test) my_env m_top_env; virtual dut_if dut_vi; function new (string name, uvm_component parent = null); super.new (name, parent); endfunction : new virtual function void build_phase (uvm_phase phase); super.build_phase (phase); m_top_env = my_env::type_id::create ("m_top_env", this); if (! uvm_config_db #(virtual dut_if) :: get (this, "", "dut_if", dut_vi)) begin `uvm_error (get_type_name (), "DUT Interface not found !") end endfunction : build_phase virtual function void end_of_elaboration_phase (uvm_phase phase); uvm_top.print_topology (); endfunction class my_env extends uvm_env ; `uvm_component_utils (my_env) function new (string name, uvm_component parent); super.new (name, parent); endfunction : new function void build_phase (uvm_phase phase); super.build_phase (phase); endfunction : build_phase task run_phase (uvm_phase phase); set_report_verbosity_level (UVM_MEDIUM); uvm_report_info (get_name(), $sformatf ("Hello UVM ! Simulation has started."), UVM_MEDIUM, `__FILE__, `__LINE__); `uvm_info (get_name(), $sformatf("Finishing up with run_phase ... "), UVM_LOW) endtask : run_phase endclass : my_env

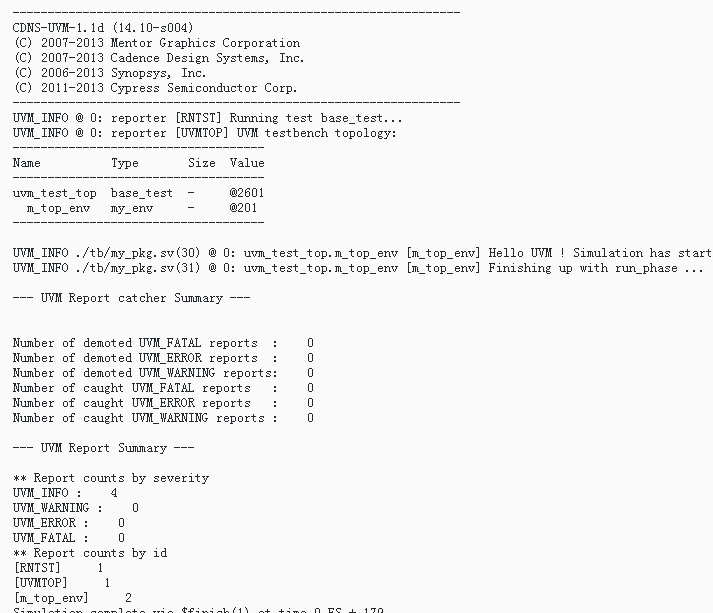

6.最终仿真log

本文来自博客园,作者:hematologist,转载请注明原文链接:https://www.cnblogs.com/littleMa/p/5295662.html

posted on 2016-03-19 17:07 hematologist 阅读(336) 评论(0) 编辑 收藏 举报