sv interface高级用法

1、interface:

interface 中的信号必须声明为logic,因为reg只允许在always块中赋值,wire至允许assign赋值,bit是两态,logic是四态的,且可以阻塞赋值也可以非阻塞赋值。

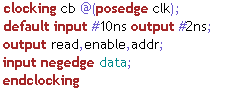

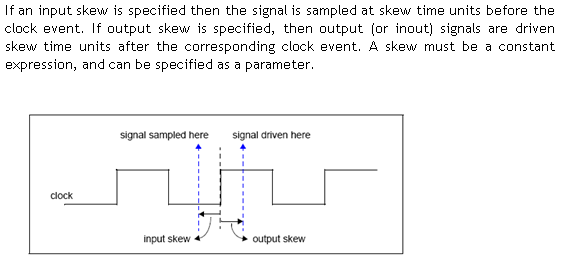

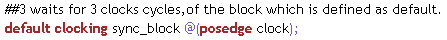

1、clocking block

clocking规定了信号之间的时序关系。

// To wait for posedge of clock @busIf.cb_clk; // To use clocking block signals busIf.cb_clk.enable = 1;

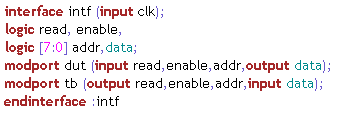

2、modport

modport明确了站在不同的角度对应信号的输入输出方向。

3. parametered interface

interface myBus #(parameter D_WIDTH=31) (input clk); logic [D_WIDTH-1:0] data; logic enable; endinterface

2、interface中定义task和function

task read_memory(input logic [7:0] raddr, output logic [7:0] data); @(posedge clk); ren=1'b0; addr=raddr; @(negedge mrdy); @(posedge clk); data=m2c_data; ren=1'b1; endtask

接口可以直接调用task,来完成信号的赋值。

3、interface中定义always块

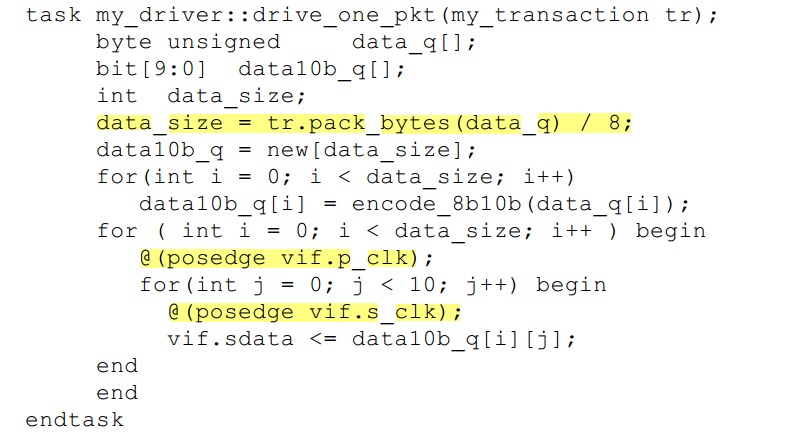

8bit到10bit的转换有专门的算法encode_8b10b完成。通常来说,可以在driver中完成这种转换,并将串行的数据驱动到接口上:

==================================================================================================

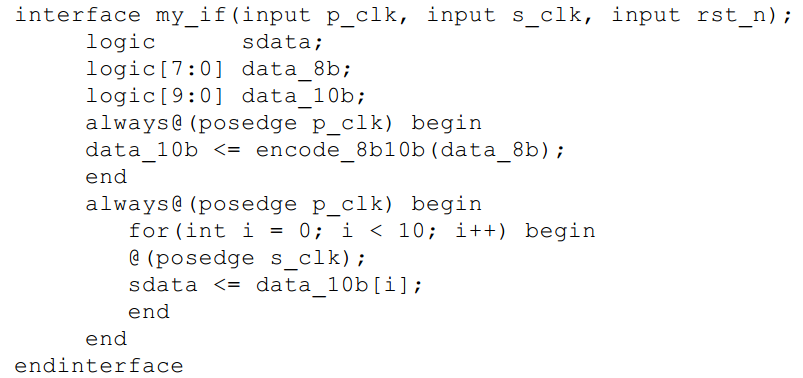

由于8b10b转换的动作适用于任意要驱动的数据,换言之,这是一个“always”的动作,因此可以在interface中使用always语句:

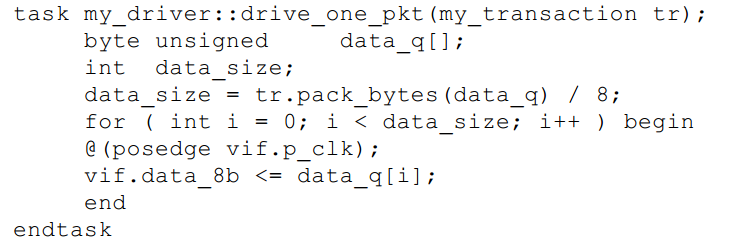

相应的,数据在driver中可以只驱动到interface的并行接口上即可:

==================================================================================================

4、interface中定义initial 块

interface clk_rst_if(); logic clk; logic rstn; initial begin clk <= 0; forever begin #5ns clk <= !clk; end end initial begin #20ns ; rstn <= 1; #40ns ; rstn <= 0; #20ns ; rstn <= 1; end endinterface

5、使用interface替代driver部分功能

上面的uvm实战中的代码用interface代替driver部分功能的举例说明

第一个好处是可以让driver从底层繁杂的数据处理中解脱出来,更加专注于处理高层数据。

第二个好处是有更多的数据出现在interface中,这会对调试起到很大的帮助。 interface可以查看信号的波形,但是uvm component中很难查看信号波形。

本文来自博客园,作者:hematologist,转载请注明原文链接:https://www.cnblogs.com/littleMa/p/10654399.html

posted on 2019-04-04 13:44 hematologist 阅读(6379) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号