Qsys在系统集成中的应用

1.1 摘要

在FPGA设计中可能涉及到集成系统的设计,Altera为这种设计提供了方便的SOPC集成系统,现在又推出了更为先进的Qsys系统,当这种转变提出后,也去尝试使用过Qsys系统,并未发现优势在哪里,无非是界面改变了,一些系统总线需要自己连接了,都是换汤不换药,但是最近看到一则文章才真实了解到Qsys系统相对SOPC系统的优越性。

1.2 Qsys使用条件

随着容量的增加,FPGA设计越来越朝向系统级发展,对于开发高端产品团队来讲,技术积累变得至关重要,对于一个复杂系统,开发团队采用统一的总线协议,研发团队每个人都按照这种总线协议开发功能部件,最终整合成一个系统。这种开发模式采用altera的Qsys系统更加方便,而且在当今产品要求高速研发,高速上市的背景下,这种模式显得非常重要。

过去的FPGA开发都采用的单一作战模式,FPGA厂商只提供一块芯片和一些IP,但是没有提供一个总线式的集成方式,后来推出SOPC后,对系统集成提供了一种可行的模式,但是SOPC都主要是针对IP级的系统构建,抽象程度不高,而且对于Altera最新系列中规划的Cortex内核无能为力,因此Qsys应运而生。

1.3 Qsys对于SOPC优势(摘抄于电子工程世界)

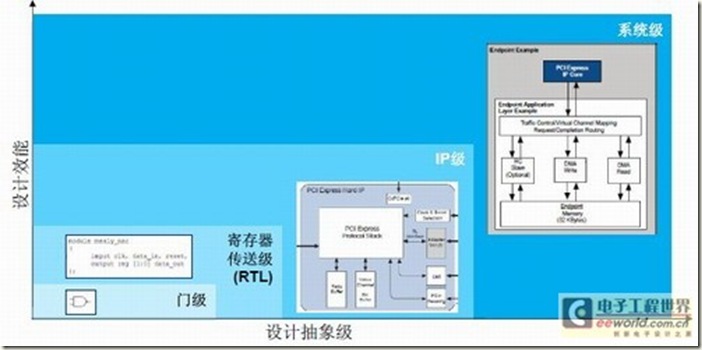

Qsys的设计理念是本着提高设计抽象级,从而使机器自动生成底层代码。从最开始的门级电路,到寄存器传输级(RTL),SOPC Builder所提出的IP级到现在Qsys提出的系统级模式。

随着容量的增加,FPGA设计越来越朝向系统级发展

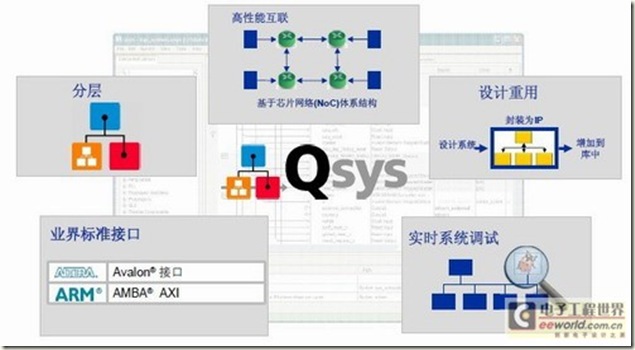

针对设计级别的提高,Qsys采用了片上网络架构,在这个架构上IP可以直接互联,这样标准化之后,软件便可以自动为标准内核及交合逻辑提供标准化互联,而用户所作的只是修改自己的定制逻辑即可。

现在,经过Qsys认证的IP核有100多个,每个认证后的IP都带有兼容标识,产品组合包括接口协议、存储器、视频和图像处理、嵌入式总线以及处理器等。

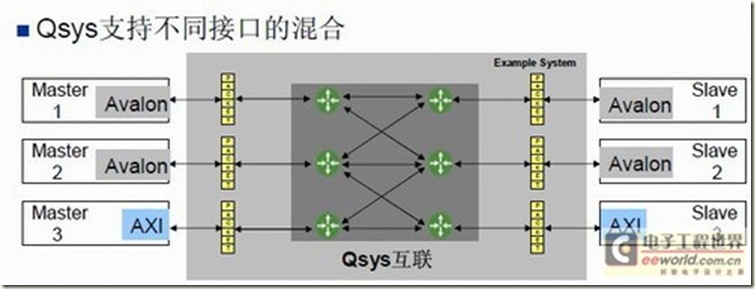

正是由于采用了标准化IP接口,对于设计复用来讲,接口不必要重新设计,此外通过标准接口,Altera的Avalon总线的IP可以与ARM AMBA总线通过Qsys混合。

Qsys互联,使AXI和Avalon总线互联

Qsys的设计重用流程具体为:导入RTL设计,Qsys进行自动封装及改进IP库,之后就可以成为独立IP来复用了。

Qsys的几大优势

对于验证调试来说,Qsys的系统控制器可以对位地址进行读写操作而不是对每个寄存器进行读写,通过更细致的验证手段,可减少验证流程,缩短产品调试时间。此外,Qsys提供了完整的系统控制台GUI,包括收发器工具包、外部存储器接口工具包以及电路板测试系统等。