007 Ethernet(以太网)详解(二)

一、以太网

二、硬件设计

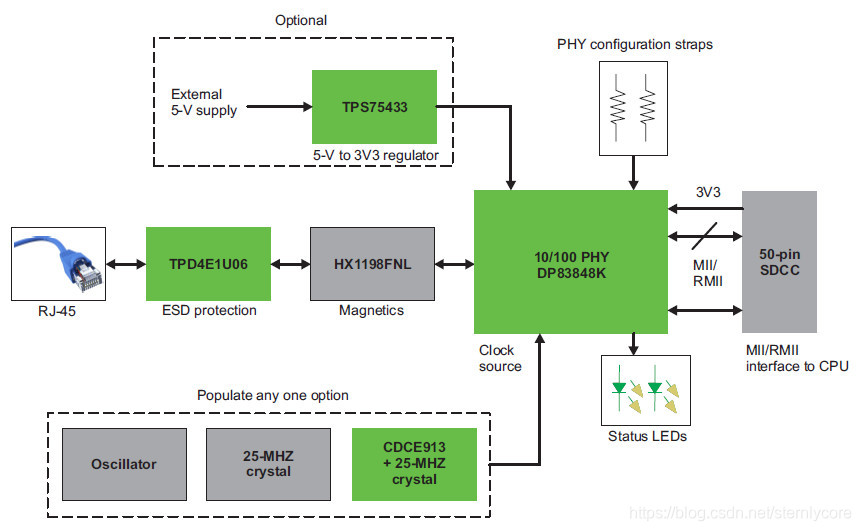

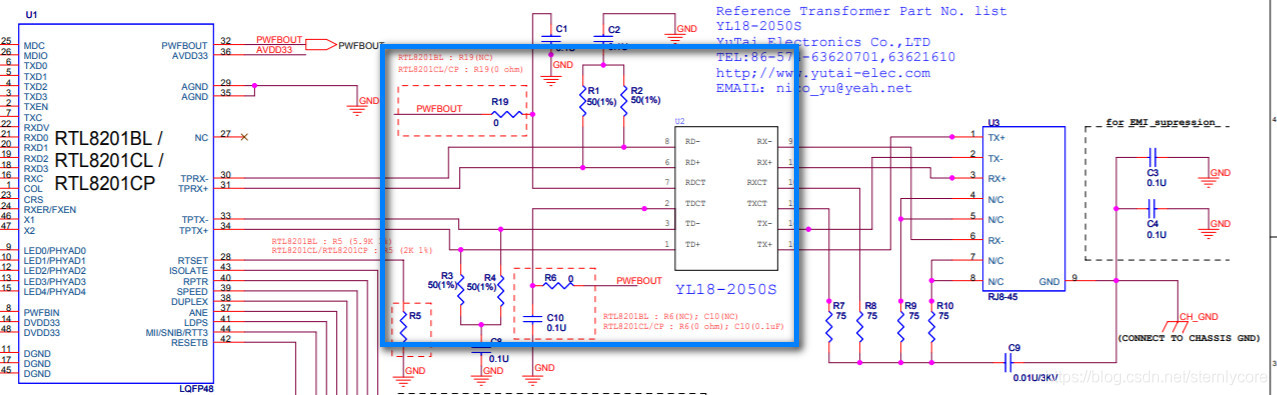

以太网接口硬件设计中,现在CPU集成度越来越高,都会集成MAC,而对于硬件设计来说,只需要外接PHY Transceiver IC即可实现以太网通信,而PHY芯片(以百兆为例)外围电路基本如下所示:

RJ45连接器

ESD保护芯片

网络变压器

PHY Transciver

MAC Controller

晶体

电源

状态指示灯

1、RJ45连接器

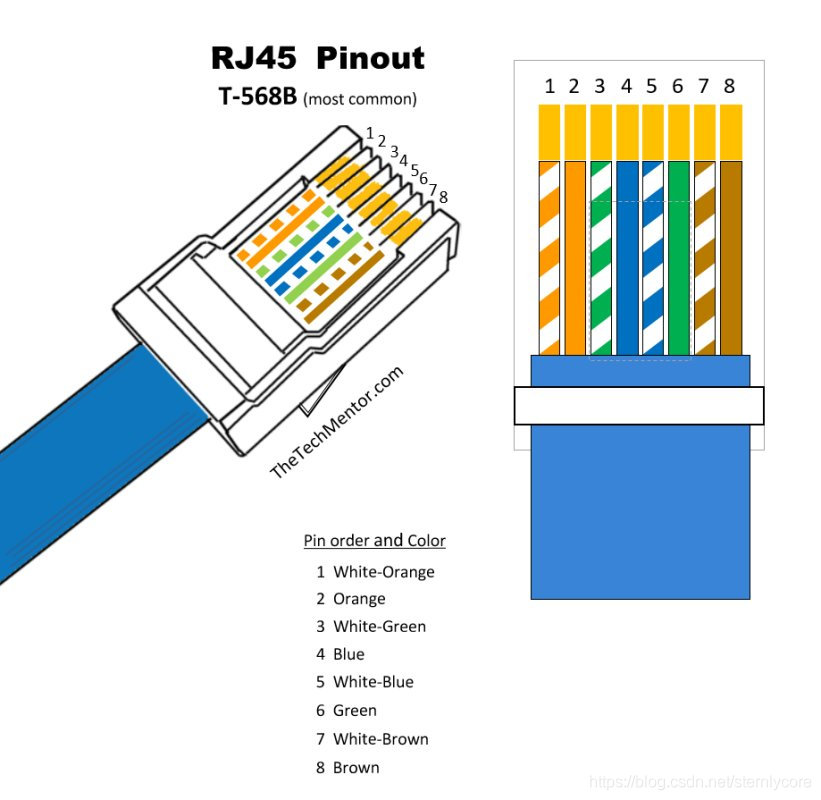

RJ是Registered Jack的缩写,意思是“注册的插座”。在FCC(美国联邦通信委员会标准和规章)中RJ是描述公用电信网络的接口,计算机网络的RJ45是标准8位模块化接口的俗称。连接器由插头(8P8C接头,水晶头)和插座组成。如下图所示:

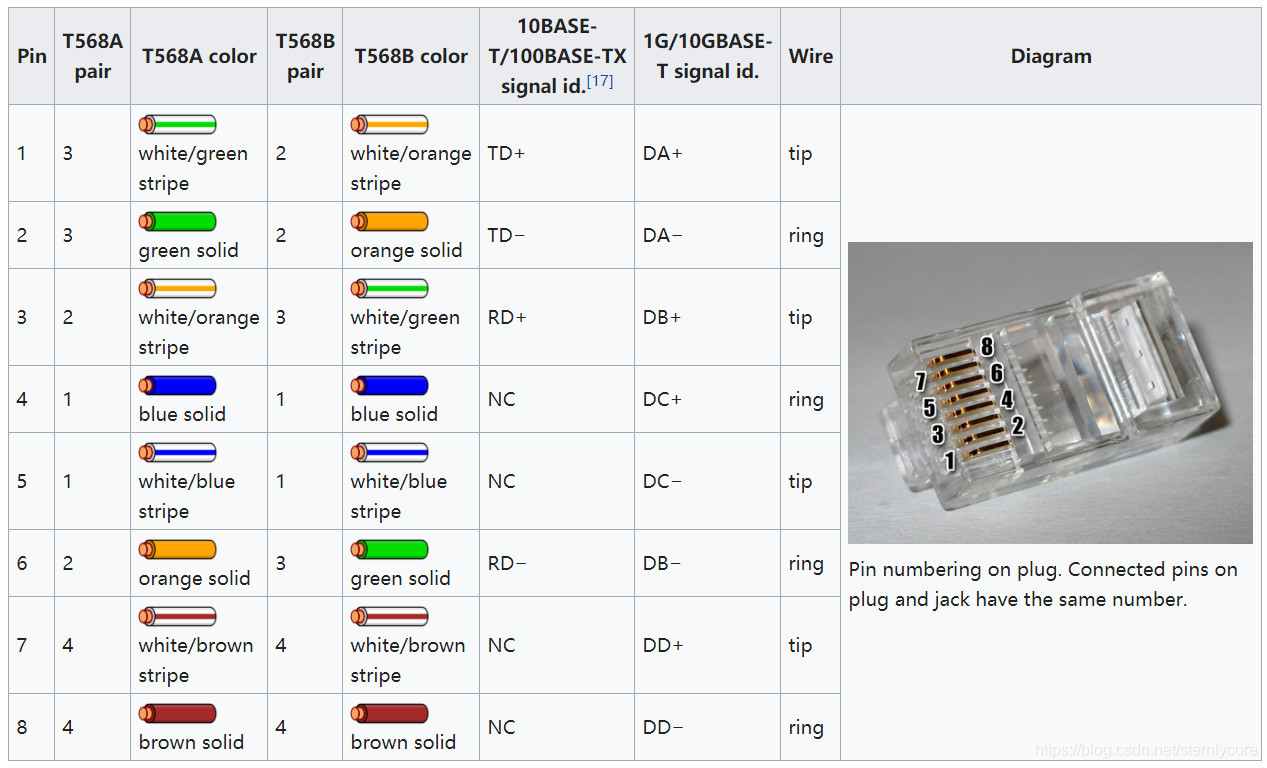

关于接头引脚定义,目前存在两种标准:T568A和T568B(最通用)。这两者的主要区别是橙色和绿色双绞线进行了交换,如下图所示:

设计这两种标准只是在线缆颜色上有所区别,目的是在线缆侧实现交叉互连。网络直通线常用于异种网络之间的互连(比如计算机交换机之间),交叉线常用于同种网络之间的互联(比如计算机与之间)。不过现在PHY芯片大部分具有自动交叉(auto MDI-X)的能力,只需要直连即可。不同网络速率及网络介质下引脚作用也不相同,如下图示意:

关于RJ45插座,也有很多分类。根据功能划分,内部有无集成变压器,有无集成LED指示灯,根据外壳分类是否金属或塑料,有无金属弹片等,进行选型时需要清楚明了。

2、ESD保护芯片

在一些工业场景下环境恶略需要增添ESD保护器件,ESD器件一版放到靠近连接器位置,对于百兆以太网来说只需要4通道低结电电容器件,根据需要的静电等级进行型号选型。

3、网络变压器

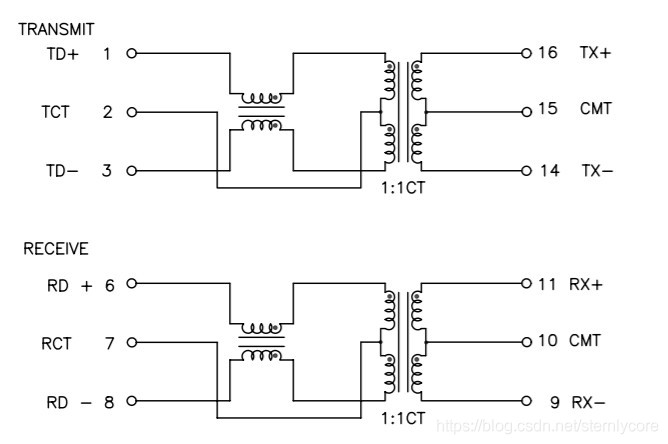

网络变压器作用是:

耦合差分信号,抗干扰能力更强

变压器隔离网线端不同设备的不同电平,隔离直流信号

网络变压器一般是由差模线圈,变压器以及中心抽头组成。如下示意:

其中初级中心抽头的接法需要根据PHY芯片来决定,电压驱动的就要接电源,电流驱动直接接个电容到地即可,是具体还要参看芯片的datasheet和参考设计了。 还需要注意的是有的变压器中间抽头是独立的有的是收发合并在一起的,设计的时候需要注意,为了防止初版硬件设计错误,可以兼容设计,如下所示:

变压器次级中心抽头使用Bob Smith电路来抑制共模噪音,利用75Ω和电容接地吸收共模能量,如上图原理图所示。

注意:有的RJ45 J已经内置了网络变压器,设计时特别注意下内部框图是如何连接的。

关于PCB Layout时,需要注意:

PHY芯片,变压器,连接器Trace需要做100Ω±10%阻抗设计,走线尽量短

差分对做等长设计,偏差小于0.5mm

避免分支

差分对走线参考平面完整

4、PHY Transceiver

作为以太网外围电路的核心器件,需要根据实际应用来选择合适的PHY芯片,基本选型指标如下:

10/100/1000Mbps

接口类型MII/RMII/GMII/RGMII/SGMII

支持单端口/双端口

光纤/电口 PHY

供电电压及工作温度

根据指标选择芯片制造厂商PHY芯片,根据datasheet以及参考手册进行设计。常见的PHY芯片厂商:

1)TI-PHY

2)MicroChip-PHY

3)Marvell-PHY

4)Realtek-PHY

5、MAC Controller

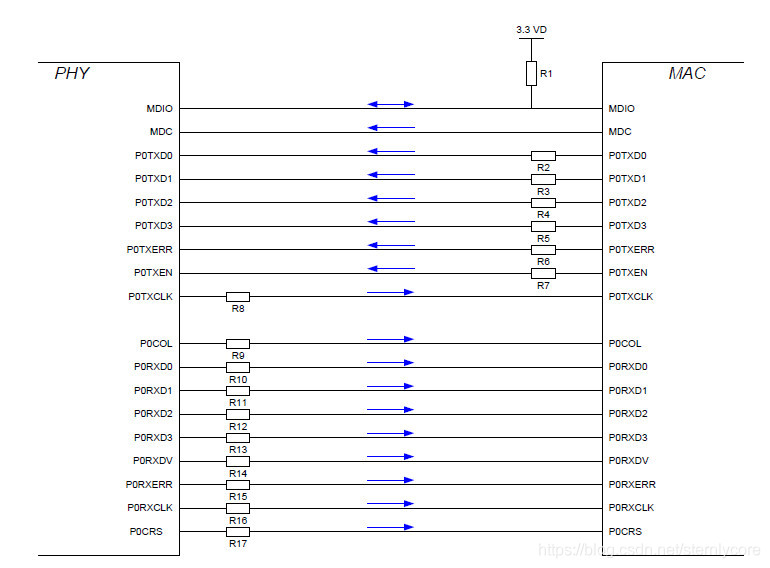

MAC端需要注意的就是使用什么接口,常见的MII/RMII/GMII/RGMII。

MII接口:

MDIO一般上拉1.5KΩ电阻

信号线需要串联电阻一般为10Ω,发送端靠近MAC,接收端靠近PHY

MII信号线单端对地阻抗应设计为50Ω±10%

TXD[3:0],TXCLK,TXEN,TXERR保证等长设计

RXD[3:0],RXCLK,RXDV,RXERR保证等长设计

信号线走线避免分层

时钟线包地处理

RMII:

50MHz外部时钟

走线规则同MII

不使用的IO可以当作GPIO使用,有的也当作复用信号,详细参考datasheet

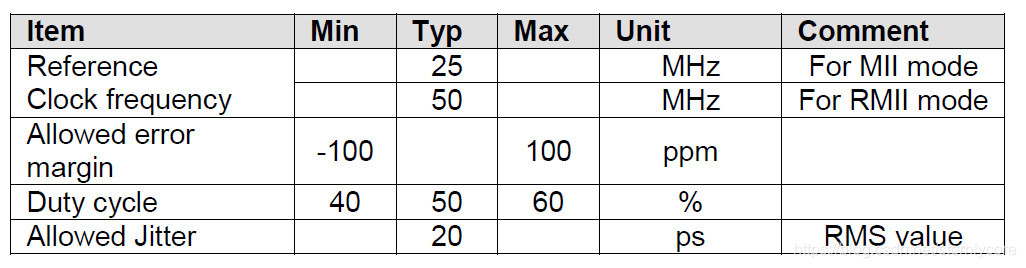

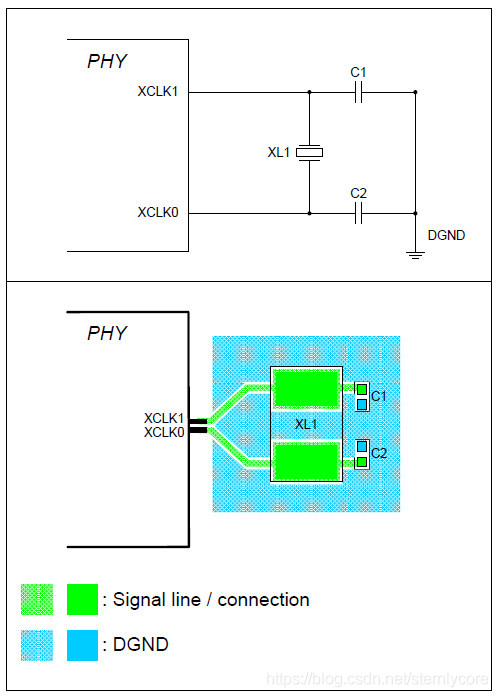

6、晶体

晶体可以使用无源晶体以及有源晶振,50MHz应用中应使用有源晶振。需要保证晶体如下规格:

使用无源晶体时:

晶体电路靠近芯片

时钟信号原理电源以及干扰信号

时钟信号包地处理

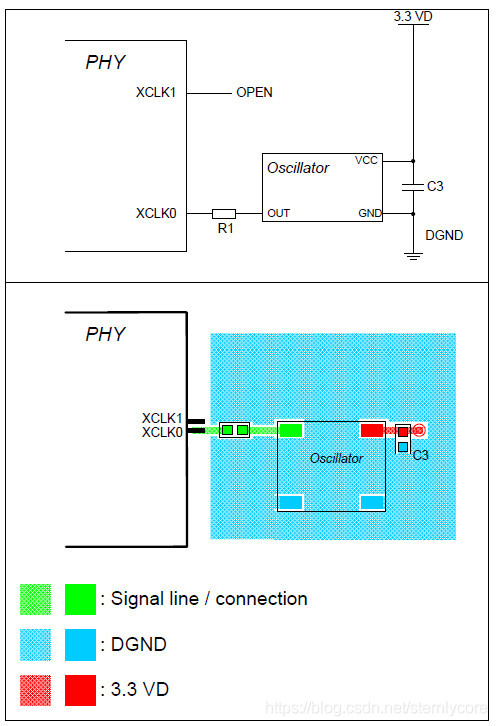

使用有源晶振时:

需要外接供电

XCLK1不连接

走线规则参考无源晶体

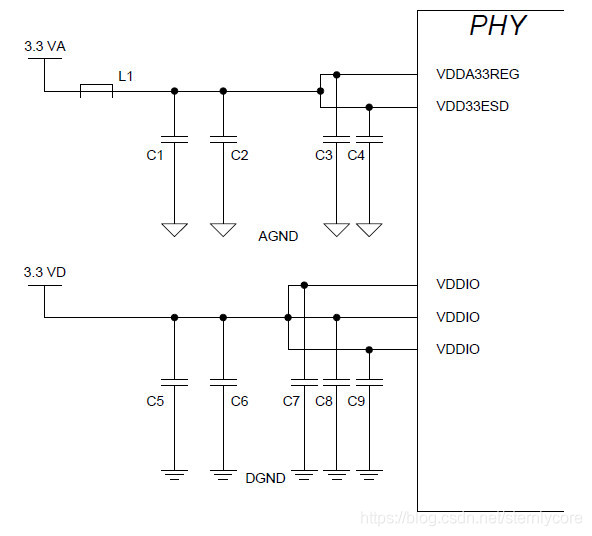

7、供电

根据PHY芯片Datasheet进行设计,如下参考:

主电源上使用磁珠(Murata BLM21AG121SH1),去耦电容(10uF+100nF)组合

数字电源使用100nF滤波

8、状态指示灯

状态指示灯代表了网络连接速率状态,LED亮灭状态是由PHY芯片控制,没有标准定义,具体参考PHY Datasheet。

三、测试

1、测试工具

测试离不开工具的使用,如下:

- Tektronix DSA71254B 示波器

- Tektronix 3.5GHz 差分探头(型号P7330)

- 示波器自带夹具(TC6)

2、测试夹具

测试夹具连接示意如下:

3、测试项目

- 模板(template):要求Active Output Interface (AOI) transmitting scrambled Halt

Line State 必须在模板内 - 差模输出电压(differential output voltage):沿漂移应在950mv~1050mv 内

- 振幅对称度(Signal Amplitude Symmetry):0.98~1.02

- 升降时间(rise and fall time):AOI 的升降时间应在3.0ns~5.0ns 范围(以电压的

10%~90%区间定义)。所有测量值的差异应不小于0.5ns - 波形的过冲(waveform overshoot)::过冲是相对于Vout 的百分漂移,不能超过

5% - 抖动(jitter):the peak-to-peak jitter should not exceed 1.4 ns

- 占空比失真(duty cycle distortion):在输出波形沿跳变的50%电压点测量

- 回波损耗(return loss)

这些测试一般都是特定的case,仪表都可以自动化完成测试。还需要测试:

- 时钟频率波形

- 电源供电波形

4、功能测试

4.1、Ping测试

与PC连接,配置好网段IP,进行Ping测试,如下示意:

4.2吞吐量测试

吞吐量测试一般都是跑iperf测试,windows电脑端可以下载JPerf软件。一端当client,另一端当server,进行吞吐量测试,如下示意:

client:

server:

4.3、抓包工具

网口进行数据分析时,需要使用抓包工具,一般使用Wireshark软件,如下示意:

4.4、EMI测试

MII信号对于通过RE测试至关重要,速率越高对应的辐射也就越高。测试表格如下示意:

4.5、ESD测试

测试标准:IEC61000-4-2 Level 4, Criterion B

四、参考资料