012 GMII、SGMII和SerDes的区别和联系

一、GMII和SGMII的区别和联系

GMII和SGMII区别,上一篇已经介绍了,这一篇重点介绍SGMII和SerDes区别。

GMII和SGMII

|

GMII |

在MII接口基础上提升了数据位宽和Clock频率成为1000Mbps接口 |

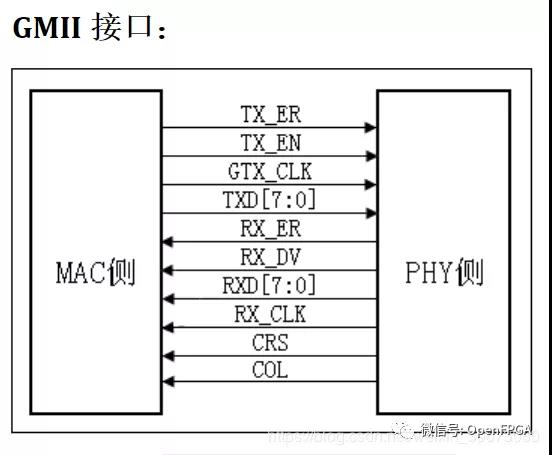

RXD[7:0]、TXD[7:0] TX_ER、TX_EN RX_ER、RX_DV GTX_CLK、RX_CLK CRS、COL |

Clock=125MHz 数据位宽8bit(一个时钟周期传输8bit数据) 1000Mbps=125 MHz *8bit |

|

SGMII |

串行GMII,在此基础上提升了时钟频率达到1000Mbps |

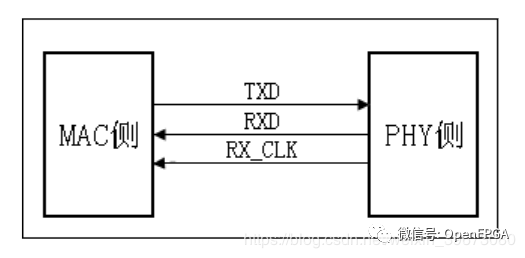

RXD[0]、TXD[0] RX_CLK |

Clock=125MHz 数据位宽1bit(一个时钟周期传输1bit数据) 串行数据帧:一帧10bit(8bit data+2bit control) 计算有效带宽时需要去掉控制位 1000Mbps=125 0MHz *(8bit/10bit) |

GMII接口

SGMII接口

二、SGMII和SerDes的区别和联系

终于到了今天的猪脚-SerDes,为什么拿SGMII和SerDes进行对比,主要原因是,SerDes是一个串行接口,和SGMII很像,和GMII几乎没有什么交集,所以两者对比就没有什么实际意义,所以只进行SGMII和SerDes进行对比。

由于SerDes在PCIe部分起着非常重要的作用,所以这部分详细内容会放到PCI-e部分详解,这里只是简单介绍一下:

SerDes,是SERializer(串行器)和DESerializer(解串器)的简称,是一种点对点的高速串行通信技术,串口协议跟IIC、SPI等总线协议还是有很大差别的,最大的特点就是点对点收发、没有随路时钟,它的速率是隐含在协议里的,双方必须按照约定好的波特率进行数据的发送和接受才能正确的完成通信,SPI则是主机向从机发送时钟,从机在这个时钟的上升沿采样数据、下降沿发送数据,最开始人们为了提高通信速率的思路有两条:提高随路时钟频率、增加数据通路位宽,这都很好理解,举个栗子就是四线SPI(Qspi),但逐渐地这种思路就遇到瓶颈!

第一、时钟频率的不断增加,时钟抖动和偏斜的因素变得更加明显,也增加了时钟质量的要求,为了充分利用时钟,工程师们还想到了利用下降沿,没错,就是DDR!第二、数据总线的增加意味着管脚数的增加,这会引起PCB布局布线的灾难。人们又开始把思路回到不用时钟线的串口协议上。先看看串口收发器的伪代码!

1 //串口收发器 SerialTransceiver 2 module serialTR( 3 input sys_clk, 4 input rst_n, 5 //可配置单双工,双工模式 6 input [1:0] I_rxtx_en, //收发使能,高有效 7 output [1:0] O_rxtx_done, //收发完成脉冲信号 8 9 input RX, //串口总线 10 output TX, 11 //数据位宽可配置 12 input [7:0] data2tx, //待发送数据 13 output [7:0] data2rx //待接收数据 14 ); 15 16 //串口接收 ---> 串转并 17 always@()begin 18 if(!rst_n) 19 //寄存器复位 20 else if(I_rxtx_en[1]) 21 //1、下降沿检测,获取起始位 22 //2、3、4、5、6、7、8、9波特率定时器,采样数据 23 //9、10接收校验位和结束位 24 //11、12、产生完成脉冲信号 25 end 26 //串口发送 ---> 并转串 27 always@(!rst_n)begin 28 if(!rst_n) 29 //复位 30 else if(I_rxtx_en[0]) 31 //1、构建数据格式 32 //2~12 按位发送 33 //13、14产生完成脉冲信号 34 end 35 36 37 endmodule

这里想说明的是:

1、串口的单双工和数据位宽都是可以配置的,按照自己的需求去设置;2、串口协议也是有时钟的,只不过这个时钟是隐含在协议里,除了常见的9600、38400、115200,自己也可以去配置特殊模式的串口,关键是双方都要遵守相同的协议,那么SerDes呢?

相同的,SerDes也是收发两条线,准确地说,是两组,因为它是差分形式,即tx_p、tx_n,rx_p、rx_n;在数据端也是可以配置成不同的数据位宽和单双工模式;

不同的,就是在于SerDes的时钟是隐含在数据中!这就需要额外的电路去完成数据和时钟的“融合”与“解析”,而这正是PCS和PMA的作用,其内部采用的编码技术和信号补偿技术正是为了完美的将时钟“融合”进串行数据(发送端),再将时钟从串行数据中“解析出来”(接收端)。

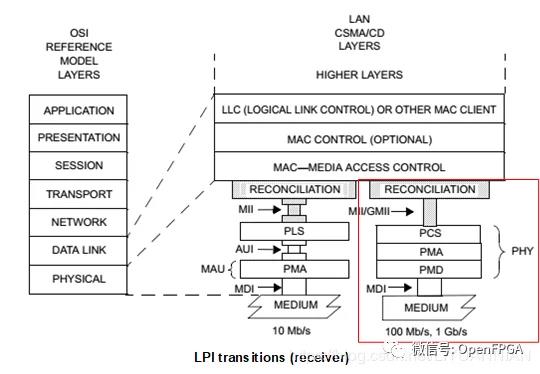

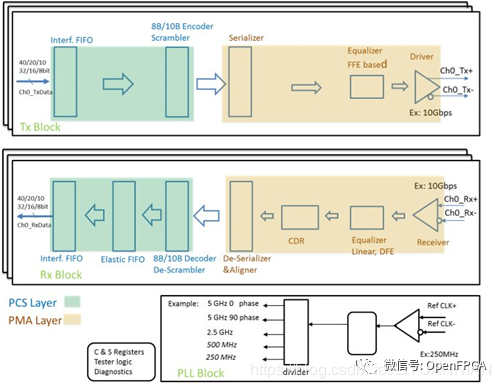

SERDES主要由物理介质相关( PMD)子层、物理媒介附加(PMA)子层和物理编码子层( PCS )所组成。PMD是负责串行信号传输的电气块。PMA负责串化/解串化,PCS负责数据流的编码/解码。在PCS的上面是上层功能。针对FPGA 的SERDES ,PCS提供了ASIC块和FPGA之间的接口边界。

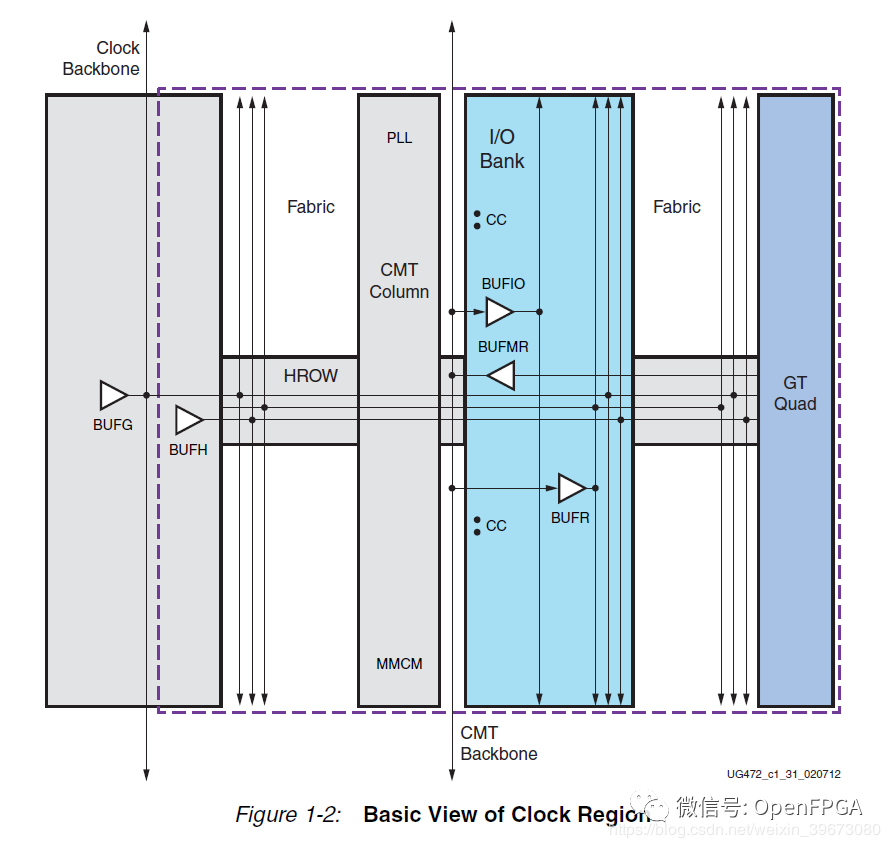

Xilinx将这个SerDes硬核进行了封装,成为GigabitTransceiver,即GT,而它在BANK里的位置和数量都是固定的,从这个角度来看这也算是它不灵活的不足所在吧。

接下来就是SGMII和SerDes的区别

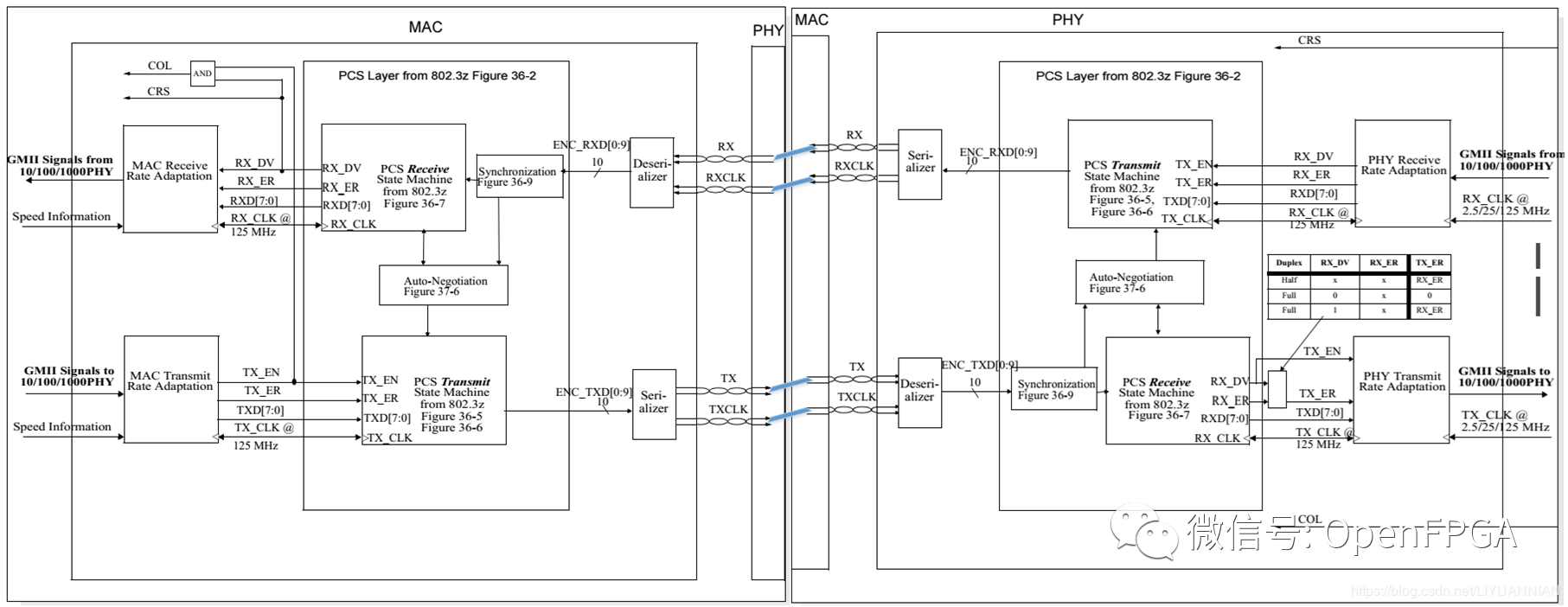

图1 SGMII的MAC侧和PHY侧

刚看到上图时,感觉很奇怪,PCS为什么还存在于MAC中?GMII规范中PCS只存在于PHY中,见下图。

图2 GMII在OSI模型中的位置

实际上SGMII对应的MAC和PHY的划分是将SGMII接口断开,一端归为MAC,一端归为PHY;同样,GMII对应的MAC和PHY的划分是将GMII接口断开,一端归为MAC,一端归为PHY。下图是将图1整理后的图。

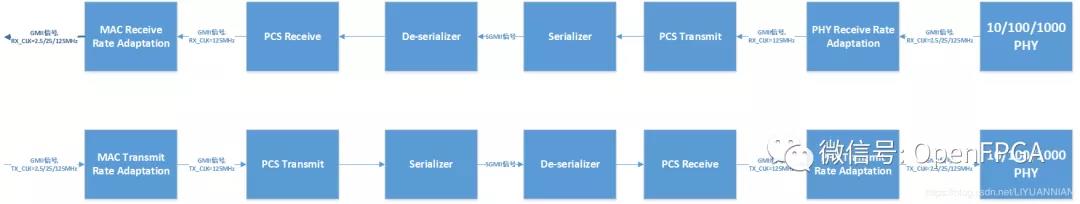

图3 整理后的SGMII信号接收和发送流程

上图可以看出,SGMII接口就是使用了SerDes技术的GMII接口,SerDes上跑的是10b信号,在接收端,PCS Transmit将GMII的8b信号编码为10b信号,经过Serializer串行化后在SerDes高速路上传输到PCS Receive模块,它将10b信号解码为8b信号送至MAC Receive Rate Adaptation模块。因此SGMII相对于GMII多了个S,这个S就是SerDes技术,它提供了一个高速传输通道。

在交换芯片中经常可以看到1个Port可以被配置为SGMII/SerDes模式,个人理解的是SGMII相对于SerDes多了一个速率协商(比如上图中的PHY Receive RateAdaptation模块),当使能了SGMII模式,就是使能了PHY Receive Rate Adaptation模块,当使能了SerDes模式,就是禁用了或者未使用PHY Receive RateAdaptation模块,这样猜测的原因是在光模块或者电模块选型时,发现SerDes接口的光模块或电模块总是仅支持1000Mbps速率;而SGMII接口的电模块总是能支持10/100/1000Mbps速率,但是没看到能支持这种猜测的文章。

下图是SerDes的发送和接收结构。

图4 SerDes的发送和接收结构

SerDes通道传输的10b信号,因此在SerDes发送端,需要上图的PCS实现8b/10b编码,之后是串行化以上高速跑道;

在SerDes接收端,需要上图的PCS实现10b/8b解码,之后是解串行化,以下高速跑道。

在进行电路设计时,当交换的1个Port配置为SerDes模式,它能接光模块和电模块,但是速率是不可协商的,当接光模块,光模块也仅是进行光电或电光的转换,以在光纤中传输,并不涉及到PCS等概念;当配置为SGMII模式,它只能接电模块,因为电模块内部是有PHY和变压器的,所以此时的设计模式就是MAC+PHY+变压器的常规模式。

三、总结

其实,大多数MAC芯片的SGMII接口都可以配置成SerDes接口(在物理上完全兼容,只需配置寄存器即可),

SerDes直接外接光模块,而不需要PHY层芯片,此时时钟速率仍旧是625MHz,不过此时跟SGMII接口不同,SGMII接口速率被提高到1.25Gbps是因为插入了控制信息,而SerDes端口速率被提高是因为进行了8B/10B变换,本来8B/10B变换是PHY芯片的工作,在SerDes接口中,因为外面不接PHY芯片,此时8B/10B变换在MAC芯片中完成了。8B/10B变换的主要作用是扰码,让信号中不出现过长的连“0”和连“1”情况,影响时钟信息的提取

所以感觉是mac芯片用加2bit控制信息的功能模块去完成了8B/10B变换,这样SerDes信号就可以直接出去了。

SerDes通道和SerDes接口是两个概念,SGMII也是需要SerDes通道(SERDES lane)的。

而SGMII需要插入2bit控制信号变成10b是因为SGMII需要控制信来实现10/100/1000速率协商,而SerDes是固定速率(1000BASE-x)。

PHY收到mac sgmii的10b后,将控制信号去除后,将数据发送出去前还是会加扰码完成8B/10B变换。

四、参考资料

1、https://mp.weixin.qq.com/s/HcnvxrIuoW_9rXSIkOY1tw

浙公网安备 33010602011771号

浙公网安备 33010602011771号