理解AXI Quad Serial Peripheral Interface(SPI) IP核

reference : PG153-AXI Quad SPI v3.2 LogiCORE IP Product Guide.pdf

在使用MicroBlaze过程中,调用了此IP,所以有必须仔细学习下;

名词:

XIP: eXecute In Place

Motorola M68HC11

支持特性:

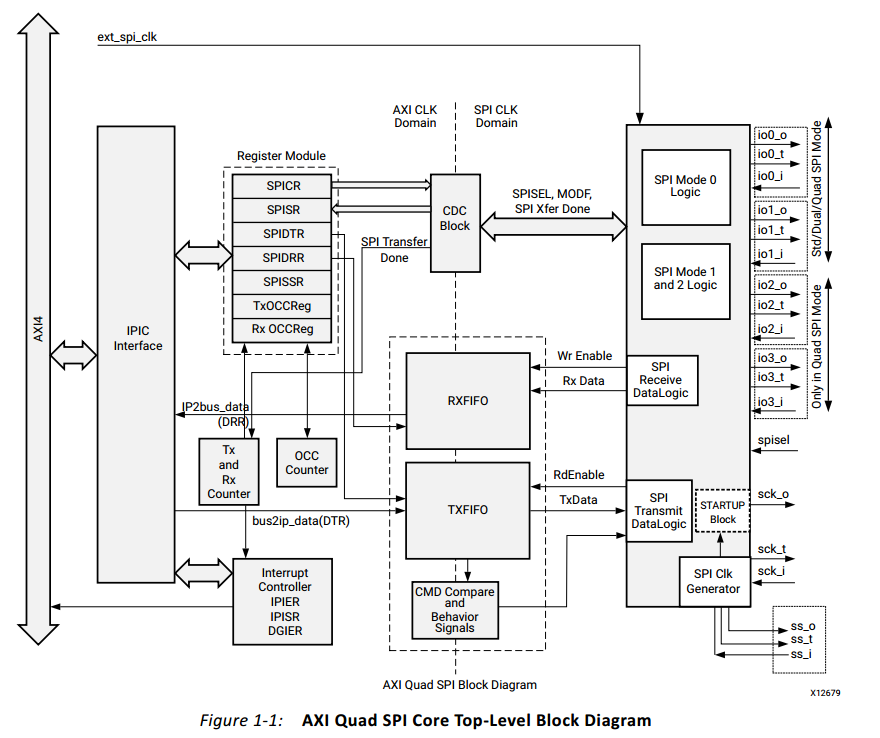

*可配置的AXI4接口

*支持对DRR/DTR FIFO的突发操作;

*支持可配置的XIP模式操作;

*支持AXI4-Lite或者AXI4接口连接的32bit Slave;

*支持可配置的SPI模式:标准、双、四模式;

*可编程的SPI时钟相位和极性;

*可配置的FIFO深度,16、256深度;对XIP模式只支持64深度;

*Configurable slave Memories in dual and quad modes are: Mixed,Micro,Winbond,and Spansion;

*AXI 接口选项:

XIP 模式: 使能AXI4 和 AXI4-Lite接口,地址模式可以选择24bit和32bit;

Performance 模式:使能AXI4接口;使用AXI4接口可以在核的发送和接收FIFO地址处启用突发功能。当不使能performance模式时,AXI4-Lite将被使用。

*SPI 选项

模式可以选择: standard/dual/quad

Transacton Width: 8/16/32

频率比率:2~2048, 代表了SPI的sck = ext_spi_clk/ratio ;

NO. of Slave: 代表了slave的个数;1~32;

*寄存器:

AXI4-Lite写访问寄存器由32位AXI写数据(* _wdata)信号更新,不受AXI写数据选通(* _wstrb)信号的影响。对于写入,AXI写地址有效(* _awvalid)和AXI写数据有效(* _wvalid)信号需要同时有效。

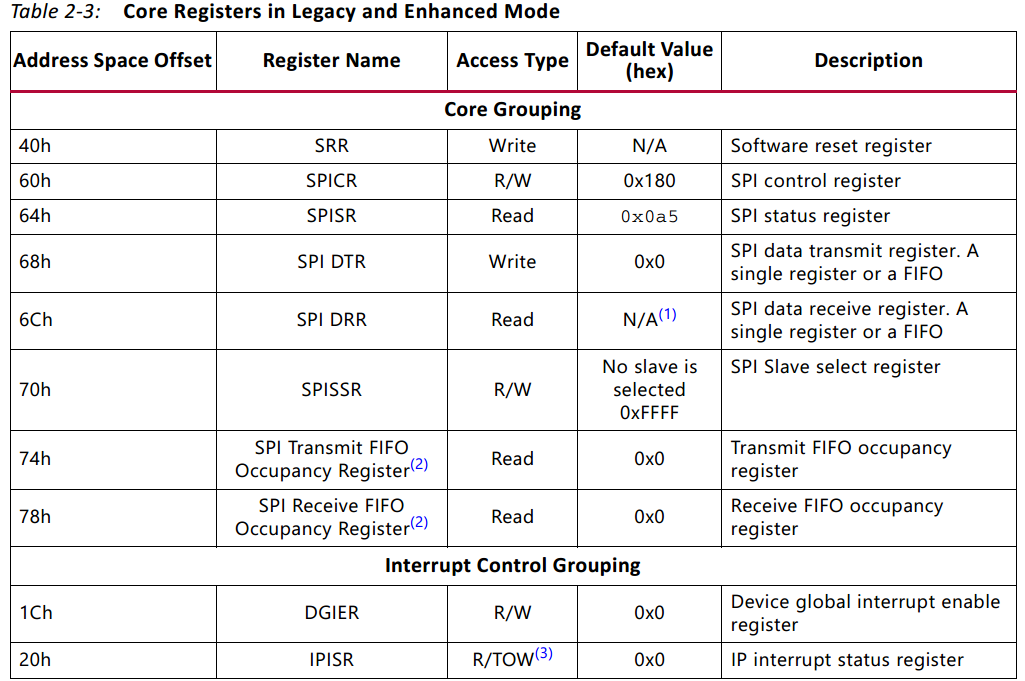

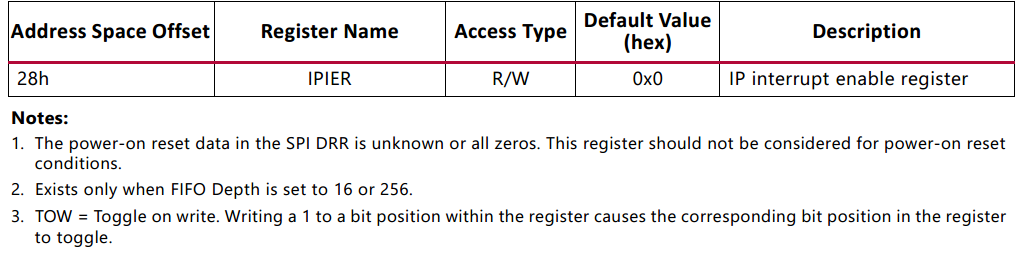

表2-3显示了适用的寄存器集,无论是否使能Performance Mode,或禁止XIP模式。应单独访问某些AXI Quad SPI内核寄存器。这些寄存器是可配置的,可通过AXI4-Lite接口或AXI4接口(增强模式)访问。 所有寄存器都以32位的形式访问。

如果访问不存在的寄存器,它们将返回OKAY响应。 这些寄存器的读取返回0,写入没有任何影响。

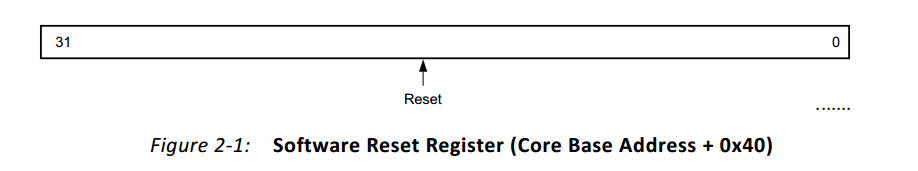

*SPISRR: 写入0xA,进行软件复位;

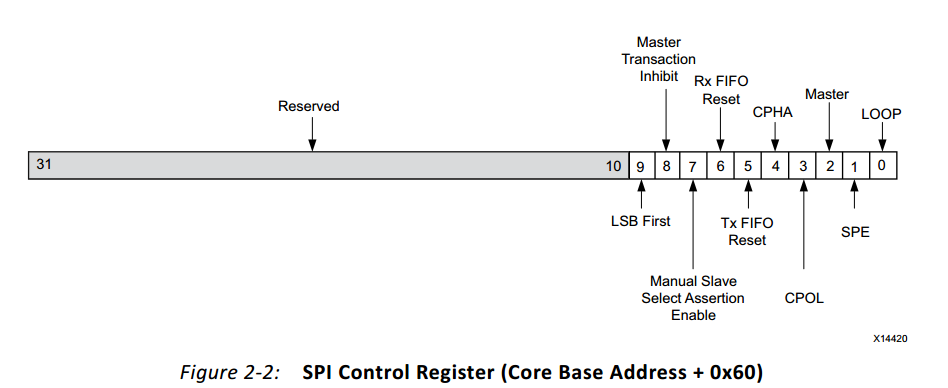

*SPICR

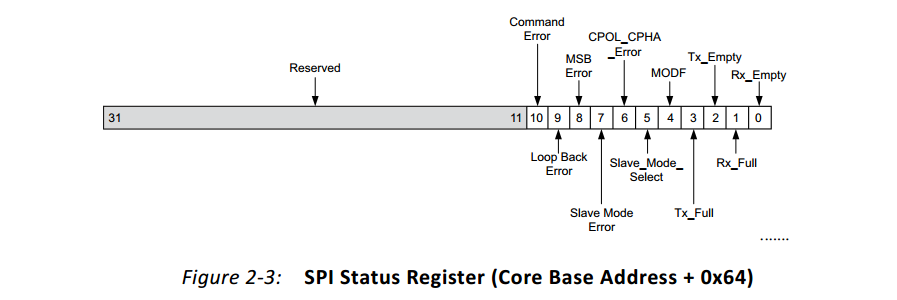

*SPISR

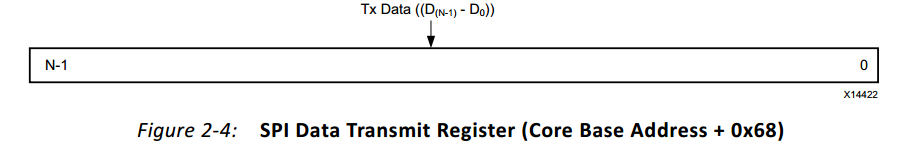

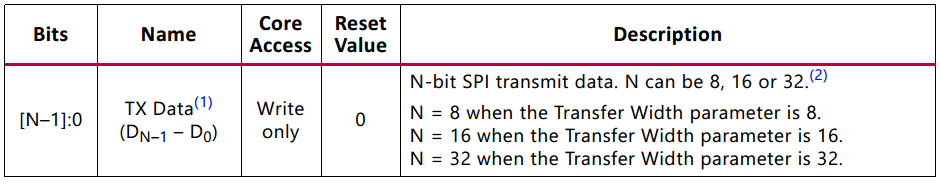

*SPI DTR:

After the SPE bit is set to 1 in master mode or spisel is active in the slave mode,the data is transferred from the SPI DTR to the shift register.

1. DN-1位始终表示MSB位,与LSB优先或MSB优先传输选择无关。 当传输宽度参数为8或16时,未使用的高位((AXI数据宽度-1)到N)被保留。

2.在标准SPI模式下,根据内核配置,该寄存器的宽度可以是8或16或32。 在双通道或四通道SPI模式下,该寄存器为8位宽。

*SPI DRR

SPI数据接收寄存器(SPI DRR)用于读取从SPI总线接收的数据。 这是一个双缓冲寄存器。 每次完成传输后,接收的数据将被放入该寄存器中。 SPI架构没有为从设备提供任何方法来限制总线上的流量; 因此,只有在最后一次SPI传输之前读取了SPI DRR时,才会在每次完成的事务后更新SPI DRR。如果未读取SPI DRR且已满,则最近传输的数据将丢失并发生接收溢出中断。 主SPI设备也会出现相同的情况。

在标准模式下,读取空DRR FIFO会返回从错误。

*SPISSR:

SPI从选择寄存器(SPISSR)包含一个长度为N的低有效,one-hot编码的slave选择矢量SS,其中N是从机数。

SS向量占据寄存器的最右位。 最多将一位置为低电平。 该位表示本地主站与之通信的从站。 SPISSR中的位分配如图2-6所示,并在表2-9中进行了描述

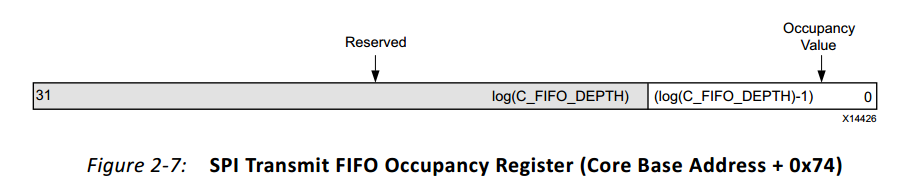

*TX_FIFO_OCY:

仅当AXI Quad SPI内核配置了FIFO(FIFO深度= 16或256)时,才会出现SPI发送FIFO占用寄存器(TX_FIFO_OCY)。 如果它存在且发送FIFO不为空,则寄存器包含一个四位右对齐值,该值比FIFO中的元素数少一(占用率减1)。

该寄存器是只读的。 写入时,或当FIFO为空时读取,寄存器内容不受影响。 确定发送FIFO为空/满的唯一可靠方法是读取SPI状态寄存器中的Tx_Empty / Tx_Full状态位或中断状态寄存器中的DTR空位。

*RX_FIFO_OCY:

仅当AXI Quad SPI内核配置了FIFO(FIFO深度= 16或256)时,才会出现SPI接收FIFO占用寄存器(RX_FIFO_OCY)。 如果寄存器存在且接收FIFO不为空,则寄存器包含一个四位右对齐值,该值比FIFO中的元素数少一(占用率减1)。

该寄存器是只读的。 写入(或FIFO为空时的读取)不会影响寄存器内容。 确定接收FIFO为空/满的唯一可靠方法是读取SPI状态寄存器中的Rx_Empty / Rx_Full状态位。

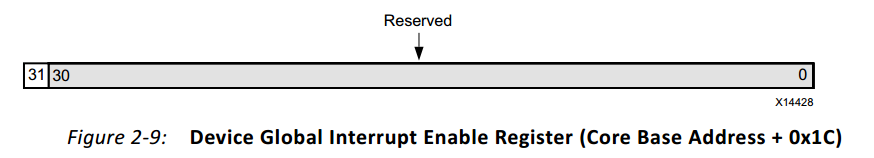

*DGIER

默认[31]=0,全局使能处于disable状态;

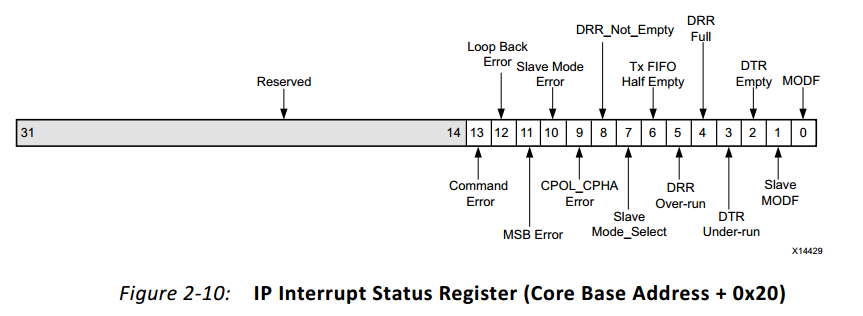

*IPISR

根据系统是否配置了FIFO,以及是否配置为主模式或从模式,最多可以有14种独特的中断条件。

没有FIFO的系统有七个中断。 中断控制器中的32位中断状态寄存器可以独立使能每个中断。 IP中断状态寄存器(IPISR)收集所有中断事件。 中断寄存器是一个读/写切换寄存器。 将1写入寄存器中的位位置会导致相应的位切换。 所有寄存器位在复位时清零。

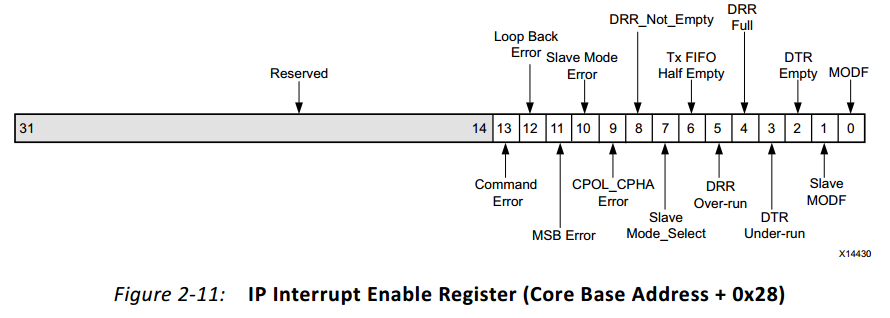

*IPIER

中断允许寄存器(IPIER)寄存器允许系统中断输出有效。 如果IPISR寄存器中的有效位对应于IPIER寄存器中的使能位,则会产生该中断。 IPIER寄存器对IPISR的每个定义位都有一个使能位。 所有位在复位时清零。

* 编程顺序:

写使能命令顺序:

1.通过置位SPICR(60h)的主禁止位来禁用主事务,并通过SPICR复位RX和TX FIFO。

示例:将0x1E6写入SPICR

2.通过将0x06写入SPIDTR来发出write enable命令。

3.通过向SPISSR(70h)写入0x00来发出芯片选择。

4.通过置低SPICR主禁止位来使能主事务。

5.通过将0x01写入SPISSR来置低片选。

6.通过置位SPICR主禁止位来禁用主事务。

擦除命令序列:

1.通过SPICR复位RX和TX FIFO。

2.将扇区擦除命令(a)发送到SPIDTR以擦除闪存扇区地址后面的任何特定扇区或发出批量擦除命令(a)擦除整个闪存

然后是flash基地址。

示例:将0xD8写入SPIDTR

3.通过向SPISSR写入0x00来发出芯片选择。

4.通过置低SPICR主禁止位来使能主事务。

5.通过将0x01写入SPISSR来置低片选。

6.通过置位SPICR主禁止位来禁用主事务。

写数据命令序列:

1.通过SPICR复位RX和TX FIFO。

2.将写入数据命令(a)(b)发送到SPIDTR,以将数据写入任何特定扇区

其次是闪存扇区地址。

3.使用要写入闪存的数据填充SPIDTR; 最大数据大小取决于

配置的QSPI FIFO大小。

4.通过向SPISSR写入0x00来发出芯片选择。

5.通过置低SPICR主禁止位来使能主事务。

6.通过将0x01写入SPISSR来置低片选。

7.通过置位SPICR主禁止位来禁用主事务。

读取数据命令序列:

1.通过SPICR复位RX和TX FIFO。

2.将读取数据命令(a)(b)发送到SPIDTR以从任何特定扇区读取数据

其次是闪存扇区地址。

3.使用虚拟数据填充SPIDTR以从闪存中读取所需数据。

4.通过向SPISSR(70h)写入0x00来发出芯片选择。

5.通过置低SPICR主禁止位来使能主事务。

6.通过将0x01写入SPISSR来置低片选。

7.通过置位SPICR主禁止位来禁用主事务

8.读取SPIDRR,以获取从SPI总线接收的读取数据。

a.参见相应的SPI Slave(闪存)数据表,了解要发出的命令。

b.写入/读取命令因使用的模式(标准/双/四)而异。

推荐:https://www.cnblogs.com/chensimin1990/p/8526497.html#4105474

浙公网安备 33010602011771号

浙公网安备 33010602011771号