μC/OS-II在Microblaze上的移植与使用专题--“安富利杯”赛灵思FPGA设计技巧与应用创新博文大赛参赛作品

随着集成电路设计与制造技术的发展,FPGA芯片的容量越来越大、性能越来越高,用FPGA构建片上系统成为现实,基于FPGA的嵌入式系统与SOPC(System On a Programmable Chip)设计技术将逐渐成为系统设计的主流技术,正获得越来越广泛地研究。Microblaze是Xilinx公司一款针对FPGA器件进行了优化设计的软处理器核,有不错的性能且价格低廉,且支持Xilinx全系列的FPGA器件,应该有着广阔的发展前景。μC/OS-II是Jean Labrosse先生于1998年推出的一个优秀的开放源码的实时操作系统,具有移植方便、执行效率高、占用空间小、实时性强和可靠性高等优点。采用μC/OS-II+Microblaze的应用平台对中小嵌入式系统应用来说是十分适合的。本文基于μC/OS-II在Microblaze上的移植与基于该系统的应用研究,记录移植和使用过程的心得、体会,内容可能会有些零散,希望对有类似应用的朋友有些帮助,也欢迎大家来交流与讨论。

一、主要参考资料

①μC/OS-II学习主要参考邵贝贝教授译的《嵌入式实时操作系统μC/OS-II(第2版)》

下面是CHINA-PUB的介绍http://www.china-pub.com/12618

网上也有该书第一版的电子书可以找来学习。

② Micrium公司的Micrium-uCOS-II-V286.ZIP,包括代码与文档,可以从

www.micrium.com获得。

③ Micrium公司的μC/OS-II and the Xilinx MicroBlaze Processor Application Note

可以从www.micrium.com获得。

④ Xilinx公司EDK相关文档:http://www.xilinx.com/ise/embedded/edk_docs.htm

⑤ ISE、EDK软件的帮助文档,包括MicroBlaze Processor Reference Guide (mb_ref_guide.pdf)。

⑥ EDK的基本使用可以参考:Xilinx官方的6个EDK实验(中文版).pdf

百度文库上有http://wenku.baidu.com/view/e92e71d184254b35eefd3425.html

二、操作系统的配置选项问题

在进行Software Platform配置时,一般安装了EDK软件后,操作系统与库设置时可选择的标准选项只有两个:Standalone和Xilkernel。 Standalone适合不带操作系统的应用,只提供基本的设置中断,配置Cache等功能,Xilkernel是赛灵思提供的一个嵌入式内核。为了能在设置操作系统时可以选择μC/OS-II,根据赛灵思文档描述,EDK软件的操作系统配置选项其实是通过扫描bsp目录得到,扫描顺序是:

1. 当前工作目录,即工程目录。

2.调用Libgen时用 –lp选项指定的目录。

3.EDK安装目录下的 EDK\sw\lib\bsp目录。

所以我们如果要在所有新建工程时都有μC/OS-II选项,可以把Micrium公司提供的移植包AN-1013.zip里的BSP目录下内容COPY到EDK安装目录下的 EDK\sw\lib\bsp目录下就可。如果仅仅是当前工程用的话,把它COPY到工程目录就可以了。

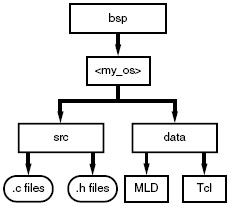

bsp目录有特定的结构,如下图示:

bsp目录下my_os指定我们用的操作系统,这里为uCOS-II_v2_86_a。

my_os目录下面的src目录包括所有的源文件和头文件,data目录包括两个文件: mld文件和tcl文件。mld文件用来定制操作系统的软件库与板级支持包(BSP:Board

Support Packages),tcl文件为产生软件库和BSP包的脚本文件。

三、Microblaze的总线接口

Microblaze处理器提供了以下的总线接口和外部进行通信

① PLB总线:32比特版本的PLB V4.6总线可以支持多个主设备和从设备连接,提供高效率的传输性能,适合于数据传输密集性应用。

② OPB总线:外设总线,适用于低速设备的连接。

③ LMB总线:本地存储总线,用来高速连接片内的 BLOCK RAM的同步总线,使用最少数量的控制信号和在一个时钟周期内存取BLOCK RAM的简单协议。LMB总线的读写时序和BLOCK RAM的读写时序是一样的,且所有的LMB信号是高电平有效。

④ FSL总线:快速单工链接接口,提供一种效率高、占用资源少的单向的点对点数据流传输。最新的Microblaze 7.2处理器最多支持16个FSL接口,每个FSL接口有一个输入和一个输出接口组成。FSL总线的读写操作通过Microblaze的PUT和GET指令完成的, 分为两种模式: 阻塞模式和非阻塞模式。阻塞模式是指写操作时如fifo满或读操作时如fifo空时处理器会等待,只到fifo不满而写操作成功或fifo非空而读操作成功。非阻塞模式读写操作不成功时处理器不会等待,但会在MSR中设置进位信号。

⑤ XCL总线:Xilinx 缓存链路接口,用在需要使用外部存储时,提供一种高效和延时最小的方案,XCL接口设计为直接通过内嵌的FSL接口连接到内存控制器。

⑥ Debug和Trace:用于基于JTAG的软件调试模块DMD(

Xilinx Microprocessor Debug Module)。

对于代码量不大的应用来说,代码和数据都可以放在BLOCK RAM内而使用LMB总线比较方便,如果需要外扩存储器时,就要使用XCL总线来提供访问外部存储器的效率。外设连接一般用到PLB或OPB或FSL总线。像LMB,FSL总线协议是比较简单的,但使用也是比较多的,具体读写时序可以参考MicroBlaze Processor Reference Guide的第2章信号接口描述,而PLB总线可以参考IBM 128-Bit Processor Local Bus Architectural Specification (v4.6)。在EDK\hw安装目录下的EDKIP核内有相应的IP说明文档参考。

-待续-

此文为“安富利杯”赛灵思FPGA设计技巧与应用创新博文大赛参赛作品

浙公网安备 33010602011771号

浙公网安备 33010602011771号