MSC-51单片机常用I/O接口的设计

I/O接口拓展概述

MCS-51单片机具有4个并行8位I/O 口(即P0、P1、P2、P3),原理上这4个I/O 口均可用作双向并行I/O接口,但在实际应用中,只有当单片机在不使用外部扩展时,才允许这4个I/O 口作为用户I/O使用,但是这种情况在单片机应用系统开发中几乎是不可能的。

在单片机应用系统开发中,需要实现单片机对多种外设(如键盘、显示器等)进行控制,I/O接口是MCS-51与外设交换数字信息的桥梁,也属于系统扩展的一部分。

在这种情况下,可提供给用户使用的I/O 口只有P1 口和部分P3 口及作为数据总线用的P0 口,而P3 口在应用系统设计中常使用其第二功能。因此,在单片机的I/O 口不够用的情况下,可以借助外部器件对I/O 口进行扩展。

I/O接口的功能

I/O接口电路应满足以下要求:

- 实现和不同外设的速度匹配。大多数外设的速度很慢,无法和微秒量级的单片机速度相比。单片机只有在确认外设已为数据传送做好准备的前提下才能进行I/O操作。想知道外设是否准备好,需I/O接口电路与外设之间传送状态信息。

- 输出数据锁存。由于单片机工作速度快,数据在数据总线上保留的时间十分短暂,无法满足慢速外设的数据接收。I/O电路应具有数据锁存器,以保证接收设备接收。

- 输入数据三态缓冲。输入设备向单片机输入数据时,但数据总线上面可能“挂”有多个数据源,为不发生冲突,只允许当前时刻正在进行数据传送的数据源使用数据总线,其余的数据源应处于隔离状态。

I/O端口的编址

在学习I/O端口的编址方法之前,首先要明确接口和端口的概念。在进行单片机应用系统设计时,通常需要多种外设,而这些外设要想接入,就需要用自己的接口和总线上的某个匹配接口匹配对接,这种单片机与外部设备之间的I/O接口芯片就称为接口。

而单片机在与外设进行通信时,要发数据到某个外设或从外设读取信息,其实就是从对应的接口电路中多个寄存器或缓冲器获取信息,这种具有端口地址的寄存器或缓冲器就称为端口,简称I/O 口。对一个系统而言,通常会有多个外设,每个外设的接电路中又会有多个端口,如数据口、命令口、状态口对于单片机而言,访问外部设备就是访问相关的端口,而所有的信息会由接口转给外设。

对一个系统而言,通常会有多个外设,每个外设的接口电路中又会有多个端口,每个端口都需要一个地址,为每个端口标识一个具体的地址值,是系统必须解决的事,这就需要进行I/O端口的编址。

I/O端口编址分为两种方式:独立编址与统一编址。

- 独立编址方式

I/O寄存器地址空间和存储器地址空间分开编址,但需一套专门的读写I/O的指令和控制信号。 - 统一编址方式

I/O寄存器与数据存储器单元同等对待,统一编址。不需要专门的I/O指令,直接使用访问数据存储器的指令进行I/O操作,简单、方便且功能强。

MCS-51单片机使用统一编址的方式 每一接口芯片中的一个功能寄存器(端口)的地址就相当于一个RAM单元。

I/O数据的传送方式

为实现和不同的外设的速度匹配,I/O接口必须根据不同外设选择恰当的I/O数据传送方式。

I/O数据传送的几种方式是:同步传送、异步传送和中断传送。

- 同步传送方式(无条件传送)

当外设速度和单片机的速度相比拟时,常釆用同步传送方式,最典型的同步传送就是单片机和外部数据存储器之间的数据传送。 - 异步传送方式(条件传送)

査询外设“准备好”后,再进行数据传送。

优点:通用性好,硬件连线和査询程序十分简单。

缺点:效率不高。

为提高效率,通常采用中断传送方式。 - 中断传送方式

外设准备好后,发中断请求,单片机进入与外设数据传送的中断服务程序,进行数据的传送。中断服务完成后又返回主程序继续执行,工作效率高。

I/O接口电路

常用的外围I/O接口芯片如下所述。

- 82C55:可编程的通用并行接口电路(3个8位I/O 口)。

- 8155H:可编程的IO/RAM扩展接口电路(2个8位I/O 口、1个6位I/O 口、256个RAM字节单元、1个14位的减法定时/计数器)。

这些接口引路芯片都可与MCS-51单片机直接连接,接口逻辑十分简单。此外,74LS系列的TTL电路也可以作为MCS-51单片机的扩展I/O 口,如74LS244、74LS273等。

MCS-51单片机与可编程并行I/O芯片82C55的接口设计

82C55芯片简介

82C55可编程并行输入/输出接口芯片是Intel公司生产的标准外围接口电路。它釆用NMOS工艺制造,用单一+5V电源供电,具有40个引脚,采用双列直插式封装。它有A、B、C三不端口共24条I/O线,可以通过编程的方法来设定端口的各种I/O功能。由于它功能强,又能方便地与各种微机系统相接,而且在连接外部设备时,通常不需要再附加外部电路,所以得到了广泛的应用。

82C55内部结构

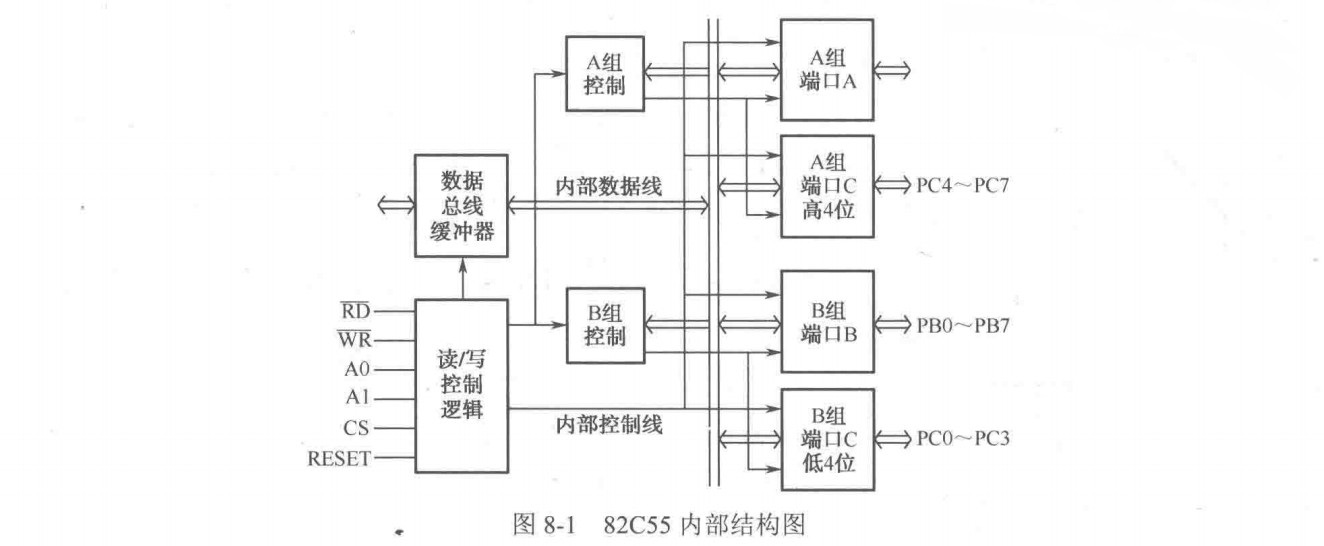

内部结构如图8-1所示。

- 端口 A、B、C

PA 口:数据输出锁存和缓冲;数据输入锁存。

PB 口:数据输出锁存和缓冲;数据输入缓冲。

PC 口:数据输出锁存;数据输入缓冲。PC 口可在软件的控制下,分为两个4位端口,作为PA 口、PB 口选通方式操作时的状态控制信号。 ’ - A组和B组控制电路

A组:PA 口和PC 口的上半部(PC7〜PC4);

B组:PB 口和PC 口的下半部(PC3〜PCO),可根据“命令字”对PC 口按位置1或清0。 - 数据总线缓冲器

数据总线缓冲器是一个三态双向8位缓冲器,作为82C55与单片机数据线之间的接口,传送数据、指令、控制命令及外部状态信息。 - 读/写控制逻辑电路线

该电路接收CPU发来的控制信号、RESET信号及地址信号Al、A0等,对端口进行读/写。

引脚说明

82C55具有40个引脚,采用双列直插式封装。

D7-D0:三态双向数据线,与单片机数据总线连接。

CS:片选信号线,低电平有效,表示本芯片被选中。

RD:读出信号线,控制82C55中数据的读出。

WR:写入信号线,控制向82C55数据的写入。

Vcc: +5V 电源。

PA7〜PA0: A 口输入/输出线。

PB7-PB0: B 口输入/输出线。

PC7-PC0: C 口输入/输出线。

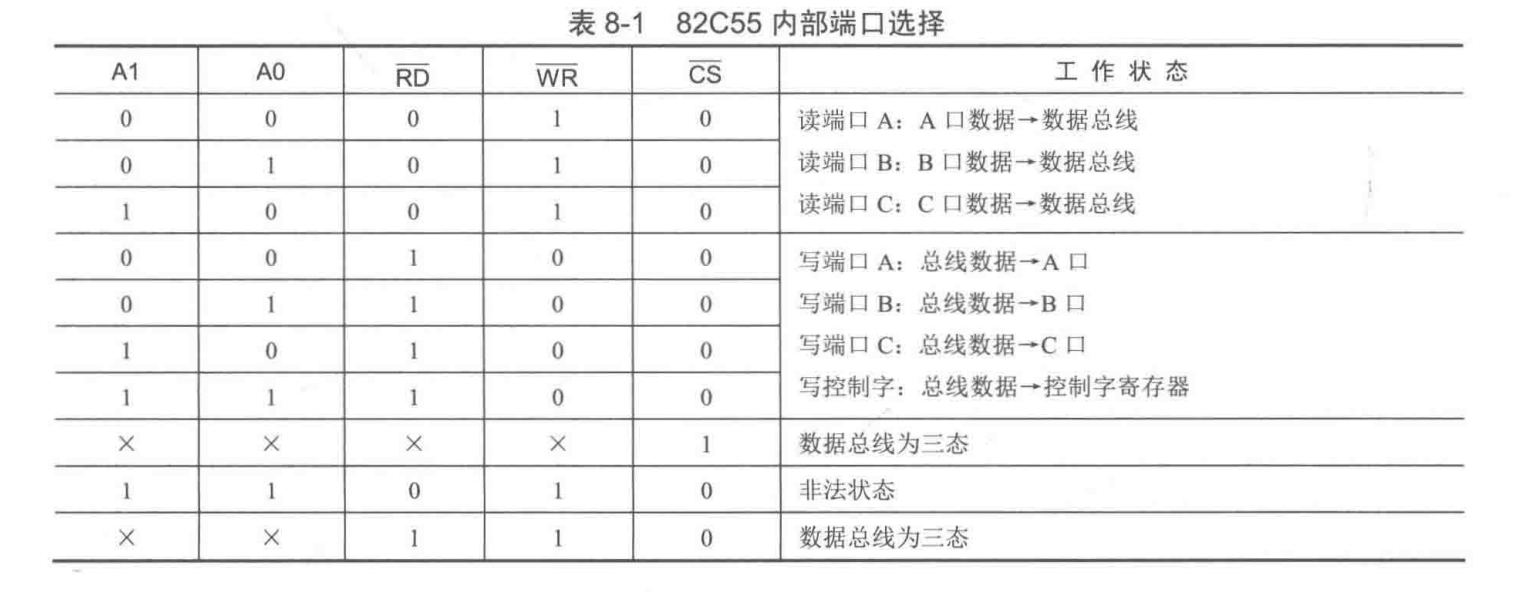

A1、A0:地址线,用来选择82C55内部的4个端口。系如表8-1所示。

工作方式选择控制字及端口PC置位/复位控制字

82C55有3种工作方式:

- 方式0:基本输入/输出;

- 方式1:选通输入/输出;

- 方式2:双向传送(仅A 口有)。

这3种工作方式由方式控制字来决定。

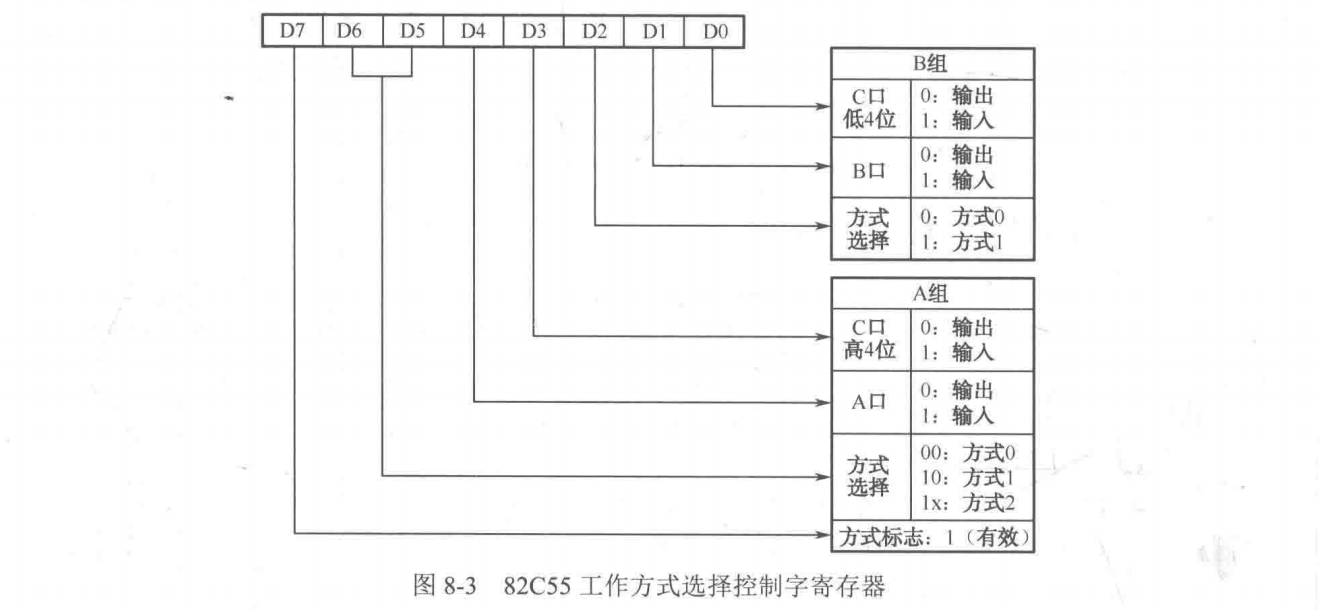

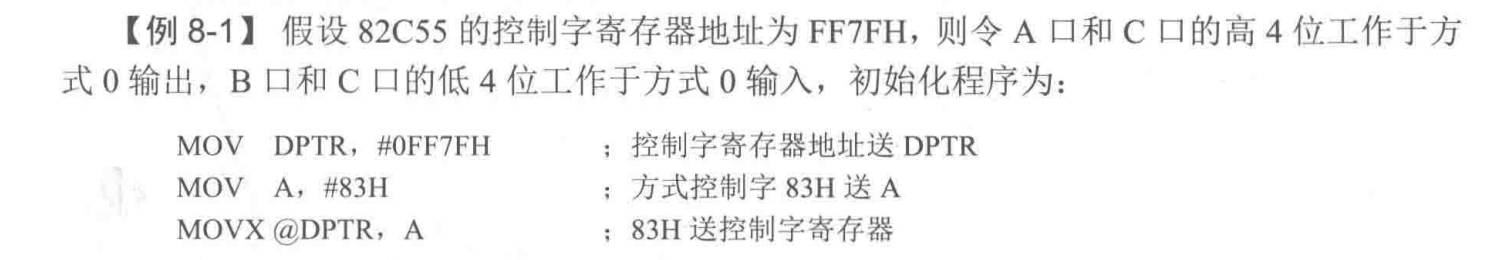

工作方式选择控制字

82C55的工作方式选择控制字是用来设定通道的工作方式及数据传输方向的,其内部各位的含义如图8-3所示。

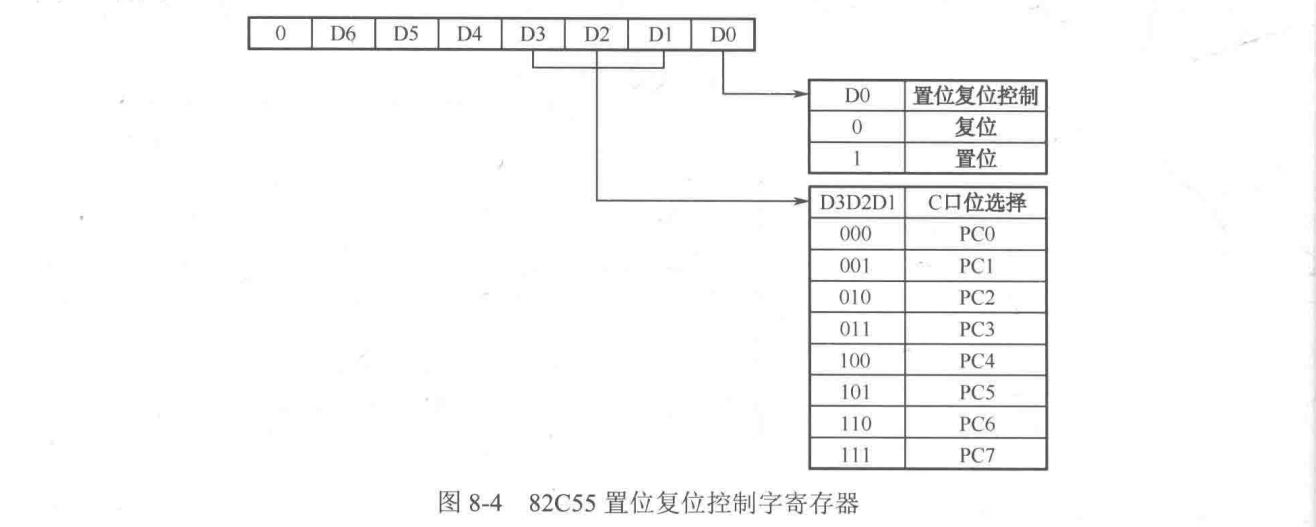

端口 PC置位复位控制字

82C55的端口PC置位复位控制字可以决定PC 口的复位、置位状态,其内部各位的含义如图8-4所示。

82C55的3种工作方式

方式0:基本的输入/输出方式

在此种工作方式下,MCS-51可对82C55进行数据的无条件传送。3个数据端口 A、B、C(C分为两个4位),通过方式选择控制字可任意选择其为输入或输出口。特别是归同一组的两个端口也可分别定位为输入口或输出口。CPU只要对82C55执行I/O指令即可输入/输出数据。方式0的主要特点如下:

- 具有两个8位端口(A、B)和两个4位端口(C的上半部分和下半部分)。

- 任一个端口都可以设定为输入或输出,各端口的输入、输出可构成16种组合。

- 数据输出锁存,输入不锁存。

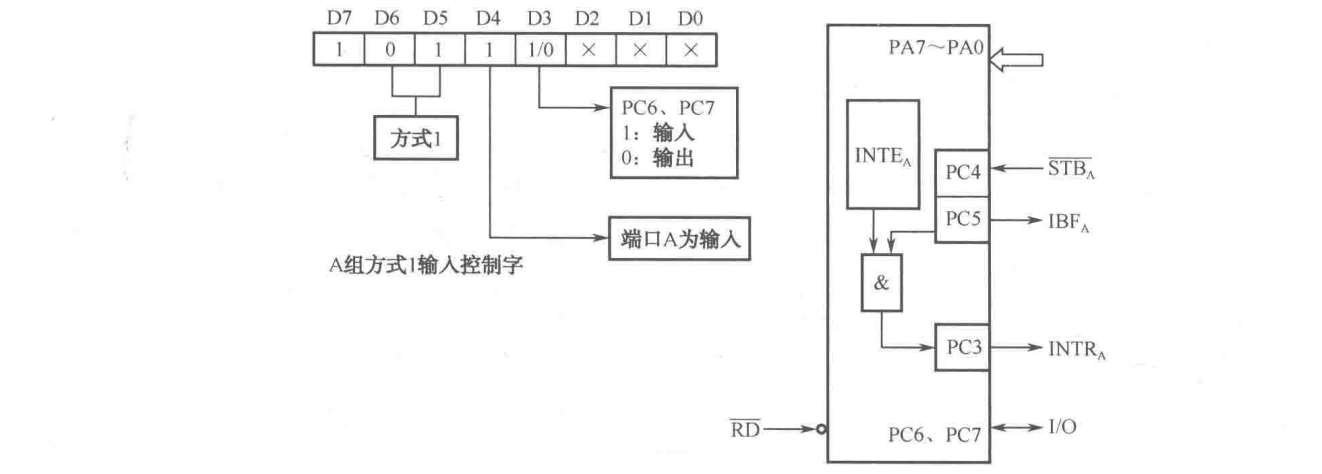

方式1:选通输入/输出工作方式

方式1是一种选通输入/输出方式,在此种方式下,82C55的A 口、B 口用于与外设进行数据通信时,必须使用C 口作为A 口、B 口的联络线,也就是通过C 口为A 口、B 口提供选通信号、应答信号,以实现中断方式传输I/O数据。

方式1输入

82C55 工作方式1下,端口 A、B用于输入的方式控制字以及联络信号如图8-4所示。

当82C55工作于方式1输入状态下,控制信号STB与IBF构成了一对应答信号联络线,各个联艷号线功能如下:

STB——选通信号,低电平有效。由外设提供的输入信号,当其有效时,将输入设备送来的数据锁存至82C55的输入锁存器。

IBF——输入缓冲器满信号,高电平有效。82C55输出的联络信号,当其有效时,表示数据已锁存在输入锁存器。

INTE——中断请求信号,高电平有效。

82C55输出的信号,可用于向CPU提出中断请求,要求CPU读取外设数据。

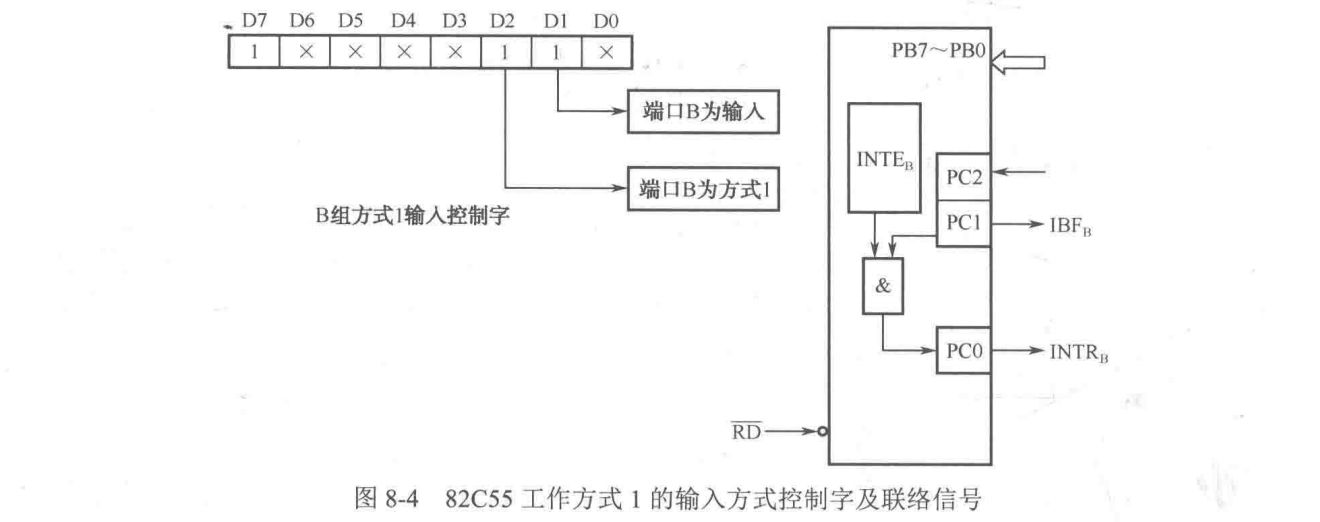

下面以A口的方式1输入为例,介绍方式1输入的工作过程以及各控制信号联络线的功能。

如图8-5所示,MCS-51单片机通过82C55扩展一外部设备,该外设通过I/O 口将外部信号读入,并与82C55的PC4、PC5引脚形成应答信号联络线,并通过数据总线将外部设备的数据传输到单片机中,具体工作过程如下:

- 当外设的数据已经送到PA0〜PA7上时,输入设备将自动在STBa上向82C55发送一个低电平选通信号。

- 82C55在接收到这个选通信号后,首先将PA0〜PA7上的数据锁存到A口的输入数据缓冲/锁存器上,然后将IBFa变为高电平,以通知外设,82C55己经接收到它送来的数据。

- 82C55检测到STBa上的信号由低电平变为高电平,并且IBFa为高电平以及INTEa为1时,使输出线INTRa变为高电平,向单片机发出中断信号。

- 单片机在接收到中断信号后,响应中断,并通过程序读取由数据总线上传来的数据,当读取完成后,82C55撤销INTRa上的中断请求,并使IBFa变为低电平,以通知外设可以传送下一个数据。

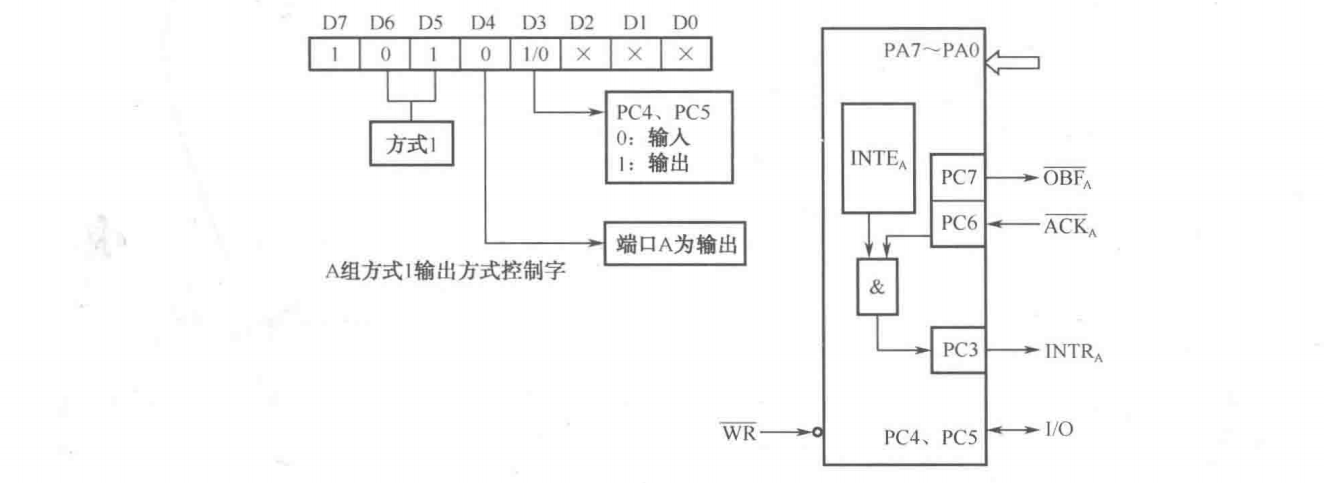

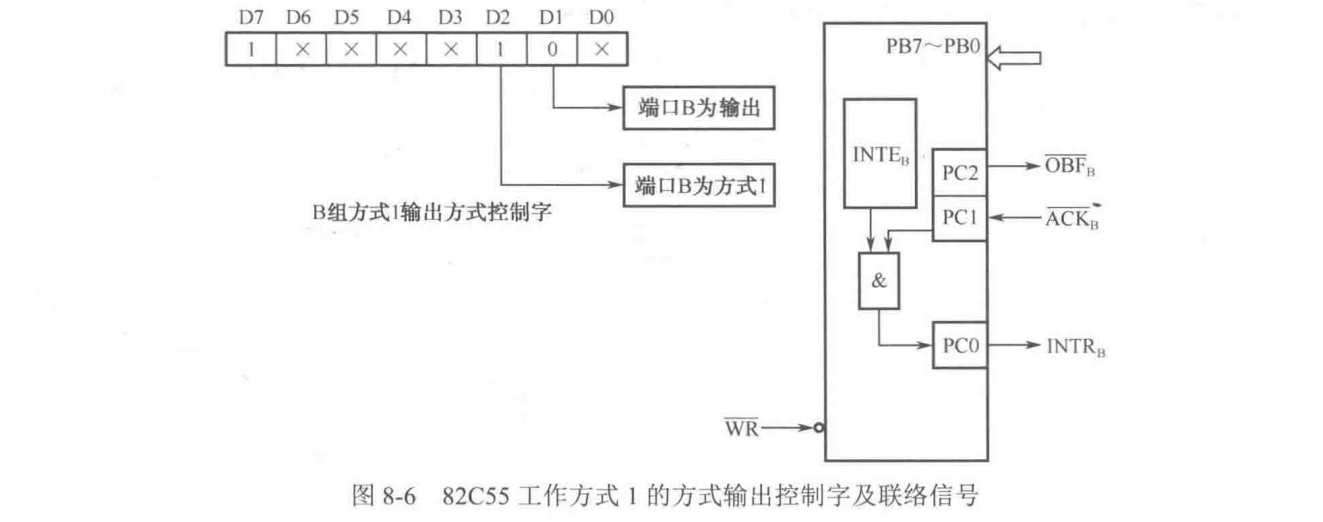

方式1输出

当82C55工作于方式1输出状态下,控制信号面OBF与ACK构成了一对应答信号联络线,各联络信号线功能如下。

OBF——输出缓冲器满信号,低有效。82C55输出给外设的一个控制信号,当其有效时,表示CPU已把数据输出给指定的端口,外设可以取走。

ACK——响应信号,低电平有效,外设的响应信号,指示82C55的端口数据已由外设接收。

INTR——中断请求信号,高有效,当输出设备已接收数据后,82C55输出此信号向CPU提出中断请求,要求CPU继续提供数据。

INTE——中断允许由PC6 (端口 A)或PC2 (端口 B)的置位/复位控制。

82C55工作方式1下,端口 A、B用于输出的方式控制字及联络信号如图8-6所示。

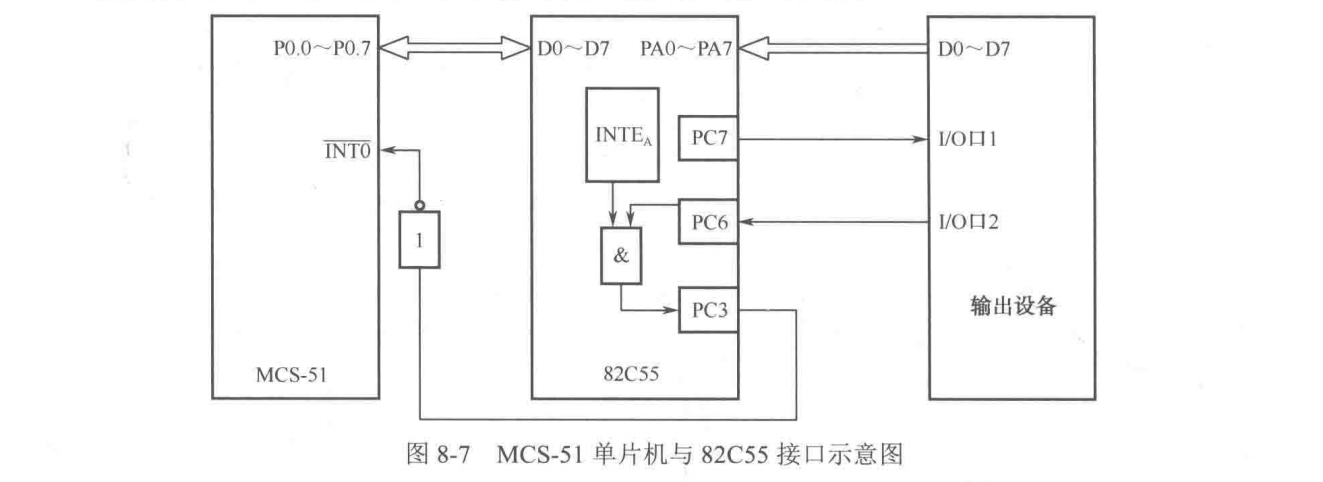

下面以A 口的方式1输出为例,介绍方式1输出的工作过程以及各控制信号联络线的功能,其电路连接示意图如图8-7所示。

如图所示,MCS-51单片机通过82C55扩展一外部设备,该外设通过I/O 口将外部信号输出,并与82C55的PC7、PC6引脚形成应答信号联络线,通过数据总线将单片机中的数据传输到外部设备,具体工作过程如下。

- 单片机通过指令将数据通过数据总线传输到82C55的A口数据输出锁存器上,82C55接收到数据后,将OBFa信号线变为低电平,以便通知外设输出数据已在A口 PA0〜PA7。

- 输出设备在接收到OBFa上的低电平后,先将PA0〜PA7的数据取走,然后将ACKa信号线变为低电平,以便通知82C55输出设备已接收到输出数据。

- 82C55从应答输入线ACKa接收到低电平后对OBFa和中断允许控制位INTEa状态进行检测,若皆为低电平,则INTRa变为高电平而向单片机发出中断请求。

- 单片机响应INTRa的中断信号后,可通过程序将下一个输出数据送到82C55的A 口的输出锁存器上。

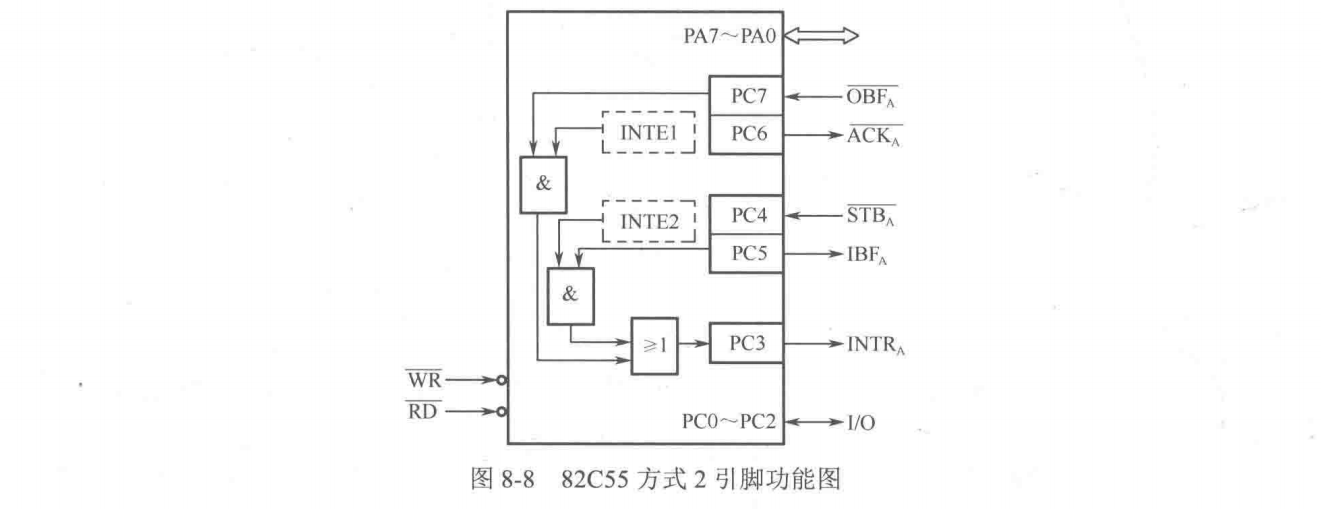

方式2:双向传输工作方式

只有A口才可设定为方式2。

82C55工作在方式2下时,其A端口(PA0〜PA7)8根口线既可以输出数据,也可以输入数据。

此外,在方式2,要用到端口C的5根口线为端口A提供相应的联络信号。当A端口(PA0〜PA7)作为输入总线使用时,其控制联络线为STBa及IBFa,其工作过程和方式1输入时相同;

当A端口(PA0〜PA7)作为输出总线使用时,其控制联络线为OBFa和ACKa,其工作过程和方式1输出时相同。82C55工作方式2下,各信号联络线如图8-8所示。

MCS-51单片机和82C55的接口设计

硬件接口电路设计

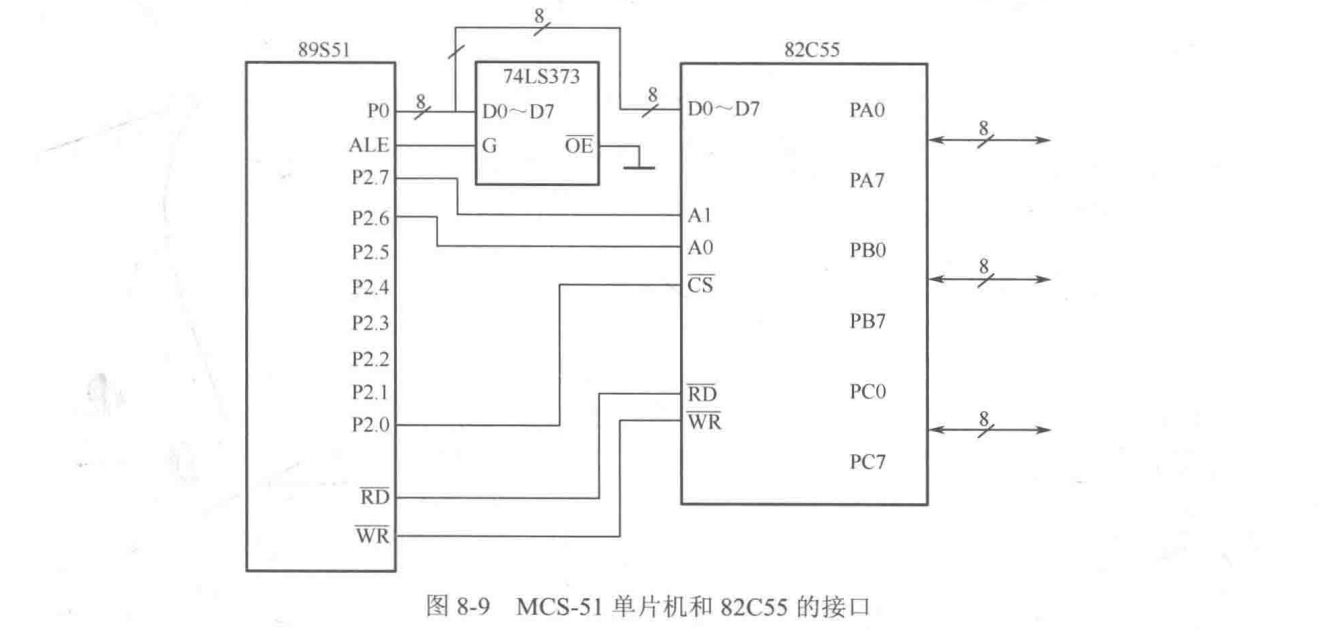

如图8-9所示为89S51单片机扩展82C55的扩展参考电路图,在扩展中,釆用总线扩展的形式,即通过地址总线确定端口地址,通过数据总线进行数据传递。

图中74LS373是地址锁存器,用来实现P0 口的地址/数据复用的锁存功能,其设计原理与在进行存储器扩展时所涉及的原理相同。

P2.0与82C55的CS引脚相连,用来进行片选;P2.6与P2.7分别与82C55的A0、A1相连,用来确定端口地址;P2 口其余引脚悬空。单片机的WR与RD引脚分别与82C55的WR和RD引脚相连,用于产生读、写信号。

82C55的端口地址确定

确定82C55的端口地址是进行82C55操作的关键步骤之一,通过得到的端口地址,就可以实现对82C55的I/O 口操作。

在图中,MCS-51单片机的P2.0引脚与82C55的CS引脚相连,P2.6与P2.7分别与82C55的A0、A1相连,想要选中需要的端口,首先要将与CS相连的P2.0置0,根据各端口地址的不同将与A0、A1相连的P2.6与P2.7按照需要置1,而其他未用到的地址线引脚置1,则根据各端口的工作状态与控制信号的关系表可以得知,82C55的端口 A、端口 B、端口 C、方式控制字端口地址分别为:

3FFFH、7FFFH、BFFFH、FFFFH

用MCS-51单片机的串行口扩展并行口

在单片机应用系统中常采用串行口对并行口进行扩展的方法,在此种方法下,釆用串行口扩展外部芯片实现串入并出或并入串出。

利用单片机串口方式0进行扩展,MCS-51串口方式0是一种移位寄存器工作方式,在这种方式下其波特率是固定的,为focs/12,数据由RXD端输入或输出,同步移位时钟由TXD输出,发送、接收数据为8位,低位在前,高位在后。

常用的并行输入串行输出的芯片有74LS165、CD4014、74HC597等;常用的串行输入并行输出的芯片有74LS164、CD4094、74HC595等。下面以74LST64、74LS165为例,对串行扩展的方法进行介绍。

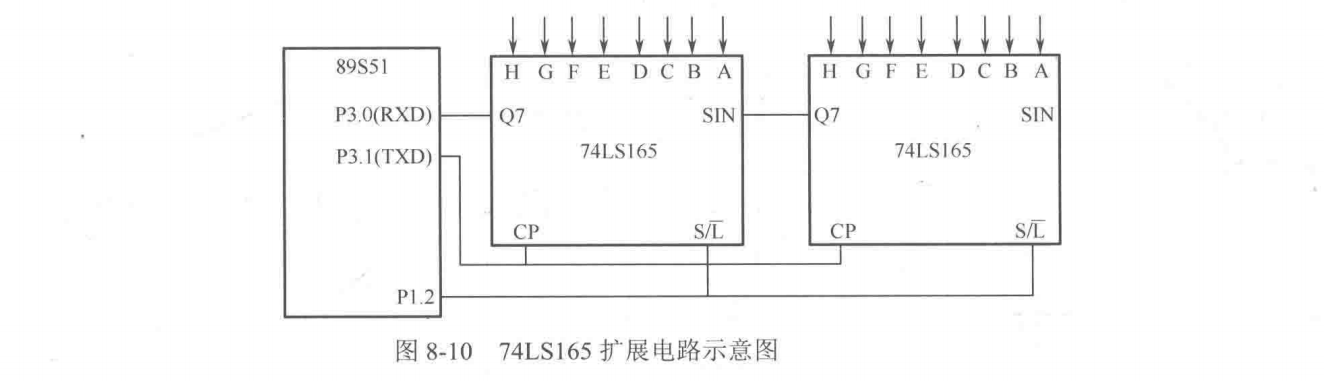

用74LS165拓展并行输入口

74LS165是8位并行输入/串行输出移位寄存器,当移、位/置入端(S/L)由高到低跳变时,并行输入端的数据被置入寄存器(并行输入);当S/L=1, 且时钟禁止端(第15脚)为低电平时,允许时钟输入,这时在时钟脉冲的作用下,数据由A到G方向移位(串行输出)。

如图8-10所示,TXD (P3.1)作为移位脉冲输出端与所有74LS165的移位脉冲输入端CP相连;RXD (P3.0)作为串行输入端与74LS165的串行输出端Q7相连;P1.2用来控制74LS165的移位与置入而同S/L相连;74LS165的时钟禁止端(15脚)接地,表示允许时钟输入。当扩展多个8位并行输入口时,两芯片的首尾(Q7与SIN)相连。

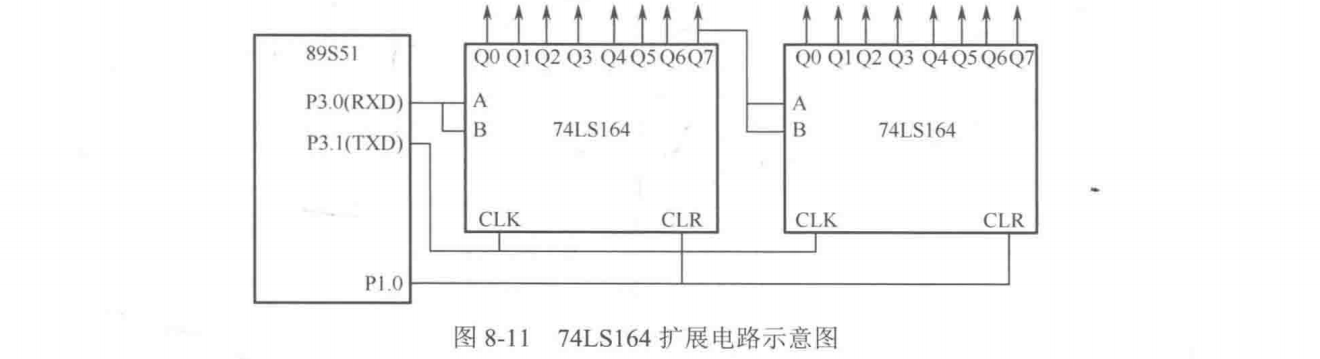

用74LS164扩展畀行输出口

74LS164是8位串行输入/并行输岀移位寄存器,在MCS-51单片机使用74LS164扩展时,单片机RXD (P3.0)引脚接74LS164芯片的串行数据输入端A、B (1、2引脚),单片机TXD (P3.1)引脚接74LS164芯片的移位脉冲输入端CLK (8引脚),在移位时钟脉冲(P3.1)的作用下,串行口发送的数据一位一位地从RXD引脚移入到74LS164中。

其接口电路如图8-11所示。

浙公网安备 33010602011771号

浙公网安备 33010602011771号