DDR2 学习笔记(一)

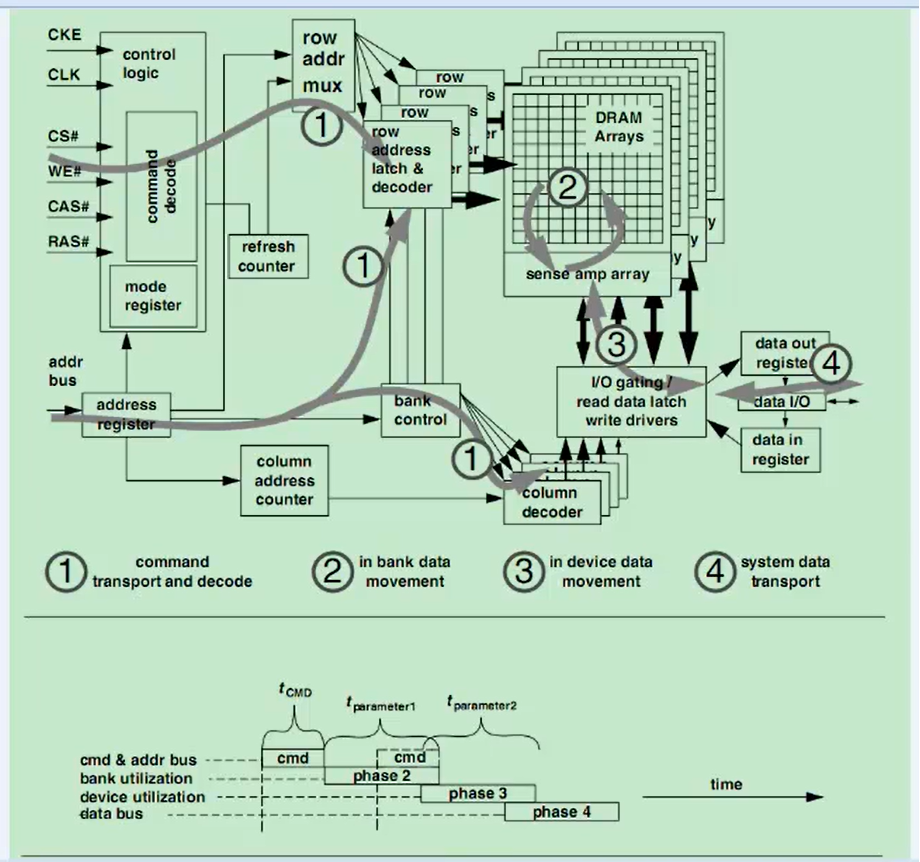

访问四大步骤:

1:命令&地址分发

2:Bank内数据操作,含预充电,行选中,放大等

3:Device数据移动,将数据由Bank移动到latch中

4:数据输出

bank和bank间是share相同的行地址的

存储单元的寻址就变成了-> bank -> row -> colum的顺序

一个bank又由多个array组成,arrays间是同时动作。

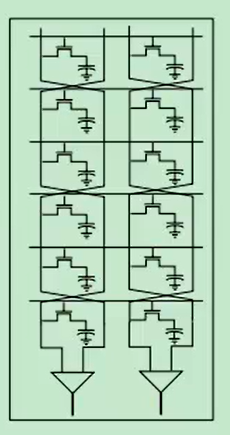

接下来重点看看bank内部array的具体操作:

每个bit都采用差分结构,提升灵敏度,降低放大器的设计难度和面积

采用版图上对称的走线减少耦合电容

vcc/2的参考电压,相当于提高mos管的基准,当bit line的信号输出时,会让ref+和ref-变为(vcc)1或者(vss)0;

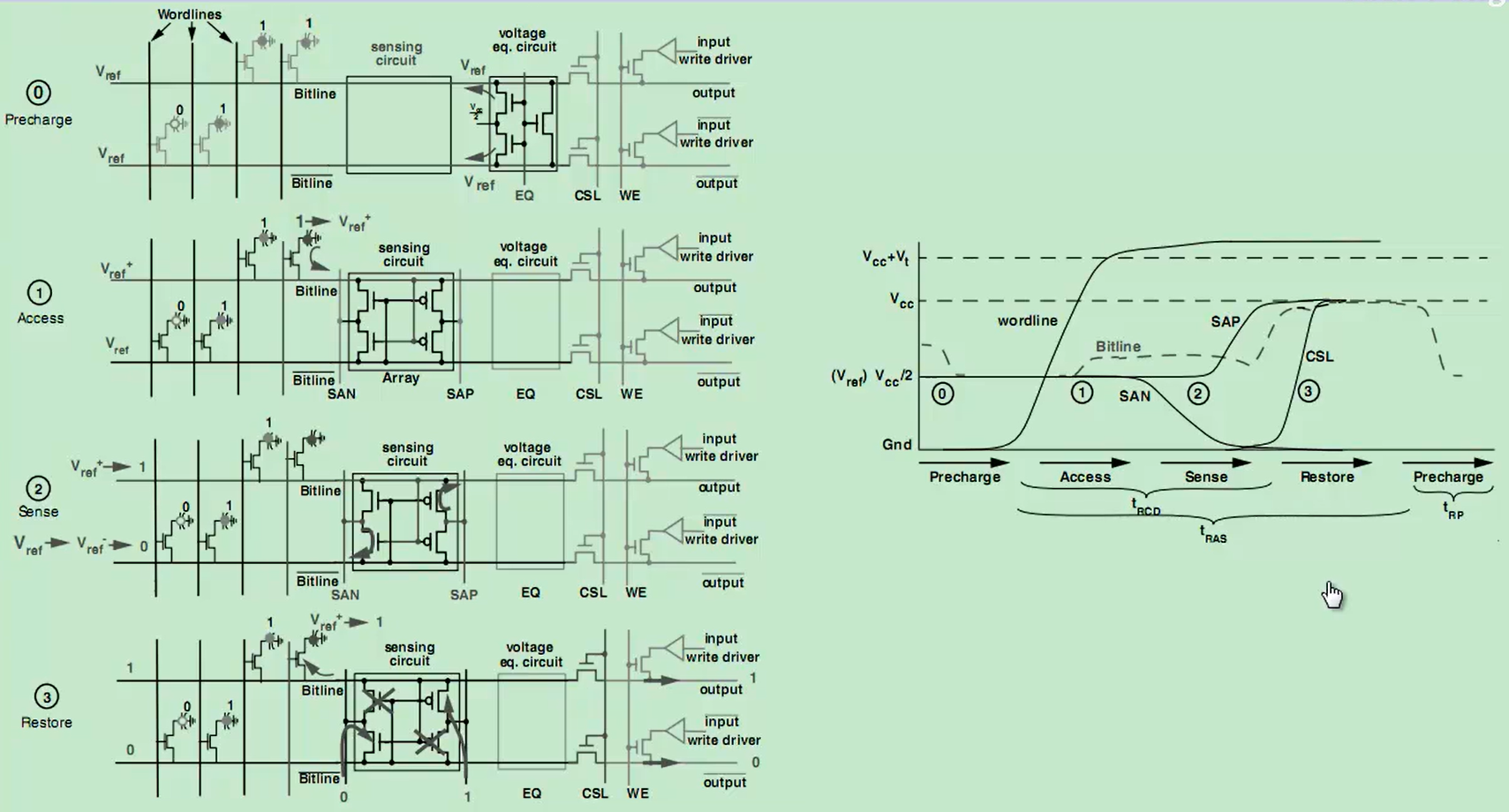

0.precharge会将bitline和~bitline都被充电到vcc/2

1.电荷被读取到bitline上

3.bitline上面微弱的信号被放大到vcc或者vss

4.将bitline的值回写到存储电荷的位置。

tRCD = row -> colum delay

tRAS = row access strobe

tRP = row precharge

tWR = write recovery

SDRAM的更新:

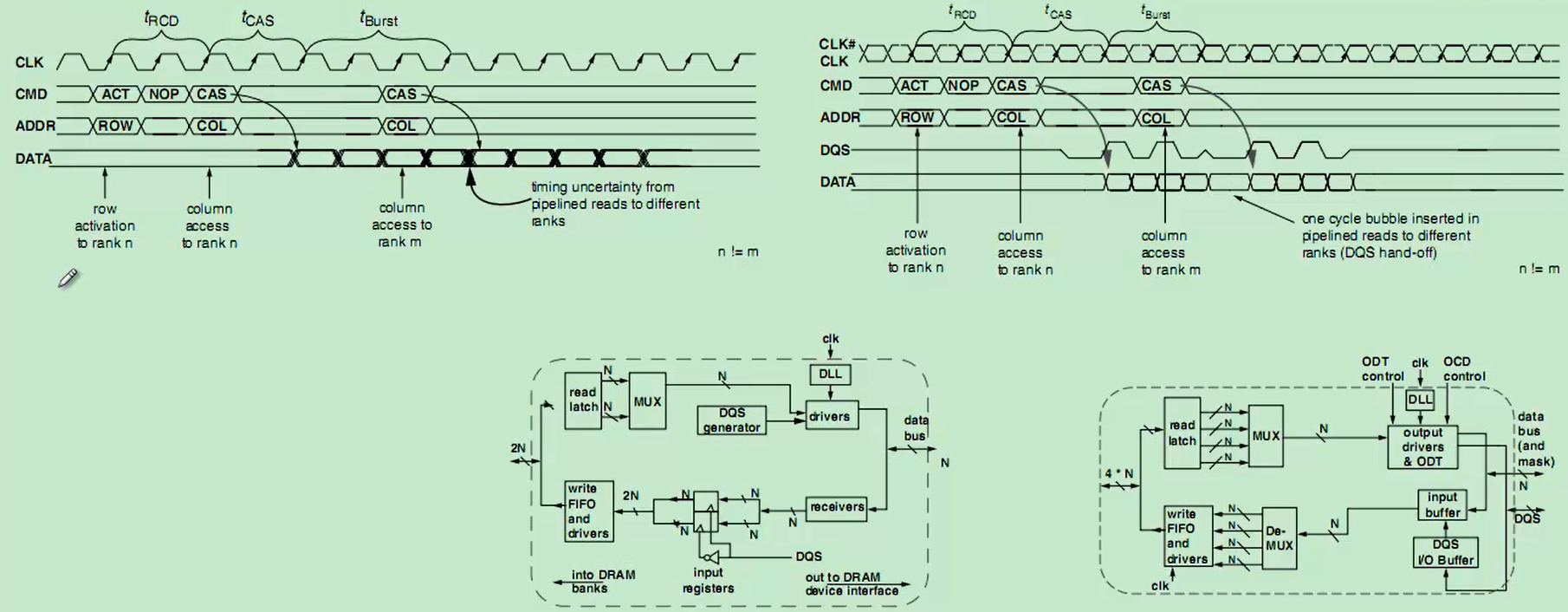

tCAS = tCL = colum latency

突发操作让ddr的效率提高,random操作可能导致ddr的效率不高

prefetch技术成为ddr性能提升的主要技术,cmd&address的decode逻辑或者器件本身速度并没有明显提高。

浙公网安备 33010602011771号

浙公网安备 33010602011771号