PCI学习之总线原理01

-----------以下资料由网络资料整理而成--------

PCI即Peripheral Component Interconnect,中文的意思是“外围器件互联”。

PCI总线支持32位和64位两种位宽,时钟频率为33MHz,总线带宽:32bit*33MHz=1056Mbps=132MB/s或64bit*33MHz=2112Mbps=264MB/s。

PCI总线结构:

PCI总线是一种树型结构,并且独立于CPU总线,可以和CPU总线并行操作。PCI总线上可以挂接PCI设备和PCI桥片,PCI总线只允许有一个PCI主设备,其它的均为CPI从设备,而且读写操作只能再主从设备之间进行,从设备之间的数据交互需要通过主设备中转。PCI总线结构如下图:

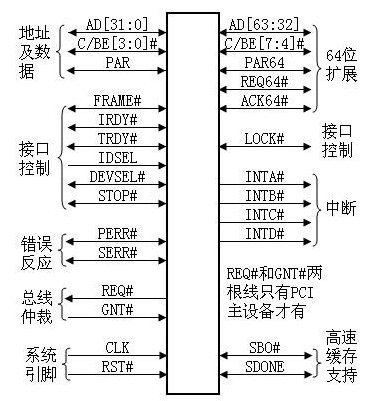

PCI总线管脚功能

PCI主设备最少需要49根线,从设备最少需要47根线,剩下的线可选。PCI管脚信号的类型:

in:输入信号;

out:输出信号

t/s:双向三态信号(Tri-state),无效时为高阻态;

s/t/s:持续三态信号,每次有且只有一个单元拥有并驱动的低有效、双向、三态信号。驱动一个s/t/s信号到低的单元在释放该信号浮空之前必须要将它驱动到高电平至少一个周期。

o/d:漏极开路输出;

#:此符号代表该信号在低电平时有效。

PCI总线引脚图如下所示:

不需要上拉的信号有AD[31:0],C/BE[3:0],PAR,IDSEL,CLK;其它的需要使用10K的上拉电阻。

>>>系统引脚

CLK:in,系统时钟,为所有PCI上的传输及总线仲裁提供时序。除RST#外,所有PCI信号都在CLK信号的上升沿采样。

RST#:in,异步复位信号。

>>>地址及数据引脚

AD[31:0]:t/s,地址数据复用引脚。FRAME#开始变为有效的那个时钟周期内AD[31:0]上传输的是地址。对于配置空间和存储空间,这是一个双字节地址,对于I/O空间,这是一个单字节地址。传输数据时,AD[7:0]为最低字节数据。

C/BE[3:0]:t/s,总线命令和字节允许复用管脚。在AD[31:0]上传输地址的时候,C[3:0]上传输的是总线命令,AD[31:0]上传输是数据的时候,BE[3:0]#用作字节允许,表示哪些通道上的数据是有效的。BE[0]#对应最低字节。

PAR:t/s,AD[31:0]和C/BE[3:0]#上的数据偶校验。PAR与AD[31:0]有相同的时序,但延迟一个时钟,在地址段后一个时钟,PAR稳定有效;对于数据段,在写传输中,PAR在IRDT#有效一个时钟稳定并有效;而在读传输中,PAR在TRDY#有效后一个时钟周期稳定并有效。一旦PAR有效,它必须保持有效直到当前数据段完成最后一个时钟。在地址段和写数据段,主PCI设备驱动PAR,在读数据段,目标从PCI设备驱动PAR。

>>>接口控制引脚

FRAME#:s/t/s,帧开始信号。由当前总线主设备驱动,以说明一个操作的开始和延续。FRAME#有效,说明总线开始传输,当FRAME#维持有效时,说明总线传输继续进行,当FRAME#无效时,说明传送的最后一个字节正在进行。

IRDY#:s/t/s,启动者准备好信号(Initiator Ready)。说明传输的启动者完成当前数据传输的能力。在读操作中,IRDY#有效说明总线主设备已经准备好接收数据。在写操作中,它说明AD[3:0]上已有有效数据。在IRDY#和TRDY#都有效的时钟周期完成数据传输。在IRDY#和TRDY#都有效之前,需要插入等待状态。

TRDY#:s/t/s:目标设备准备就绪(Target Ready)。说明传输的目标设备完成当前的数据传输能力。在写操作中,TRDY#有效说明目标设备已经准备好接收数据。在读操作中,它说明AD[31:0]上已有有效数据。

STOP#:s/ts/,停止信号。说明当前的目标设备要求总线主设备停止当前传输。

LOCK:s/ts,锁定信号。

IDSEL:in,初始化设备选择(Initialization Device Select)。在配置空间读写操作中,用作片选。

DEVSEL#:s/t/s:设备选择。当驱动有效时,说明驱动它的设备已将其他地址解码为当前操作的目标设备。

>>>仲裁引脚

REQ#:t/s,申请。想仲裁器说明该单元想使用总线。这是一个点对点的信号,每个总线主设备都有自己的REQ#。

GNT#:t/s,允许。仲裁器向申请单元说明其对总线的操作已被允许。这是一个点对点信号,每个总线主设备都有自己的GNT#。

>>>错误反馈引脚

PERR#:s/t/s,奇偶校验错误。该引脚用于反馈在除特殊周期外的其它传送过程中的数据奇偶校验错误。PERR#维持三态,在检测到奇偶检验错误后,在数据结束后两个时钟周期,由接收数据的单元驱动PERR#有效。并至少持续一个时钟周期。只有DEVSEL#的单元才能发出PERR#。

SERR#:o/d,系统错误(system error)。用于反馈地址奇偶校验错误、特殊周期命令中的数据奇偶校验错误和将引起重大事故的其他灾难性的系统错误。

>>>中断引脚

INTA#

INTB#

INTC#

INTD# :o/d 中断输出

>>>高速缓存支持引脚

SBO#:in/out,监视补偿。

SDONE:in/out,监视进行。

>>>64位总线扩充引脚

AD[63:32]:t/s,地址数据服用引脚提供32个附加位。

C/BE[7:4]#:t/s,总线命令和字节允许复用管脚。

REQ64#:s/t/s,请求64位传输。

ACK#:s/t/s,应答64位传送。

PAR64:t/s,高双字偶校验。

--------------------------------------------------------------------

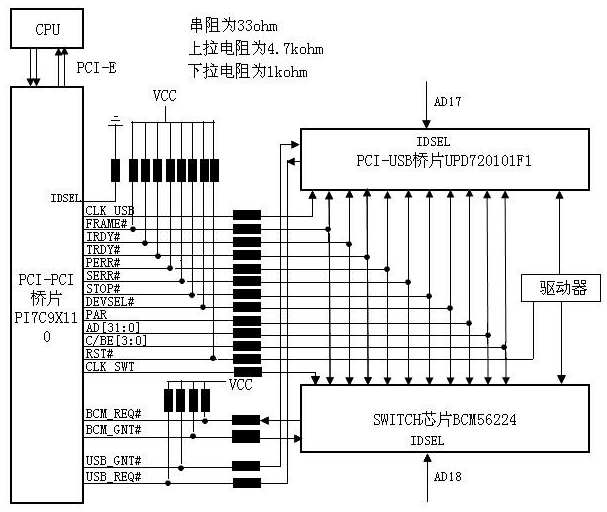

>>>PCI总线的典型接法:

>>>PCI信号的驱动方式

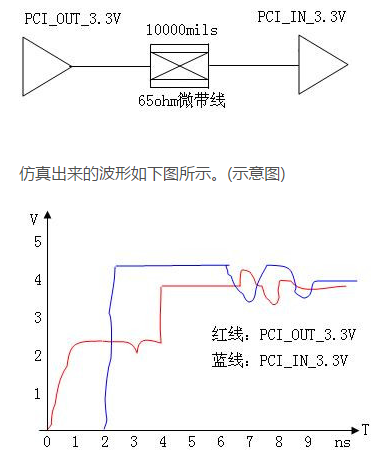

PCI信号为半波驱动方式,为了更好的说明什么时候半波驱动方式。下图为仿真链路:

从上图可以看出,PCI_OUT_3.3V输出先是以大约2.3V的半幅度来驱动总线,经过大约2ns的延迟后,信号到达接收端,接收端阻抗不匹配,将信号反射回始端,反射信号经过2ns的延迟后到达起始端,驱动信号与反射信号在起始端出现叠加,使得PCI_OUT_3.3V在大约4ns的位置达到全幅度3.3V。之后经过短暂震荡后趋于平衡。由于大多数PCI器件内都内置了限幅器件,所以PCI信号在不在起始端添加串行匹配电阻都可以使PCI信号很快平稳。只是加串阻后,信号幅度更低,使PCI器件的使用寿命更长。

>>>PCI操作类型

前面已经说过,在FRAME信号有效后的第一个时钟周期,AD[31:0]总线上传输的是目标PCI器件的地址,C/BE[3:0]上传输的操作命令类型。如下图所示:

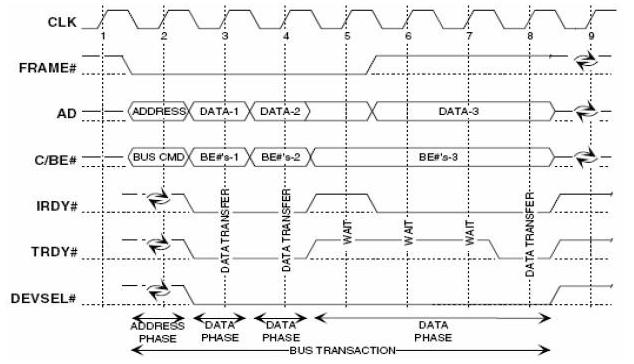

>>>>PCI总线的读写时序

------------->写时序如下图所示

如上图所示,在FRAME#有效后的第一个时钟周期内,AD上传输的是要写入目标PCI设备的地址信息,C/BE#上传输的是命令类型(I/O写命令为0011),DEVSEL#信号有效后,表明目标设备已经被选择到,IRDY#和TRDY#同时有效后,主PCI设备向目标PCI设备中传输要写入的数据,在第5个时钟周期时,IRDY#和TRDY#同时变为无效状态,AD总线上被插入一个等待周期,在第6和第7个时钟周期时,IRDY#有效,但是TRDY#无效,传输仍然不能有效进行,总线上被继续插入两个等待周期,第8个时钟周期时,IRDY#和TRDY#都有效,数据继续传输。

--------->读时序如下图

读操作和写操作类似,只是在FRAME#有效后的第一个时钟周期内,C/BE#上传输的是读操作命令而已(I/O读操作命令为0010)。

>>>PCI设备的配置空间

所有除主桥之外的设备功能,必须实现配置地址空间,目前有三种类型的首部格式:首部类型0,用于全部除PCI桥之外的设备;首部类型1,用于PCI-PCI桥;首部类型2,用于Card Bus桥。

每个PCI设备的配置空间大小为256字节,用来存放PCI配置文件,其中文件头标识区占64字节,下图为类型0的首部:

》厂家ID:用来区别每个PCI设备生产商,由PCI-SIG组织分配,0xFFFF标识无效。

》设备ID:又来标识设备类型。

》命令寄存器:为发出PCI和响应PCI总线命令提供粗略控制。

》状态寄存器:用于记录PCI总线的事件状态信息。

》版本标识:标识PCI设备的版本。

》分类代码:用来标识PCI设备的功能分类和特定的变成接口,只为读存储器。

》Cache行大小:指定系统中高速缓存Cache一行的长度,以Dword为单位,可读写。

》持有定时器:指定PCI总线主设备的延时计时值,以PCI总线的时钟为单位。

》配置类型:表示头标区类型,以及是否为多功能设备。

》自测能力BIST:支持自测的PCI设备为1,不支持的为0.

》基地址0~5:实现PCI设备所有使用地址空间的再定位

》扩展ROM基地址:表示ROM在内存中的起始地址,执行其中代码完成PCI初始化。

》中断线:报告PCI设备使用了哪些中断引脚。

》最短获准时间:指定PCI设备对延时计数器的设定值。

》最大等待时间:指定PCI设备对延时计数器的设定值。

>>>>>>PCI总线小案例

Q1:在测试PCI总线的TRDY信号时,发现该信号从低电平拉倒高电平时太缓慢,如下图所示。

问题分析:

TRDY是s/t/s信号,在前面已经讲过,s/t/s信号有如下特点:

1、在某一个时刻只能由一个设备驱动;

2、在释放之前必须将该信号驱动到高电平,并且至少保持一个时钟周期;

3、其它设备必须等到该信号释放至少一个时钟周期后才能重新驱动它;

4、该信号必须进行外部上拉处理;

经过分析该PCI总线的逻辑代码得知,该逻辑在处理s/t/s信号时没有完全按照规范来做,将TRDY信号置为低电平有效后直接释放到高阻态,没有将它驱动到高电平后再释放,因此,TRDY在低电平位置被释放到高阻态后,完全依靠外部的上拉电阻将其拉倒高电平位置,由于外部上拉比较弱,导致我们看到上面的TRDT电平上升缓慢现象。修改逻辑代码后问题消失。