BGA 256 FPGA PCB设计

终于耐不住寂寞,开始了PCB设计。。

为了降低成本,拟采用4层板搞定256 IO的FPGA,同时使用所有的IO,绝不浪费任何一丝的资源。。。。大多数业内人士说,256IO 4层全部走线,可能性不大。。。不好意思,我好想实现了。。。

且不说我Layout的怎么样,先说说我的经验吧:

(1) 关于规则要求

走线:6mile及以上

间距:6mile及以上

过孔:12/20mile及以上

层数:4层

厚度:1.6mm

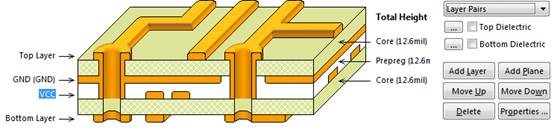

(2) 关于PCB分层

毋庸置疑,4层板,正常应该为信号、地、电源、信号。但是为了适当的提高走线的灵活性,在电源层上稍微走几根线不会影响全局,因此将地层设置为负片,而电源层设置为正片,如下所示:

实际上电源层不到万不得已的时候,一定不去走线!!!

(3) 关于耦合电容

这主要可以分为2部分,一部分是内核电压的电容,另一部分是IO电压的电容。在TQFP FPGA的设计中,我总是靠近IO 直接拜访。。走线神马的轻松而愉快。。但是BGA中,没辙了。。。

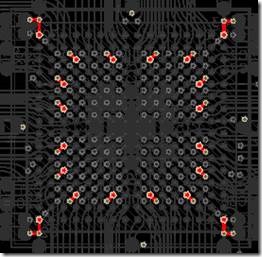

幸运的是BGA的内核电压就在“内部”,而IO电压在靠外面的地方。。。内核与IO电压如下所示:

同时内核中间是BGA的GND,因此红圈圈部分不用再走线,很是放和内核的滤波电容。二IO电压向外扩展,刚好往外放电容。。。。此外,内核电压四个角落的1.2V,为PLL的模拟电压,直接扇出到BGA的角落。

最后,分配内核4个电容,IO电压8个电容,而PLL部分完整按照手册设计电路,3D视图如下图所示:

其中1.2V内核电压走线如下所示,PLL电源走线和总体1.2V的输入,被迫走在了电源层,完成了内核电压的扇出。

(4) IO的扇出技巧

a) 首先,上一篇博客中讲过,外面2圈IO可以直接在顶层扇出,不用过孔。

b) 其次,内层的IO通过过孔扇出,这里由于BGA为1mm间距,过孔采用了12/20mile。

c) 最后,实在没有办法的IO,迫不得已下从电源层扇出,到BGA片子外部时,重新过孔到TOP/Buttom Layer。

d) 最重要的是,为了完成4层256 IO走线,所有成功扇出的走线,都得保证在顶层或者底层走线。

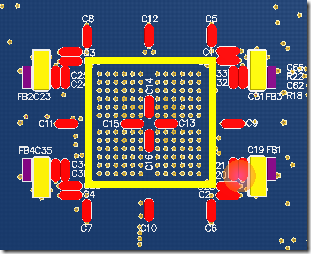

部分层走线如下所示:

也就是说,除了PLL的1.2V电压,在电源层上总共辅助扇出了7个IO。这样,4层完成了所有IO的扇出。

(5) 其他IC的走线

既然已经引出了所有的IO,其他IO的走线就回归到了2层板。当然方便的时候,由于我们采用了4层板设计,GND与VCC可以直接打孔到电源层投个懒。。。给个我最近设计的BGA256 FPGA板卡的扇出图,如下所示:

256 BGA,4层板轻松完成,呵呵。。。。

(6) 制版工艺

这是最蛋疼的。。。除了上次0.65mm的BGA板卡,这是我第一次设计BGA板卡,同时12/20mile的过孔,6mile的走线及间距,工艺相对于我以前那些戳板子而言,提高了不少,。,。,。。。嘉立创12/24mile,内层8mile等的制版工艺无法完成我的板卡。。。。。

考虑未来的某些因素,慎重选择制版上中,兴森快捷这类肯定是做不起的,屌丝一枚。。。追求美好的明天,、、、、、

浙公网安备 33010602011771号

浙公网安备 33010602011771号