HDL模块导入System Generator

Black Box可以导入任何符合规范要求的HDL代码,包括用户自己编写的HDL代码、Core generator 产生的HDL代码等

基本上按照《FPGA开发指南》上的例子。在system generator中导入 core generator中的生成的IP。

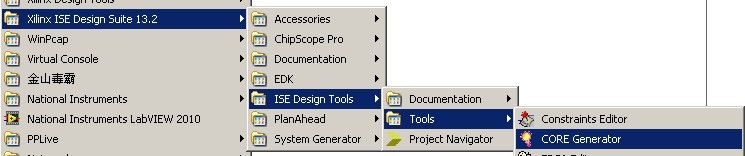

1、启动core generator,点击图标,打开core generator.

点击File->New Project,选择合适的目录建立工程。

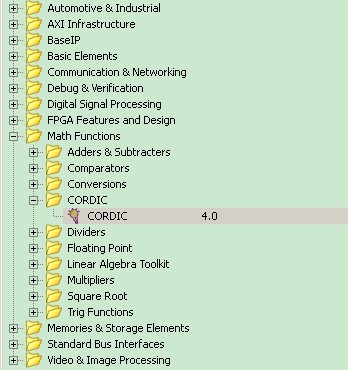

双击cordic算法IP核,配置好参数后不需要太多配置,点击generator,生成工程文件即可。

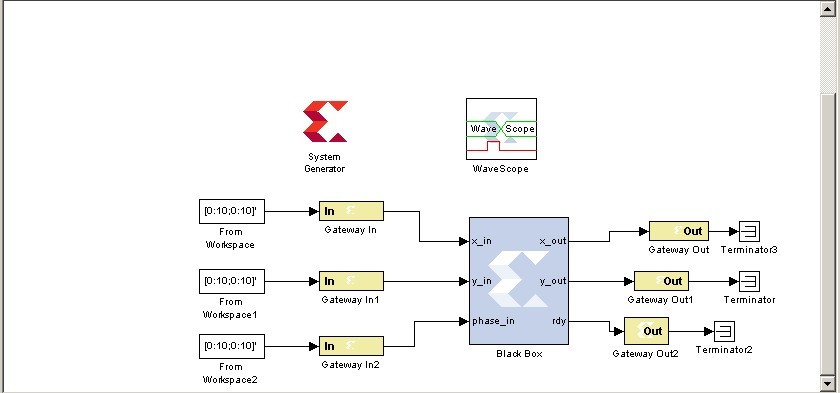

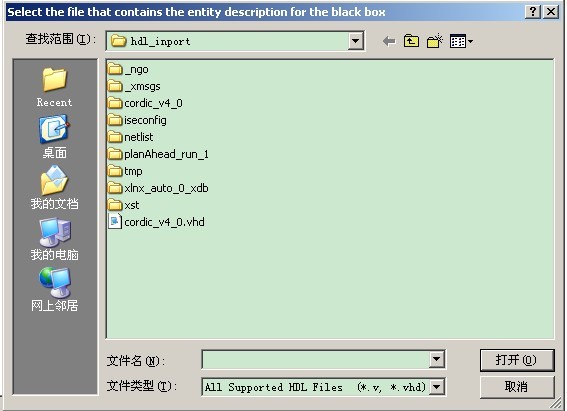

core generator产生的IP核,在SG中以黑盒的形式导入。添加xilinx blockset-》basic elements中的Black Box到SG中,选择cordic_v4_0.vhd,系统自动添加所需的配置文件(cordic_v4_0_config.m)。

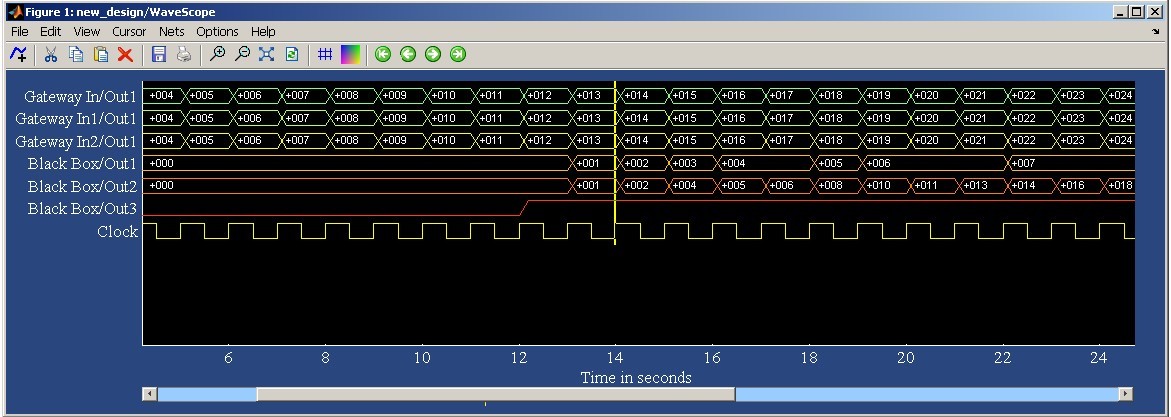

双击已经添加到工程里的Black box,选择Simulation mode 为ISE Simulator。(默认Inactive不激活仿真)。这样就可以在matlab中观察仿真结果对不对。结果对不对,我不知道cordic算法到底如何,所以不懂。结果如下图。

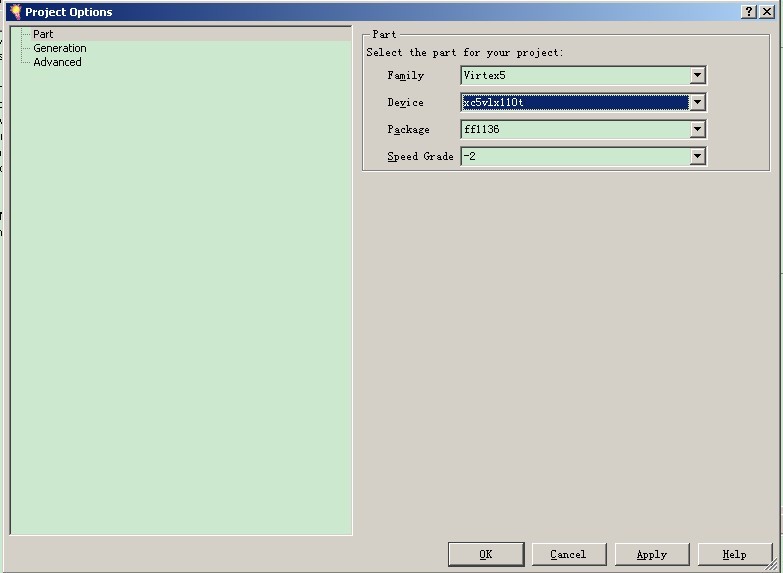

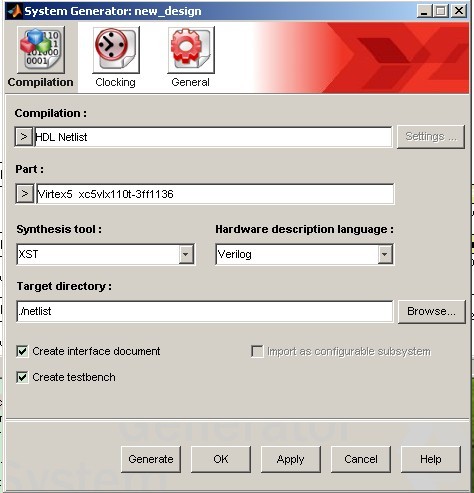

3.双击 SG中system generator图标,打开配置选项。选择生成HDL netlist。器件型号与封装生成相应工程。

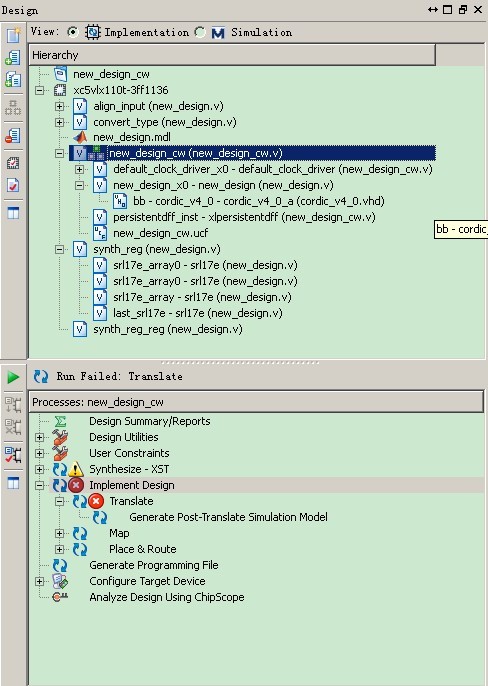

打开生成的ISE工程(在netlist目录中)。综合通过了,但是布局布线就失败了,这让人很郁闷。

ERROR:NgdBuild:604 - logical block 'new_design_x0/bb' with type 'cordic_v4_0'

could not be resolved. A pin name misspelling can cause this, a missing edif

or ngc file, case mismatch between the block name and the edif or ngc file

name, or the misspelling of a type name. Symbol 'cordic_v4_0' is not

supported in target 'virtex5'.

在网上找到几个相似问题的链接。

http://bbs.ednchina.com/BLOG_ARTICLE_1969774.HTM

http://bbs.21ic.com/icview-213795-1-1.html

http://www.xilinx.com/support/answers/38262.htm

我也尝试的去试了试,但没有效果,错误依然如故,书中的例子是用ISE10.0做的,书中好多步骤在新版本中早就没有了,呵呵,但相应的很多bug依然存在,解决办法却没更新,真让人无语。完整的工程以附件形式上传了。

浙公网安备 33010602011771号

浙公网安备 33010602011771号