【转】 DFT小讲座之2_DFT@芯片开发不同阶段

在很多人的印象里,DFT(可测试性设计)就是简单的利用EDA工具,在IC设计的某一阶段,通过工具对芯片逻辑自动优化重组,产生DFT测试逻辑。

然而在现实中, DFT解决方案远非push button那么简单。尽管EDA厂商在提供DFT解决方案时候的愿景是实现测试逻辑生成的最大可能性的自动化,随着芯片功能的复杂化,仅调配片上资源产生DFT逻辑就需要巨大的时间和精力。

在项目执行过程中,DFT的参与的越早,对于测试逻辑的规划就越合理;对现有功能电路的利用率就越高;版图和时序的实现就越容易。

芯片开发过程包括从产品架构定义到封装后芯片测试等10个阶段。

它们分别是:

-

产品定义

-

RTL实现

-

RTL验证

-

逻辑综合 (产生synthesis netlist)

-

物理综合 (place&route 产生layout netlist)

-

后端验证 (基于netlist 和sdf的验证)

-

流片

-

晶圆级测试

-

封装

-

封装后测试

除了流片和封装这2个生产步骤之外,DFT需要参与到其他所有的阶段当中。

产品定义和架构阶段

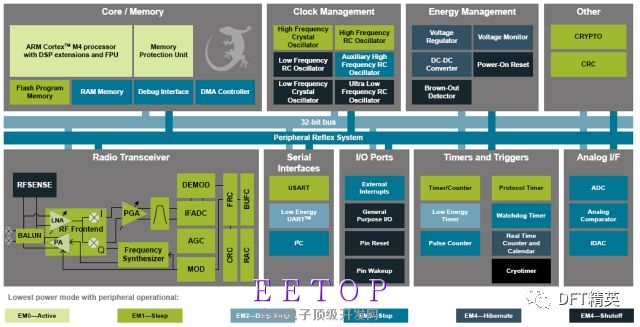

在这一阶段, 与整个SoC架构定义类似, DFT架构需要安排整体测试架构,考虑scan策略,mbist布局,片上资源规划分析等各种任务。

该阶段的DFT规划至关重要。 在项目整体结构上综合考虑DFT方案,合理规划不同IP, module的测试需求,可以给整个芯片实现最经济的测试方案。

RTL实现及验证阶段

在这一阶段,除了将架构阶段的各种策略以RTL的方式实现外,还需要通过module级别,以及chip级别的验证,检查设计漏洞。同时和芯片的功能设计交互印证,确保DFT的设计不会影响功能方的设计,同时功能方的设计可以被DFT逻辑所控制。 这部分的工作时间跨度较长,需要在整个前段设计阶段不断交互反馈,修改。

逻辑及物理综合和layout验证

在这一阶段, DFT的主要任务在于和版图部门充分沟通合作。 任务包含但不局限与:

-

提供不同测试模式下的约束条件

-

扫描链插入

-

针对测试逻辑的时序分析

-

版图后时序仿真

流片后阶段

在芯片流片后,前段IC设计工作基本完成。

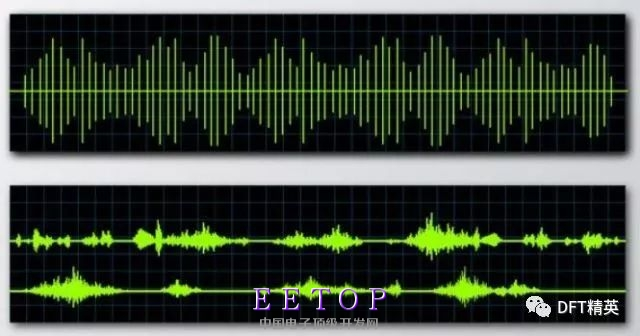

这时,DFT需要参与到silicon support当中。 DFT工程师需要生成并调试测试向量;帮助芯片bring up;帮助silicon learning以及failure analysis。

这一阶段的DFT工作除了测试向量以外,还需要对测试,yield等各部门给予及时有效的支持。

浙公网安备 33010602011771号

浙公网安备 33010602011771号