基于FPGA的图像处理(三)--图像融合

2012-11-03 19:22 libing64 阅读(2104) 评论(0) 收藏 举报System Generator安装之后可以在Simulink中调用相应的模块进行视觉算法的搭建,我两台电脑上分别是ISE12.3+matlab2010a, ISE10.1+Matlab2010a。需要注意的是ISE和Matlab之间是有型号匹配的。

首先要打开FPGA,打开Simulink,新建一个Model。

在Xilinx Blockset中拖取需要的模块,搭建图像处理的算法。本程序是一个图像融合算法,读入两幅图像,相加,截取低8位,输出。

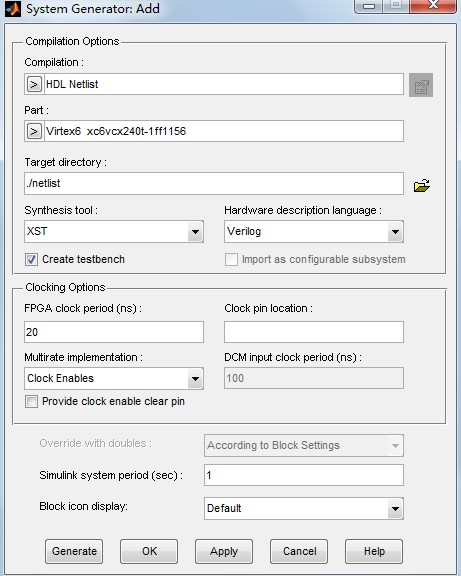

其中System generator模块是每一个model中都必须的,在System Generator可以进行一些配置,包括编译选项、FPGA的选型、综合工具、HDL语言、时钟周期等,如果只是在上位机仿真不下载到FPGA中,那么这些参数基本都不用改。

这里我使用的Xilinx公司的官方开发板ML605,芯片是Virtex6 xc6vc240t-1ff1156,HDL语言选择了Verilog。

gateway In和gateway out模块是FPGA和外部的纽带,FPGA只支持定点数,是不支持float、double类型的,通过gateway In可以将数据转化为需要的类型,gateway out又将处理之后的数据传出,可以在Matlab中查看。

为模型添加回调函数callback。在model properties中添加。PreLoadFcn中添加LoadImage_gray,StopFcn中添加ShowImage_gray,这两个函数实际是在当前文件夹下的m文件,这样在进行仿真时两个函数会分别在加载和停止时自动执行。二者的功能分别是提供初始数据和数据的后处理显示。

//LoadImage_gray的代码,将两张原始图像读入,并转化为一个n行2列的矩阵传入gateway In

%读取原始图像数据

SourceImage1_2D = imread('rice.png');

SourceImage2_2D = imread('text.png');

SourceImage2_2D = 250*SourceImage2_2D;

%得到图像的长宽尺寸

ImageWidth = size(SourceImage1_2D,2);

ImageHeight = size(SourceImage1_2D,1);

%将二维数组转换成一维数组

SourceImage1_1D = reshape(SourceImage1_2D',1,ImageWidth*ImageHeight);

SourceImage1_1D = [SourceImage1_1D];

SourceImage2_1D = reshape(SourceImage2_2D',1,ImageWidth*ImageHeight);

SourceImage2_1D = [SourceImage2_1D];

%按照格式形成Simulink的To Workspace模块要求的数据格式

SourceImage1_1D = [ double(0:ImageWidth*ImageHeight-1)' double(SourceImage1_1D)'];

SourceImage2_1D = [ double(0:ImageWidth*ImageHeight-1)' double(SourceImage2_1D)'];

%设置整个模块的输入到输出延时

DesignLatency = 2;//ShowImage_gray的代码 ,主要是将处理结果的以为数据转化为二维图像数据,并显示

%将DestImage1D一维数组转换成规定大小的DestImage2D二维数组

DestImage2D = reshape(DestImage1D(DesignLatency:DesignLatency+ImageHeight*ImageWidth-1),ImageWidth,ImageHeight);

DestImage2D = DestImage2D';

%按照格式显示输入图像和输出图像

h = figure;

clf;

colormap(gray(256));

set(h,'Name','Results');

image(DestImage2D), axis off;

这些准备完成之后还要修改一些仿真时间,这里是图像的点数加上延时,ImageWidth*ImageHeight+DesignLatency。

DesignLatency是一个需要自己根据算法中延时的长度自己调整的参数,并在Loadimage_gray中修改。需要特别注意的是System Genrator的时序问题是一个很麻烦的问题,经常会因为时序导致仿真结果一差千里,千万注意。

下面可以进行仿真了。

//原图1 rice

//原图2 text

//计算结果

二、生成HDL代码

System Generator的真正高端之处在于能够将简单搭建的模块转化为HDL代码,我们进行简单的配置,生成Verilog HDL代码。

选中Create testbench,硬件语言选择Verilog HDL,点Generate ,自动生成ISE工程。

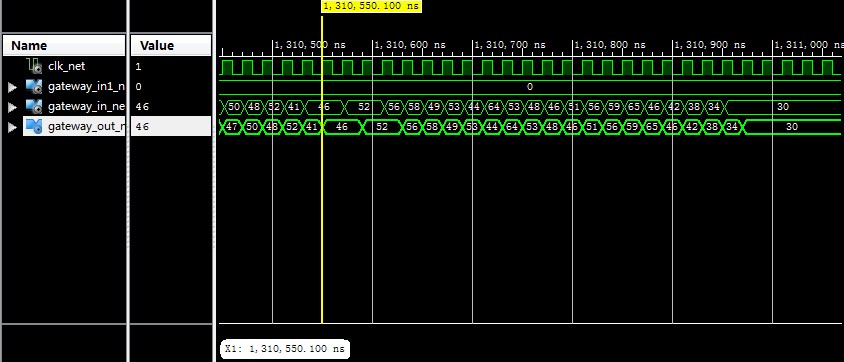

完成之后在netlist文件夹下生成了一个ISE的工程,直接用ISE打开工程就可以看到Verilog代码,包括testBench,由于我的板子是官方开发板,因此其中的管脚约束文件都是自动生成的,十分方面,如果使用的自己做的板子的话,可能需要修改一些管脚约束文件ucf文件。在ISE下进行仿真,效果如下:

可以看到 geteway out的数据都是两个gateway In数据的和,刚还延迟一个时钟周期。

目前正在使用System Generator搭搭建立体视觉算法,虽然已经搭建完成,但是时序问题没有处理明白,导致进行匹配时,总是发生错位,导致匹配效果大大降低,如果哪位高手解决了此问题的话,还望不吝赐教。

浙公网安备 33010602011771号

浙公网安备 33010602011771号