I2C通信接口及通信协议

1、I2C总线概念

I2C总线支持任何IC生产过程(NMOS、CMOS、双极性),两线(串行数据SDA和串行时钟SCL)在连接到总线的器件间传递信息,每个器件都有一个唯一的地址识别(微控制器、LCD驱动器、存储器或键盘接口等),而且都可以作为一个发送器或者接收器(由器件的功能决定),很明显,LCD驱动器只是一个接收器,而存储器既可以接收又可以发送数据,除了发送器和接收器外,器件在执行数据传输时也可以被看作是主机或从机,主机是初始化总线的数据传输并产生允许传输的时钟信号的器件,此时,任何被寻址的器件都被认为是从机,I2C总线的一些术语定义如下:

| 术语 | 描述 |

| 发送器 | 发送数据到总线的器件 |

| 接收器 | 从总线接收数据的器件 |

| 主机 | 初始化发送、产生时钟信号和终止发送的器件 |

| 从机 | 被主机寻址的器件 |

| 多主机 | 同时有多于一个主机尝试控制总线,但不破坏报文 |

| 仲裁 | 是一个在有多主机同时尝试控制总线,但只允许其中一个控制总线并使报文不被破坏的过程 |

| 同步 | 两个或多个器件同步时钟信号的过程 |

I2C总线是一个多主机的总线,就是说可以连接多于一个能控制总线的器件到总线。

2、I2C特征

- 只要求两条总线线路:一条串行数据线(SDA)和一条串行时钟线(SCL);

- 每个连接到总线的器件都可以通过唯一的地址和一直存在的简单的主机/从机关系软件设定地址,主机可以作为主机发送器或者主机接收器;

- 真正的多主机总线,如果两个或更多主机同时初始化数据传输可以通过冲突检测和仲裁防止数据被破坏;

- 串行的8位双向数据传输速率在标准模式下可达100Kbit/s,快速模式下可达400Kbit/s,高速模式下可达3.4Mbit/s;

- 片上的滤波器可以滤掉总线数据上的毛刺波,保证数据完整;

- 连接到相同总线的IC数量只受到总线的最大电容400pF限制。

3、位传输

由于连接到I2C总线上的器件有着不同种类的工艺(CMOS、NMOS、双极性),逻辑0(低)和逻辑1(高)的电平不是固定的,它由VDD的相关电平去决定,每传输一个数据位就产生一个时钟脉冲。

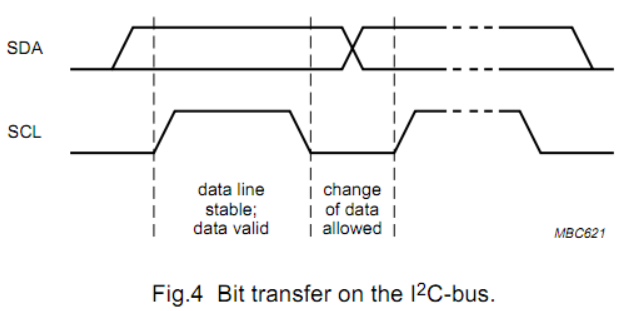

(3.1)数据的有效性

SDA线上的数据必须在时钟的高电平周期保持稳定,数据线的高或低电平状态只有在SCL线的时钟信号是低电平才能改变,如下图所示:

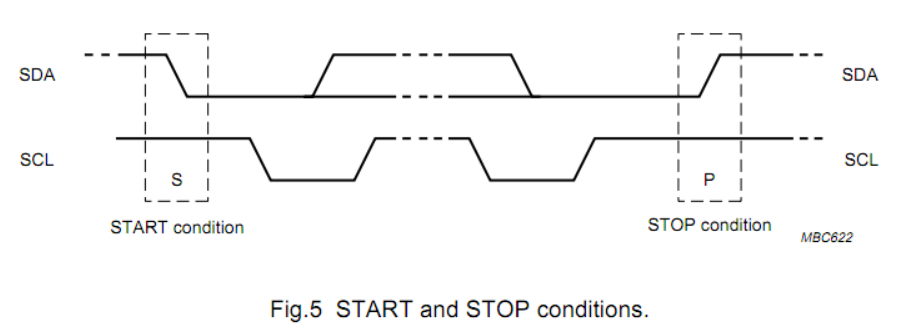

(3.2)起始和停止条件

在I2C总线中,唯一出现的是被定义为起始(S)和停止(P)条件的情况,如下图所示:

其中的一种情况是,当SCL线为高电平时,SDA线从高电平向低电平切换,该情况表示I2C总线的起始条件,另外一种情况时,当SCL线为高电平时,SDA线从低电平向高电平切换,该情况表示I2C总线的停止条件,起始条件和停止条件一般由主机产生,总线在起始条件后被认为处于忙的状态,在停止条件后的某段时间,总线会被认为处于空闲状态,如果产生重复起始条件(Sr)而不产生停止条件,总线会一直处于忙的状态,此时的起始条件(S)和重复起始条件(Sr)在功能上是一样的。

如果连接到总线的器件合并了必要的硬件接口,那么用它们检测起始条件和停止条件将十分简便,但是,没有这种接口的微控制器在每个时钟周期至少要采样SDA线两次来判别是否发生电平切换。

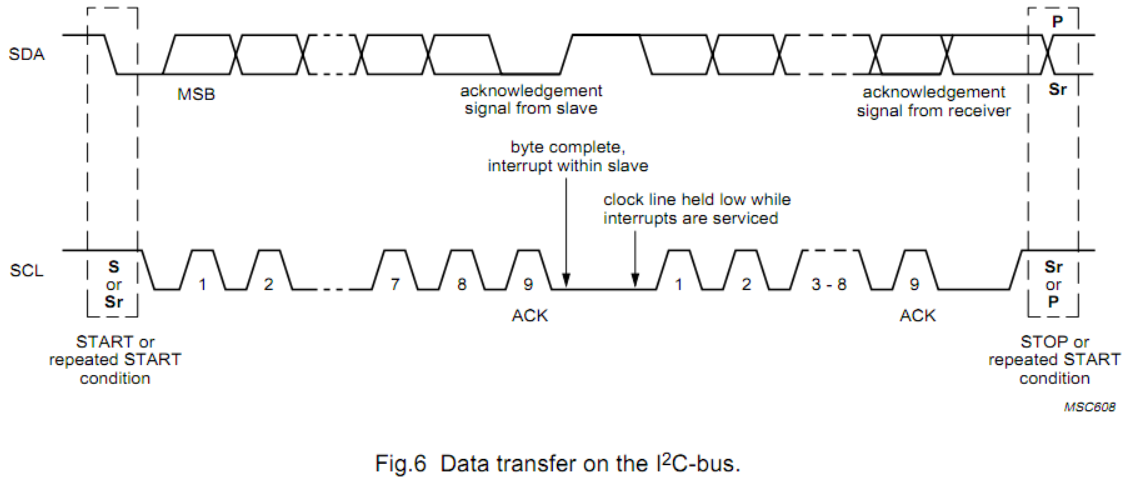

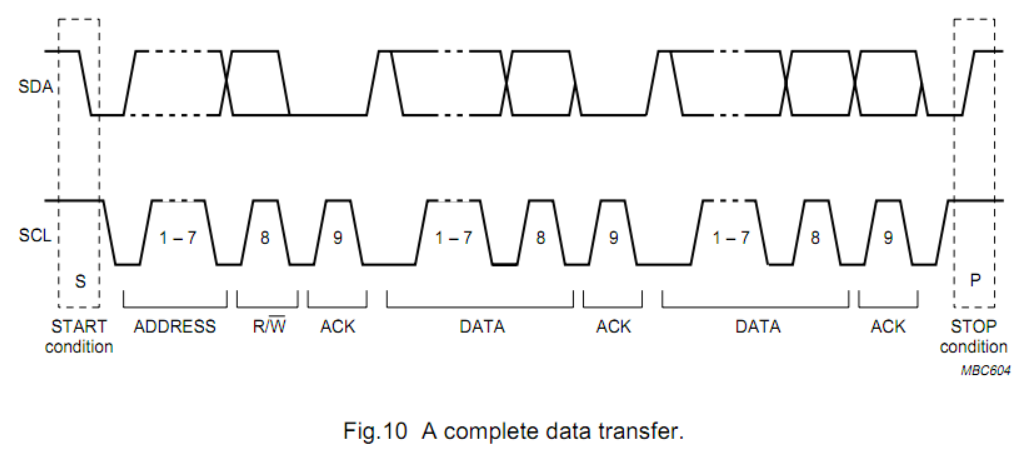

4、传输数据

(4.1)字节格式

发送到SDA线上的每个字节必须为8位,每次传输可以发送的字节数量不受限制,每个字节后必须跟着一个响应位,首先传输的是数据的最高位(MSB),如果从机要完成一些其它功能(例如一个内部中断服务程序)后才能接收或发送下一个完整的数据字节,可以使时钟线SCL保持低电平迫使主机进入等待状态,当从机准备好接收下一个数据字节并释放时钟线SCL后,数据继续传输,I2C总线数据传输如下图所示:

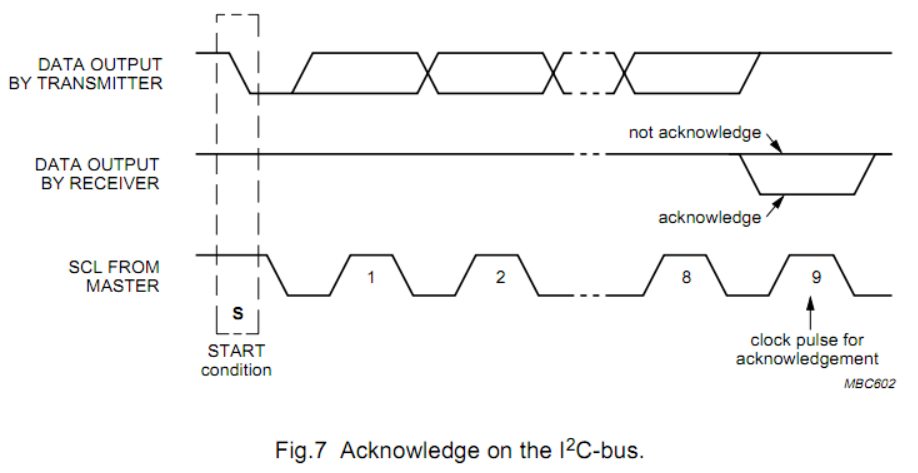

(4.2)响应

数据传输必须带响应,相关的响应时钟脉冲由主机产生,在响应的时钟脉冲期间,发送器释放SDA线(高),在响应的时钟脉冲期间,接收器必须将SDA线拉低,使它在这个时钟脉冲的高电平期间保持稳定的低电平,当然,必须考虑建立和保持时间,I2C总线的响应如下图所示:

5、7位地址格式

I2C总线数据的传输遵循下图所示的格式:

在起始条件(S)后,发送了一个从机地址,这个地址共有7位,紧接着的第8位是数据方向位(R/W),0表示发送(写),1表示请求数据(读),数据传输一般由主机产生的停止条件(P)终止,但是,如果主机仍希望在总线上通讯,它可以产生重复起始条件(Sr)和寻址另一个从机,而不是首先产生一个停止条件,在这种传输中,可能有不同的读写格式结合。

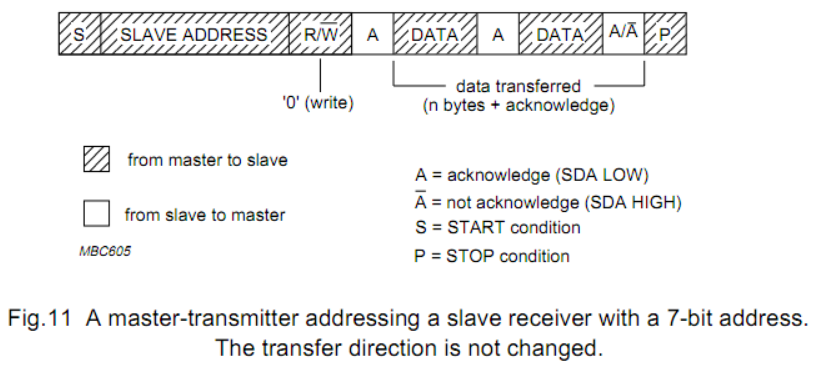

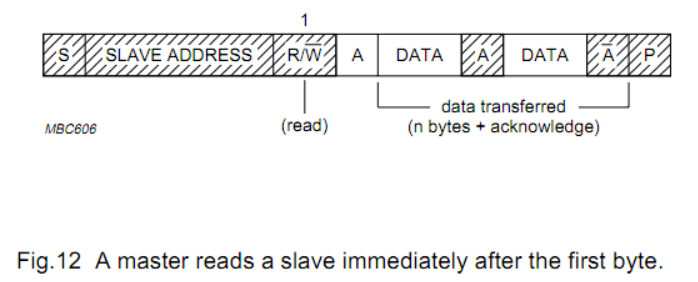

可能的数据传输格式有:

- 主机-发送器发送到从机-接收器,传输的方向不会改变,如下图所示:

- 在第一个字节后,主机立即读从机,如下图所示,在第一次响应时,主机-发送器变成主机-接收器,从机接收器变成从机-发送器,第一次响应仍由从机产生,之前发送了一个不响应信号的主机产生停止条件;

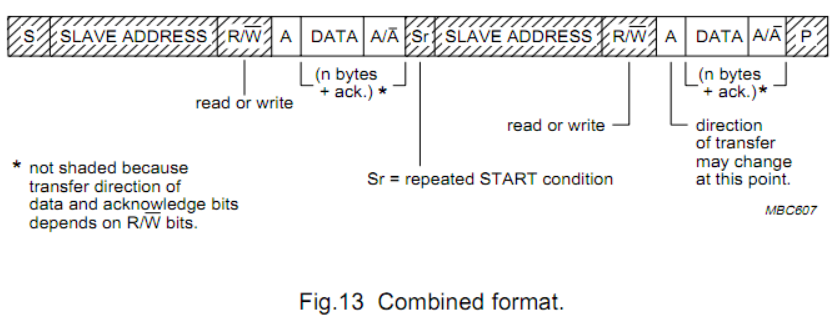

复合格式如下图所示,传输改变方向的时候,起始条件和从机地址都会被重复,但R/W位取反,如果主机-接收器发送一个重复起始条件,它之前应该发送了一个不响应信号;

复合格式如下图所示,传输改变方向的时候,起始条件和从机地址都会被重复,但R/W位取反,如果主机-接收器发送一个重复起始条件,它之前应该发送了一个不响应信号;

需要注意的是:

需要注意的是:

- 复合格式可以用于例如控制一个串行存储器,在第一个数据字节期间,要写内部存储器的位置,在重复起始条件和从机地址后,数据可以被传输;

- 自动增加或者减少之前访问的存储器位置等所有决定都由器件的设计者决定;

- 每个字节都跟着一个响应位;

- 兼容I2C总线的器件在接收到起始或者重复起始条件必须复位它们的总线逻辑,甚至在这些起始条件没有根据正确的格式放置,它们也都期望发送从机地址;

- 起始条件后面立即跟着一个停止条件,此时报文为空,是一个不合法的格式。

6、7位寻址

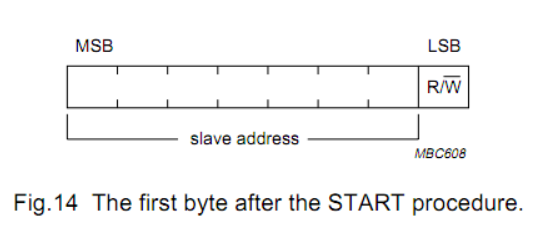

I2C总线的寻址过程是通常在起始条件后的第一个字节决定了主机选择哪个从机,第一个字节的头7位组成了从机地址,如下图所示:

最低位(LSB),它决定了报文的方向,第一个字节的最低位是0表示主机会写信息到被选中的从机,1表示主机会向从机读信息,当发送了一个地址后,系统中的每个器件都在起始条件后将头7位与自己的地址进行比较,如果一样的话,器件会任务它被主机寻址,至于是从机-接收器还是从机-发送器都由最低位进行决定。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 如何调用 DeepSeek 的自然语言处理 API 接口并集成到在线客服系统

· 【译】Visual Studio 中新的强大生产力特性

· 2025年我用 Compose 写了一个 Todo App