使用Cadence SPB设计时,如何在布置Via Array时避免盘中孔?

| 版本 | 日期 | 说明 |

|---|---|---|

| V0 | 20240206 | 初版 |

| V1 | 20240617 | 原文方法不正确,已经删除 |

| V2 | 20241009 | 新方法,确认可用 |

软件套件是Cadence SPB 17.4,其他版本可以用同样的思路尝试。

1. Via Array的作用

这里指的是布置接地的Via Array,为信号提供尽可能短的回流通路。

2. 布置Via Array时的盘中孔

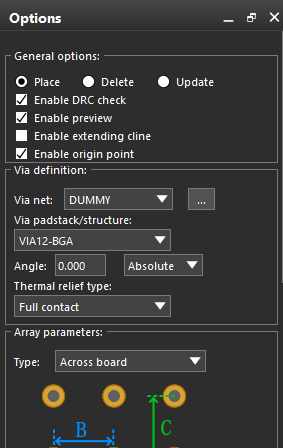

Place Via Array的时候,即使已经勾选了Enable DRC check,布置的过孔会避让其它网络,但是不会避让同名网络,造成“盘中孔现象”。

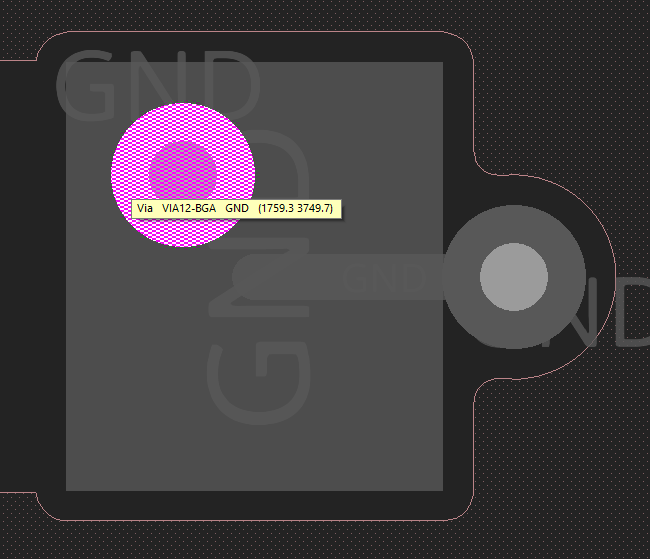

如下图是一个例子。高亮的是一个盘中孔,虽然电气连接正确,也能通过DRC,但是不利于制造和焊接(即违背了DFM),因此尽量避免。(除非是散热焊盘,散热焊盘往往需要盘中孔,这个可以在最后手动添加)。

查找盘中孔然后一个个删除很麻烦,如果布置过孔时就能避免问题是最好的。

3. 处理思路

既然DRC会自动避让不同网络,那么思路就是:

- 让过孔的网络与器件接地网络不同。

- 放置Via Array,此时会自动避让。

- 删除可能依然存在的少部分盘中孔。

- 修改过孔网络与器件接地网络一致。

- 刷新PCB版图,此时在PCB中二者网络名一致。

4. 实例

4.1. 在原理图中构造一个小范围的临时网络

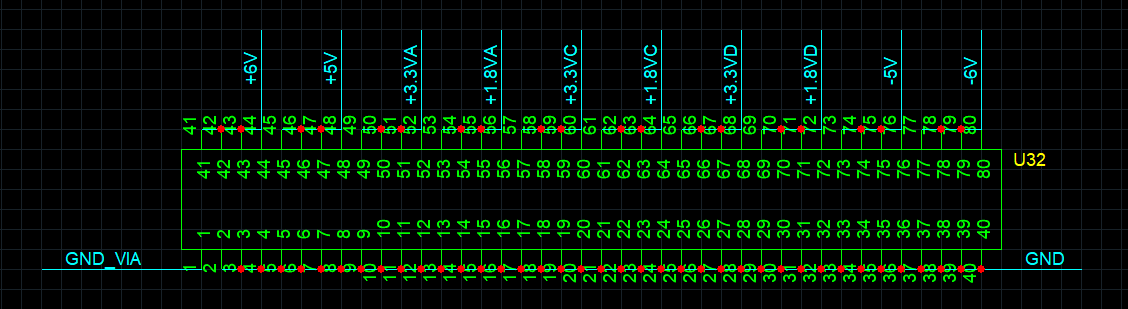

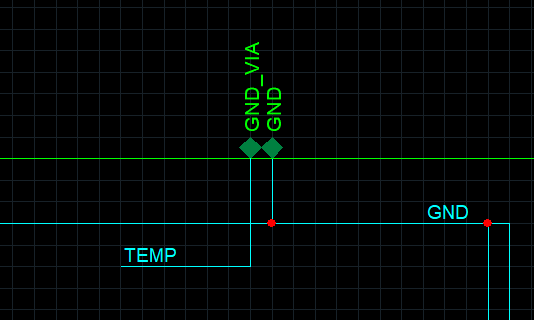

上图是一个插座,本来Pin#1~Pin#40全是 GND,但是现在取Pin#1为一个新名称 GND_VIA。

只要在原理图中构造一个范围很小的net(比如只连接一个pin)的网络就行。

按照以上思路,先将两个网络名称分开,连接如下图所示。

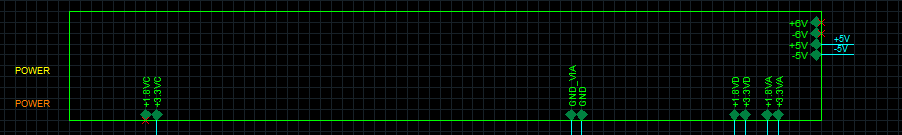

在原理图顶层(版图中一样)这个网络叫做 TEMP。

4.2. 同步到版图

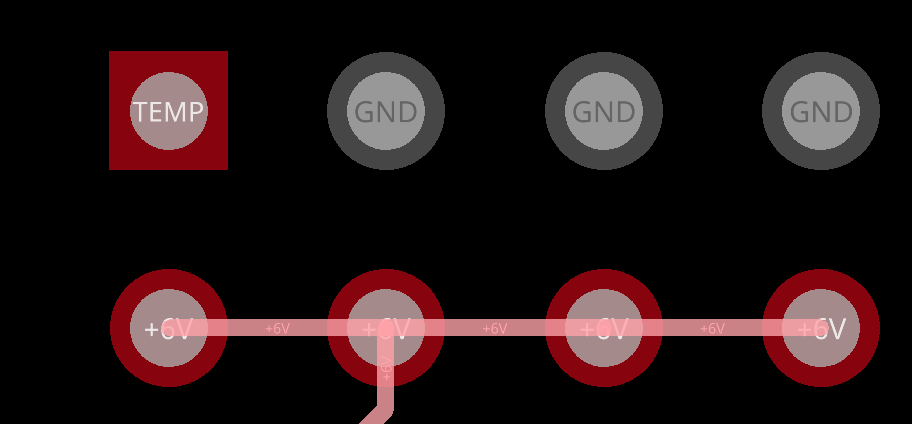

将以上原理图同步到版图,可以发现插件上面一排原本都是 GND网络,现在Pin#1名为 TEMP。直观起见,GND网络被赋予了灰色,红色是顶层Pin的颜色。

4.3. 布置Via Array

Place Via Array,网络是 TEMP,这样布置时就会自动避开器件接地管脚(因为它们网络名为 GND)。

注意:插件Pin#1的网络是 TEMP,所以仍然可能有少数的盘中孔在这个Pin周围,但是只是一个Pin的范围,手动删除很简单。

4.4. 使用Query找到这些过孔并重新赋值(20241009修改)

在Find菜单中选择 Find by Query...,如下图所示,查找所有网络为 TEMP的过孔。

我这里是已经修改完的,所以没查找到,正常是可以查找到的。在下面的搜索结果框中将这些过孔全选,可以发现它们在版图中也被选中了。

换到版图页面,右键选中的过孔,点击 Assign net to via,将这些过孔的网络重新赋值为 GND。

最后在原理图中将 TEMP网络还原成本来的名字。并同步到版图。

至此就完成了过孔布置,这些过孔是按照不同名网络的DRC规则来布置,然后才换到同名网络的,因此不会出现盘中孔。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· winform 绘制太阳,地球,月球 运作规律

· 超详细:普通电脑也行Windows部署deepseek R1训练数据并当服务器共享给他人

· 上周热点回顾(3.3-3.9)

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· AI 智能体引爆开源社区「GitHub 热点速览」