Synopsys DC的使用

| 日期 | 版本 | 内容 |

|---|---|---|

| 2024/01/12 | V0 | 初版 |

| 2024/01/18 | V1 | 根据书籍内容添加“3.3 综合脚本”内容 |

SDC软件即Synopsys Design Compiler,其对应的时序约束文件为Synopsys Design Constraint,缩写都是SDC。

1. SDC软件配置

SDC语法本质上是特殊的TCL语句,因此TCL语句都可以在SDC中使用,不过SDC还有一些TCL没有的语句。

1.1. 设置数字库

1.1.1. 库相关系统变量/术语解释

以下英文解释来自Synopsys ug-dcug(deisgn compiler ug)。

-

link_library/local_link_library

For a design to be complete, all cell instances in the design must be linked to the library

components and designs that are referenced. This process is called linking the design or

resolving references. To resolve references, Design Compiler uses the link libraries set by

the following variables and attribute:• The

link_libraryapplication variable lists the libraries and design files that Design

Compiler uses to resolve references.

Design Compiler searches the files listed in thelink_libraryvariable from left to right,

and it stops searching when it finds a reference. Specifying an asterisk in the

link_libraryvariable means that Design Compiler searches loaded libraries in

memory for the reference. For example, if you set thelink_libraryvariable to

{"*" lsi_10k.db}, Design Compiler searches for the reference in memory first and then in

the lsi_10k library.

• Thelocal_link_libraryattribute lists the design files and libraries added to the

beginning of thelink_libraryvariable during the link process. Design Compiler

searches files in thelocal_link_libraryattribute first when it resolves references.

You can set this attribute by using theset_local_link_librarycommand.

• Thesearch_pathvariable specifies a list of directory paths that the tool uses to find logic

libraries and other files when you specify a plain file name without a path. It also sets the

paths where Design Compiler can continue the search for unresolved references after it

searches the link libraries.

If Design Compiler does not find the reference in the link libraries, it searches in the

directories specified by thesearch_pathvariable, as described in Specifying a Library

Search Path.link_library就是SDC软件可能会调用的库,将这些库与软件link起来了,但是不一定会用到。

-

target_library

Design Compiler selects functionally correct gates from the target libraries to build a circuit

during mapping. It also calculates the timing of the circuit by using the vendor-supplied

timing data for these gates.

To specify the target libraries, use thetarget_libraryvariable. Your should specify only

the standard cell libraries that you want Design Compiler to use for mapping the standard

cells in your design, such as combinational logic and registers. You should not specify any

DesignWare libraries or macro libraries, such as pads or memories.

For information about specifying target libraries, see Specifying Logic Libraries.target_library就是SDC综合实际用到的库,里面的所有库地位是均等的,对于每个器件function,SDC先根据功能挑出器件,然后根据约束从中选择一个最优的。

-

symbol_library

Symbol libraries contain definitions of the graphic symbols that represent library cells in

design schematics. Semiconductor vendors maintain and distribute the symbol libraries.

Design Compiler uses symbol libraries to generate schematic views. You must use Design

Vision to view the schematic. When you generate a schematic, Design Compiler performs a

one-to-one mapping of cells in the netlist to cells in the symbol library.

Each Design Compiler installation includes a default symbol library file, generic.sdb, located

in the \$SYNOPSYS_ROOT/libraries/syn directory. This file contains generic symbols and all

the Verilog standard logic gate symbols.

To load the schematic symbols, Design Vision first checks thesymbol libraryfiles that you

specify with the symbol_library variable. For example, asymbol_libraryvalue of

tech.sdb prompts the tool to search for the symbols in the file named tech.sdb.

If the specified libraries do not contain the symbols, the tool searches the generic.sdb file in

the $SYNOPSYS_ROOT/libraries/syn directory. If no match is found, the tool displays the

cell instance as a rectangle, which is the default representation.symbol_library定义了原理图的器件,感觉这个用处不是很大,只是为了好看。只要网表稍大一点都不可能进去仔细找逻辑器件的功能的。

-

synthetic_library

A DesignWare library is a collection of reusable circuit-design building blocks (components)

that are tightly integrated into the Synopsys synthesis environment. During synthesis,

Design Compiler selects the component with the best speed and area optimization from the

DesignWare library.

DesignWare components that implement many of the built-in HDL operators are provided by

Synopsys. These operators include +, -, *, <, >, <=, >=, and the operations defined by if and

case statements.

You can develop additional DesignWare libraries at your site by using DesignWare

Developer, or you can license DesignWare libraries from Synopsys or from third parties. To

use licensed DesignWare components, you need a license key for the components.

If any DesignWare component set in thesynthetic_libraryvariable requires a

DesignWare license, Design Compiler checks for this license. You do not need to specify the

standard synthetic library, standard.sldb, that implements the built-in HDL operators. Design

Compiler automatically uses this library

By default, if the dw_foundation.sldb library is not in the synthetic library list but the

DesignWare license has been successfully checked out, the dw_foundation.sldb library is

automatically added to the synthetic library list. This behavior applies to the current

command only. The user-specified synthetic library and link library lists are not affected.

All DesignWare hierarchies are, by default, unconditionally ungrouped in the second pass of

the compile. You can prevent this ungrouping by setting thecompile_ultra_ungroup_dw

variable tofalse. The default istrue.DesignWare Library,我的理解是就像IP核一样,里面包含了一些常用的略高层的HDL模块。估计引入这样的库是更利于SDC综合。

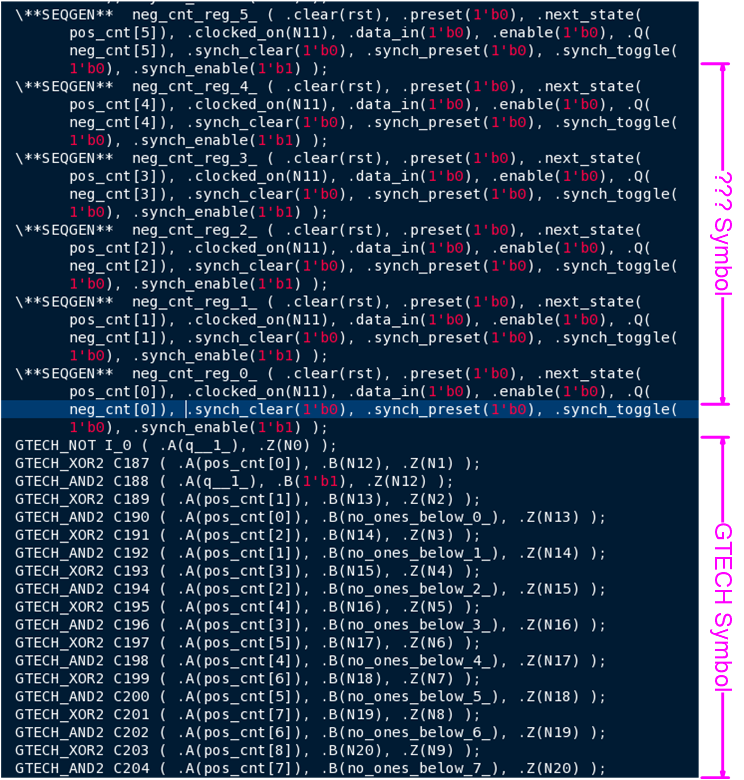

试想顶层HDL的功能是b = a*4,这样的乘法在verilog里面可以直接写,但这不是一个直接的电路,需要综合。尽管任何综合器都能对这样的简单乘法综合出正确的结果,但是因为DesignWare是针对SDC设计的,它更适合用于SDC综合,综合出的结果可能会优于没有这个库。GTECH Library[1]与上面的DesignWare Library对应,也是一个HDL虚拟库,不过其中应该只有基本逻辑门,推测可能连触发器都没有,理由参下图片。

一般就把

synthetic_library设为dw_foundation.sldb,这是SDC自带的DesignWare,GTECH不需要用语句引用。

1.1.2. SDC综合过程解释

从以上解释可以看出SDC的综合过程:

-

使用synthetic library(通常是逻辑门库GTECH和高层HDL功能库DesignWare)将逻辑综合为通用逻辑。

在查找这两个库的时候,发现很多资料来自于Synopsys Synplify,这是一款FPGA逻辑综合软件。这样也印证了上面的说法:这两个库是通用的,Synplify可以将逻辑综合为通用网表,再用FPGA制造商的专用库去替换,得到FPGA专用网表。

-

在link library中寻找target library,寻找与HDL抽象器件相同逻辑的器件,并根据约束选择最优的一种。将抽象器件全部替换为库器件,就完成了综合过程。

为了印证以上的说法,进行了如下实验:

使用SMIC130的数字库,MOS电压有两个系列分别为RVT、HVT。也就是说有两套数字库可用。

-

link_library为空。

综合结果:有GTECH器件,另一类器件不知道是否来自于DesignWare,像是寄存器。库文件.db和.sldb文件都是打不开的,没法验证。

-

link_library为其中一个,target_library为另一个。

综合结果:同第1次。 -

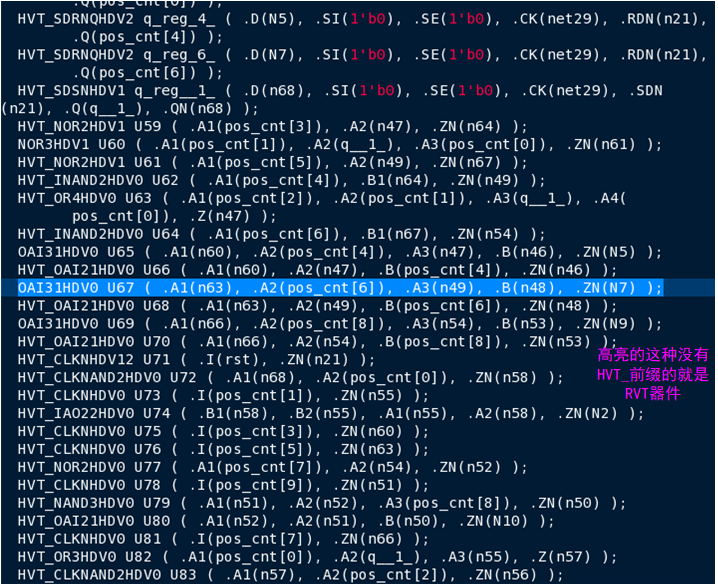

link_library、target_library都是HVT或RVT。

综合结果:器件全是对应库的。 -

link_library、target_library都包含了HVT和RVT。

综合结果:两种器件都有,但大多数为HVT。

RVT(Regular Voltage Threshold)和HVT(High ~ ~)代表MOS的阈值高低。阈值越低,饱和电流越小,速度越快;但是漏电流越大,功耗越大[2]。因此HVT比RVT更慢、更低功耗。

在本例的低时序要求情况下,约束器转而约束功耗,因此大都选用HVT器件。这是正常合理的结果。 -

由上总结SDC库的一般用法:

- 防止混淆起见,保证link_library和target_library的内容一致。link_library和target_library感觉还是有些不明白,但是反正最终网表一定是来自于target_library。

- synthetic_library就用默认的dw_foundation.sldb,一般不需要额外添加。

- 一般Vendor提供的PDK都会包含Typical、Fast、Slow三个工艺角,快慢都是极端的情况,是否需要如此严格的约束应该视需求决定。

- 在有多个仅阈值电压不同的数字库系列时,建议将这些库全部使用,这样能得到最好的综合结果。

- PDK lib是有延时的,自带的synthetic library是没有的,因此如果综合成功调用了PDK库,综合不会那么快。

1.1.3. 连接数字库的SDC语句实例

以下列举一个实际的脚本:

第一步:定义所有库的变量,尽管可能不一定用到。

set LIB_STDCELL_TC_SVT "scc013ug_hd_rvt_tt_v1p2_25c_basic"

set LIB_STDCELL_WC_SVT "scc013ug_hd_rvt_ss_v1p08_125c_basic"

set LIB_STDCELL_BC_SVT "scc013ug_hd_rvt_ff_v1p32_-40c_basic"

set LIB_STDCELL_TC_HVT "scc013ug_hd_hvt_tt_v1p2_25c_basic"

set LIB_STDCELL_WC_HVT "scc013ug_hd_hvt_ss_v1p08_125c_basic"

set LIB_STDCELL_BC_HVT "scc013ug_hd_hvt_ff_v1p32_-40c_basic"

set LIB_STDCELL_PATH_SVT $DC_S_STD_LIB_PATH/rvt

set LIB_STDCELL_PATH_HVT $DC_S_STD_LIB_PATH/hvt

这里只是定义了TCL变量,只是把名字存下来。

第二步:将SDC默认库引入,一般只有dw_foundation.sldb。

set_app_var synthetic_library [list dw_foundation.sldb]

set_app_var link_library [list $synthetic_library * \

]

set_app_var target_library [list \

]

注意,link_library中也是有dw_foundation的,之前实验中只是在此基础上再增添新的。

现在列表没有PDK库,后面用轮询添加。

第三步:将PDK数字库引入,建立库列表。

foreach link_lib $DC_S_STD_LINK_LIB {

set lib_var LIB_STDCELL_${DC_S_STD_LIB_CORNER}_${link_lib}

set lib_name [set $lib_var]

lappend link_library ${lib_name}.db

}

foreach target_lib $DC_S_STD_TARGET_LIB {

set lib_var LIB_STDCELL_${DC_S_STD_LIB_CORNER}_${target_lib}

set lib_name [set $lib_var]

lappend target_library ${lib_name}.db

}

foreach link_lib $DC_S_STD_LINK_LIB {

set path_var LIB_STDCELL_PATH_${link_lib}

set path_name [set $path_var]

lappend search_path ${path_name}

}

用列表循环将需要的库名字拼成一个列表。注意以上lappend <list> <element>(list append)表示在列表末尾插入新的值。

1.2. 指定顶层模块

set DC_S_DESIGN <topmodule_name>

1.3. 系统变量

1.3.1. 设置SDC系统变量语句

从dc_ug来看,用set_app_var这种Synopsys定制命令比用set这种通用TCL命令更直观,能让人看出来你设的是软件的固有变量,而不是一个任意变量,语法为:

set_app_var <var_name> <var_value>

1.3.2. 查看系统变量

在dc_shell环境下输入命令printvar <var_name>可以打印现有的变量,缺省表示所有(后同),如果自己没有定义变量,那么就只有系统变量,不过选择全部变量时,输出结果好像是在vim环境中显示的,不会用。

输入命令get_app_var <var_name>可以查看系统变量的值

输入命令report_app_var <var_name>可以查看系统变量的属性和值。

但是似乎没有办法知道每个变量代表的意义。

1.4. 指定SDC工作模式

set DC_S_IS_FLATTEN true

set DC_S_IS_SYN true

set DC_S_IS_NET true

set DC_S_IS_APR false

set DC_S_BLOCK_DB netlist

set DC_S_UPF_FLOW true

从名称都容易理解其作用。这些变量在运行脚本中有用到。

2. SDC Design Vision GUI的使用

2.1. 启动GUI界面

SDC实际上是有GUI界面的,但是好不好用不清楚,我觉得在综合完之后用来看一下网表原理图还是可以的,总比直接看网表verilog要直观的。

方法是,首先找到SDC安装路径(这一点无论是否是GUI都是一样的):

export PATH="/cdsmgr/synopsys/syn/O-2018.06-SP1/bin:"$PATH

export DC_HOME=/cdsmgr/synopsys/syn/O-2018.06-SP1

找到路径后可以用SDC自带的命令design_vision,在不加参数情况下是默认进入GUI环境的。

或者可以从dc_shell跳入GUI环境,依次执行以下命令:

dc_shell

gui_start

GUI没有过多摸索怎么用,我都是在里面直接source脚本运行。GUI使用可以参考Synopsys DC ug-dvug(design vision ug)。

里面依然可以输入SDC/TCL命令,也能完全看到输出结果和提示。

直觉告诉我GUI可能适合用于迭代设计,可以看原理图综合结果是否合理,如果不合理就立即添加SDC命令再重新综合。

2.2. 查看系统变量

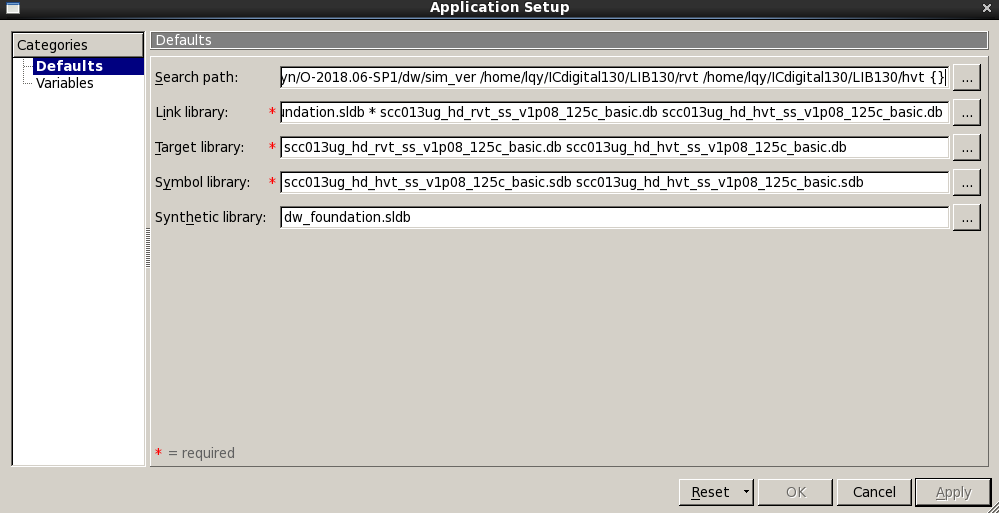

在GUI中点击File-Setup...进入以下界面。

在之前的脚本中已经定义了库变量,可以在此处检查是否正确。

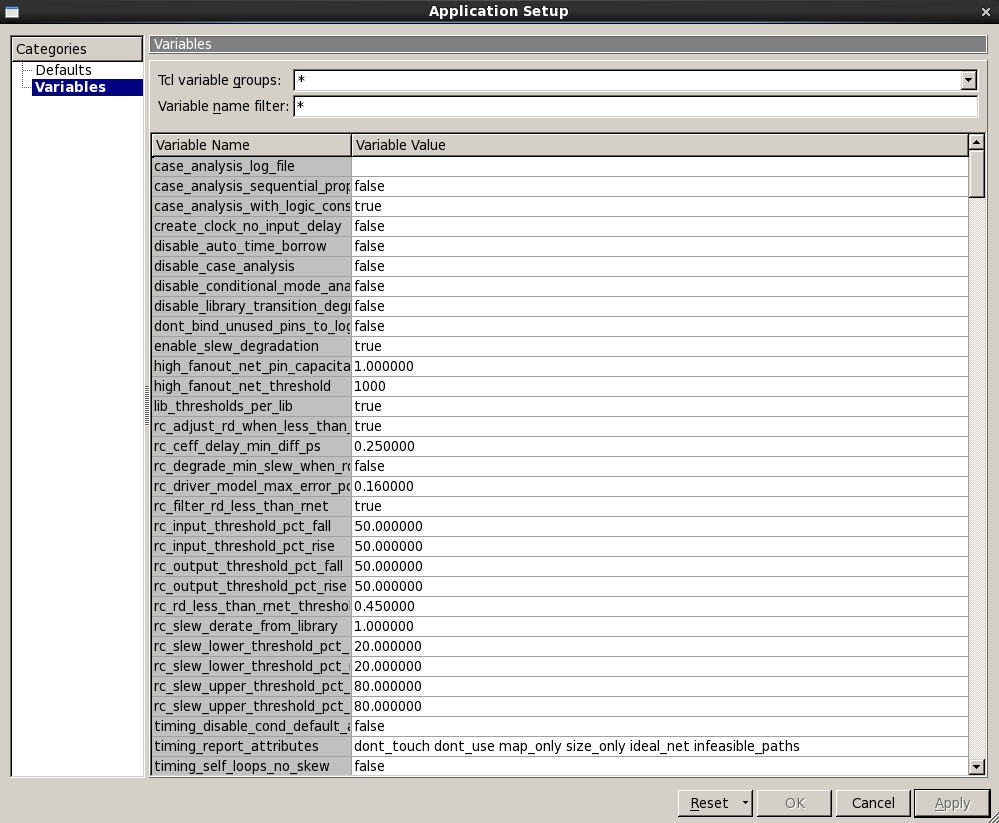

此外可以看到SDC软件的所有系统变量并可以编辑。

2.3. 查看综合结果

选中某个模块,在工具栏中找到Create Schematic of Selected Objects按钮即可创建原理图。估计symbol library的symbol就是用在这里的。

3. 启动SDC综合

3.1. 从命令行启动

#! /bin/csh -f

set dir_list = "log report result"

setenv run

foreach var ($dir_list)

if ( ! -d $var )then

mkdir $var

endif

end

dc_shell-xg-t -f ./runset_dc.tcl | tee ./log/dc_syn.log

前面的循环是为了创建log、report、result三个文件夹。最后一句启动SDC。

dc_shell是SDC软件的shell,紧接着的参数是运行模式,可以不接参数,接-t或-xg-t,分别是sh mode、tcl mode、XG mode,一般最后一项综合结果最好[3]。-f表示自动执行的tcl脚本。后面的tee命令是标准linux命令,生成了指定的log文件,从内容来看就是把SDC运行过程中命令行的所有显示全部记录。

3.2. 从GUI启动

根据实验,如果想要从GUI启动,就要加上-gui参数,并且注意综合的脚本中不要有-exit,否则在GUI打开之前就退出了。自动打开了GUI之后,结果可以在GUI中查看。

注意:以上的两种方法只是启动软件,并不会自动开始综合过程。综合还有一个专门的配置、综合脚本,比较复杂。

3.3. 综合脚本

此部分给出一般的综合脚本格式[4]。

DC综合的一般顺序:analyze, elaborate, link, uniquify

按照参考书内容,这几步的语法如下:

analyze -format verilog $xxx.v ;#<xxx> 是定义的顶层模块名

elaborate $xxx ;#elaborate使用GTECH抽象器件综合网表,此时实际数字库都还没有link

current_design $xxx ;#设置当前设计名

link ;#按照link_library去link

uniquify -force ;#去除设计中多次调用相同实例但只有一个定义的情况

compile_scan ;#编译,从GTECH抽象库编译为实际数字库

其余部分其实就是设定系统变量、设定约束、输出文件等。

4. SDC的输出

在本例使用的脚本中,让SDC输出了以下文件:

- 网表verilog文件(.v)

- 延时文件(.sdf)

- Synopsys验证文件(.svf):用于Sysnopsys Formality进行形式验证

- Synopsys特殊database文件(.ddc):包含约束和网表,可以认为是Synopsys特别版的简化db文件,只能用于Synopsys的数字后端(ICC)

- 全部信号的约束文件(.sdc)

5. 附录

5.1. Synopsys DC User Guide

dvug文件、dcug文件、tclug文件都是Synopsys DC的官方ug的一部分。

网盘链接:[链接:https://pan.baidu.com/s/1eRUnd5MYEsFKopW0S333UQ?pwd=85q5 提取码:85q5 ]

5.2. FPGA-SDC User Guide

Quartus支持SDC语法,Vivado的xdc语法也基本与SDC一致。学习SDC语法也可以找Quartus、Vivado关于SDC的介绍。

已知的Vivado文档:

- ug835-vivado-tcl-commands-en-us-2023.2

- ug945-vivado-using-constraints-tutorial-en-us-2023.2

已知的Quartus文档:

- SDC and TimeQuest API Reference Manual

5.3. Synopsys-GoTo Webinar

这是Synopsys官方网站指向的一个Webinar视频,需要输入一些信息但不用注册。

About Gtech and DesignWare library | Forum for Electronics (edaboard.com) ↩︎

What's the main difference between dc_shell, dc_shell-t, dc_shell-xg-t? | Forum for Electronics (edaboard.com) ↩︎

高级ASIC芯片综合-使用Synopsys Design Compiler Physical Compiler 和PrimeTime(第二版)(封面参下)

↩︎

↩︎

浙公网安备 33010602011771号

浙公网安备 33010602011771号