使用Quartus+ModelSim联合仿真

最后修改日期:2023/02/17

本文前提是用Verilog Testbench文件(.vt) 仿真。相较于波形仿真而言,此方法较为通用。

下面以Quartus Prime 18.0 Standard + Mentor Graphics ModelSim SE-64 10.4为例说明。

1. Quartus选项设置

Quartus软件全局偏好设置。在此配置EDA软件。

点击Tools-Options…,找到General-EDA Tool Options,在ModelSim一栏中填入ModelSim可执行程序的路径,典型路径为:[INSTALL_DIR]\win64。

2. 创建vt文件

点击Processing-Start-Start Testbench Template Writer,会自动生成vt文件,vt文件的命名、顶层模块等与项目中设定的Top-Level Module一致,否则会出现错误:Top-level design entity "xxx" is undefined.

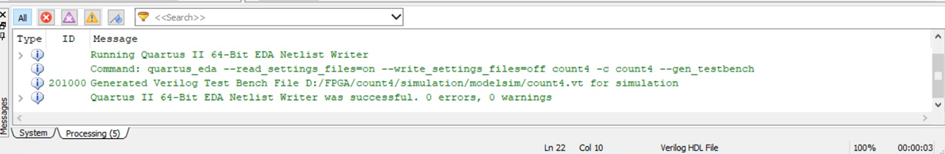

注意:生成vt文件之后,并不会自动打开文件,也不会自动引入到项目中。可以观察Quartus Message的提示,如下图所示:

注意 “Generated Verilog Test Bench File” 的提示。典型路径为:[PRJ_DIR]\simulation\modelsim\xxx.vt。

后面vt文件是否引入到项目中其实是不影响的。不过vt文件需要修改,如果不用Quartus打开修改,也可以用其它编辑器修改。

3. 修改vt文件

这部分不再多说。Template中的端口定义和实例化都已经完成,只需要设置波形(也就是always或initial块)。

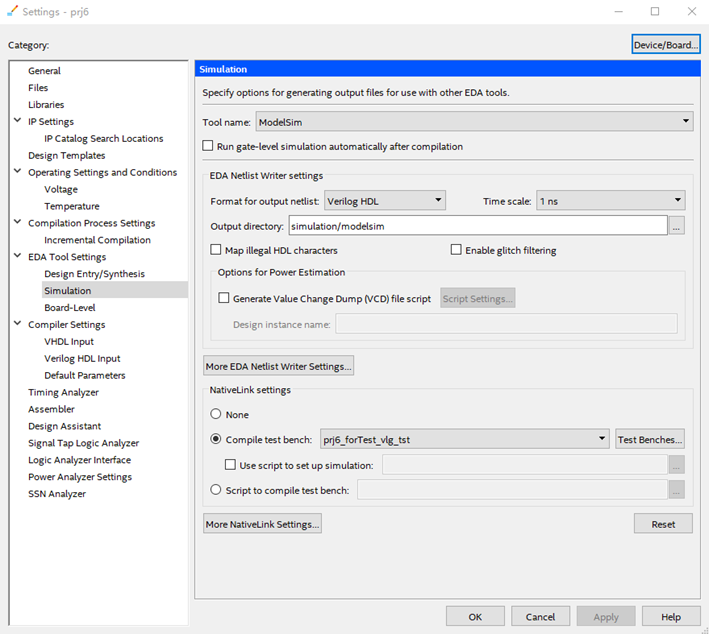

4. 仿真选项设置

点击Assignments-Settings…,找到EDA Tool Settings-Simulation。如下图所示:

一项项设置。Tool name是ModelSim,HDL语言自己选,Time scale决定仿真精度。

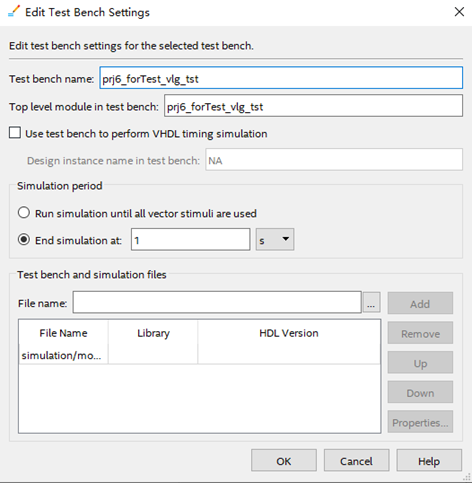

然后注意下方NativeLink settings,选择Compile test bench,然后点击Test Benches…,进去之后应当是空白。点击New…增加新的测试,如下图所示:

Top level module in test bench,去vt文件里看一下Top的名称,填进去。

稳妥起见,Test bench name与前述项保持一致。

End simulation at,也就是仿真停止时间。

然后下方添加 .vt文件,注意选完之后要点Add才能添加进来。

全部完成后点OK。

5. 启动仿真

功能仿真:Tools-Run Simulation Tool-RTL Simulation

时序仿真:Tools-Run Simulation-Gate Level Simulation…

会自动弹出ModelSim页面,自动仿真,自动展示波形。

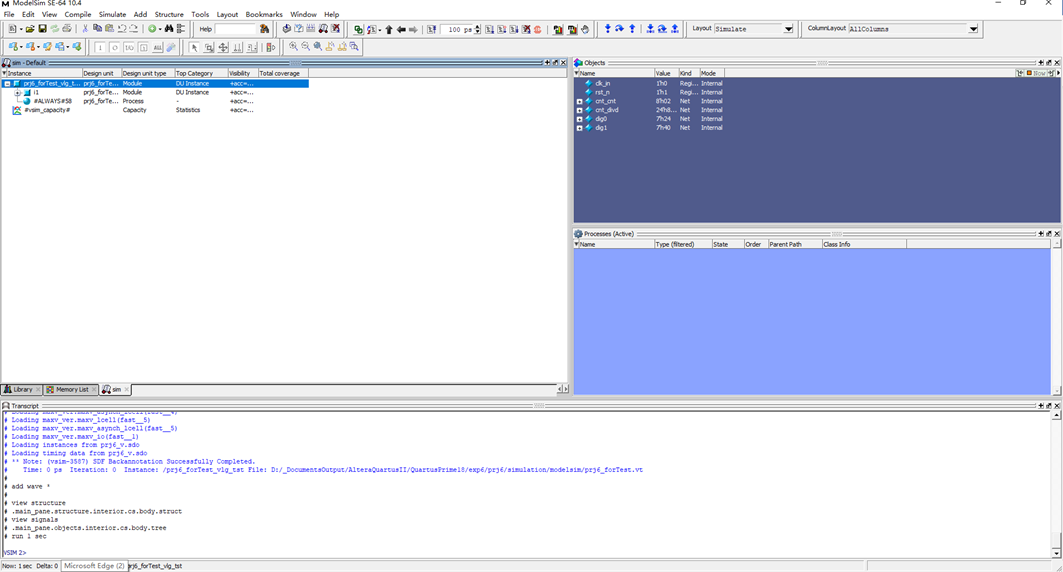

下图给出了ModelSim的界面:

在运行时,注意下方Transcript的提示,有Error而导致仿真不成功会以红字标出。

左下角会给出进度条,代表仿真时间进度。当仿真时间设置的比较长的时候,可以看这里观察仿真进度。

浙公网安备 33010602011771号

浙公网安备 33010602011771号