AXI-GPIO 按键 LED

官方文档,PG144

可以学如何从block design IP ?中看PG144文档。

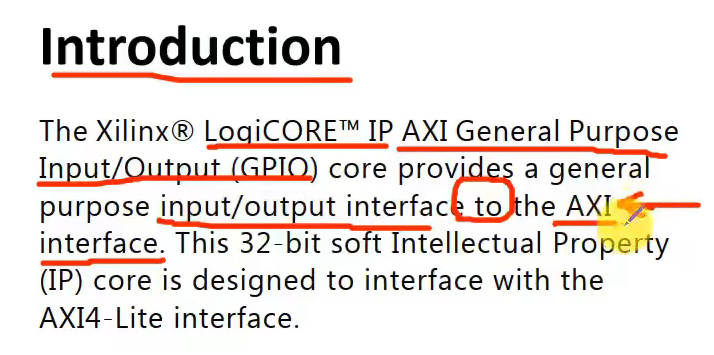

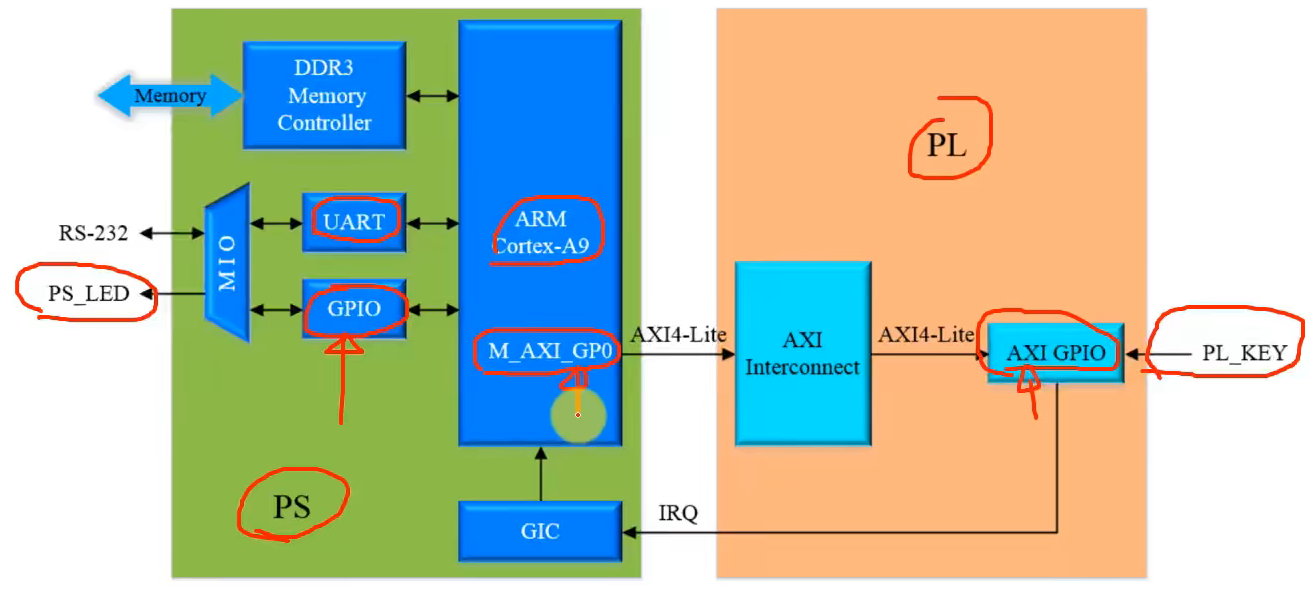

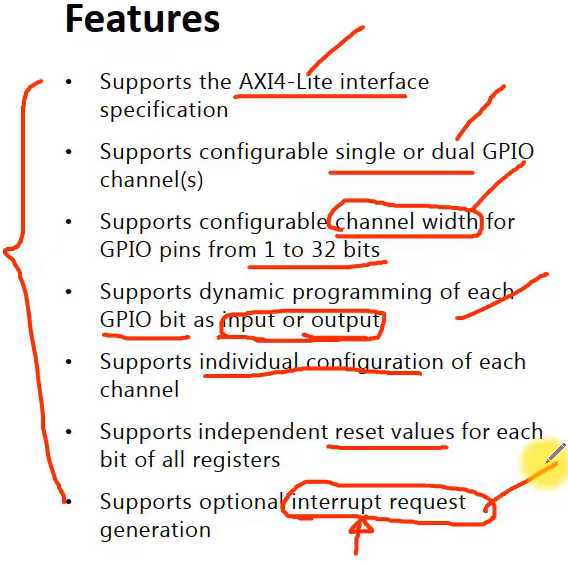

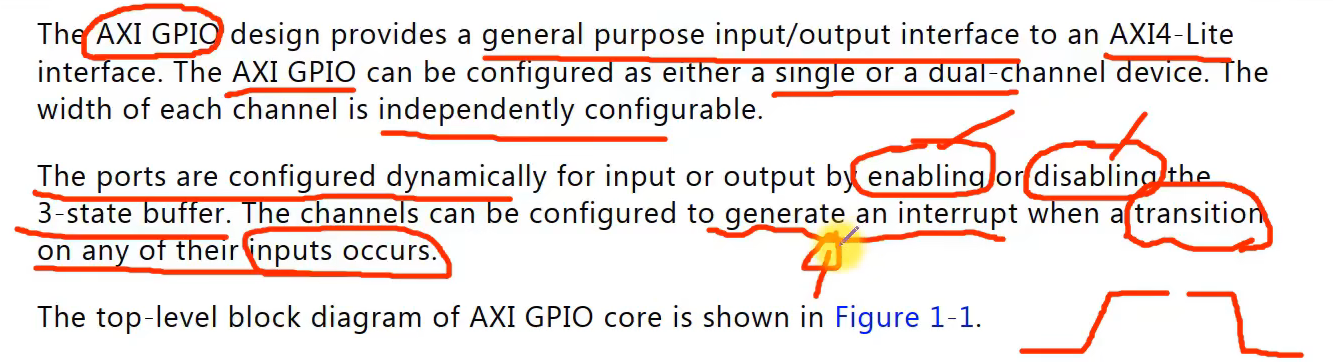

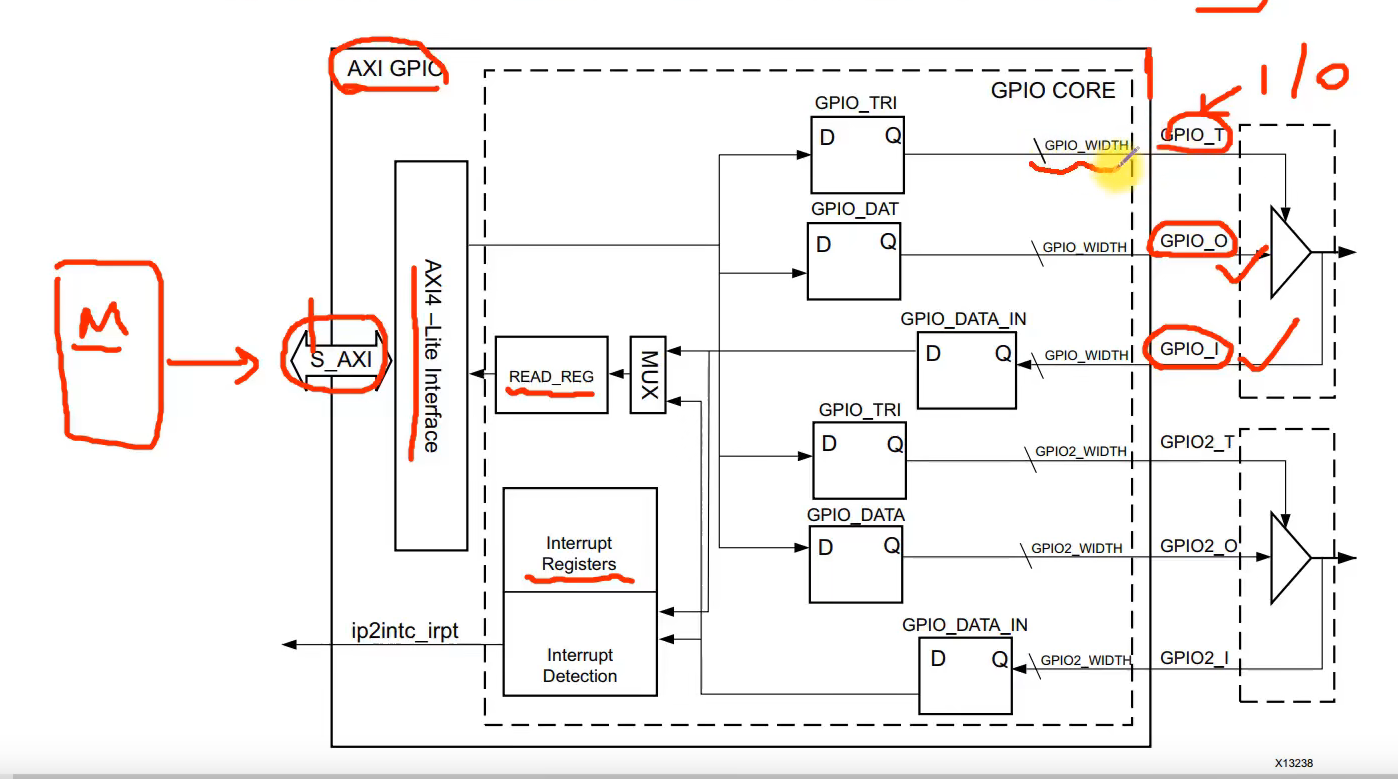

逻辑IP,即在ZYNQ FPGA里面能实现的IP。AXI GPIO,提供了通用的输入输出接口到AXI接口。它是一个软核的IP,被设计来连接AXI4-LITE接口。

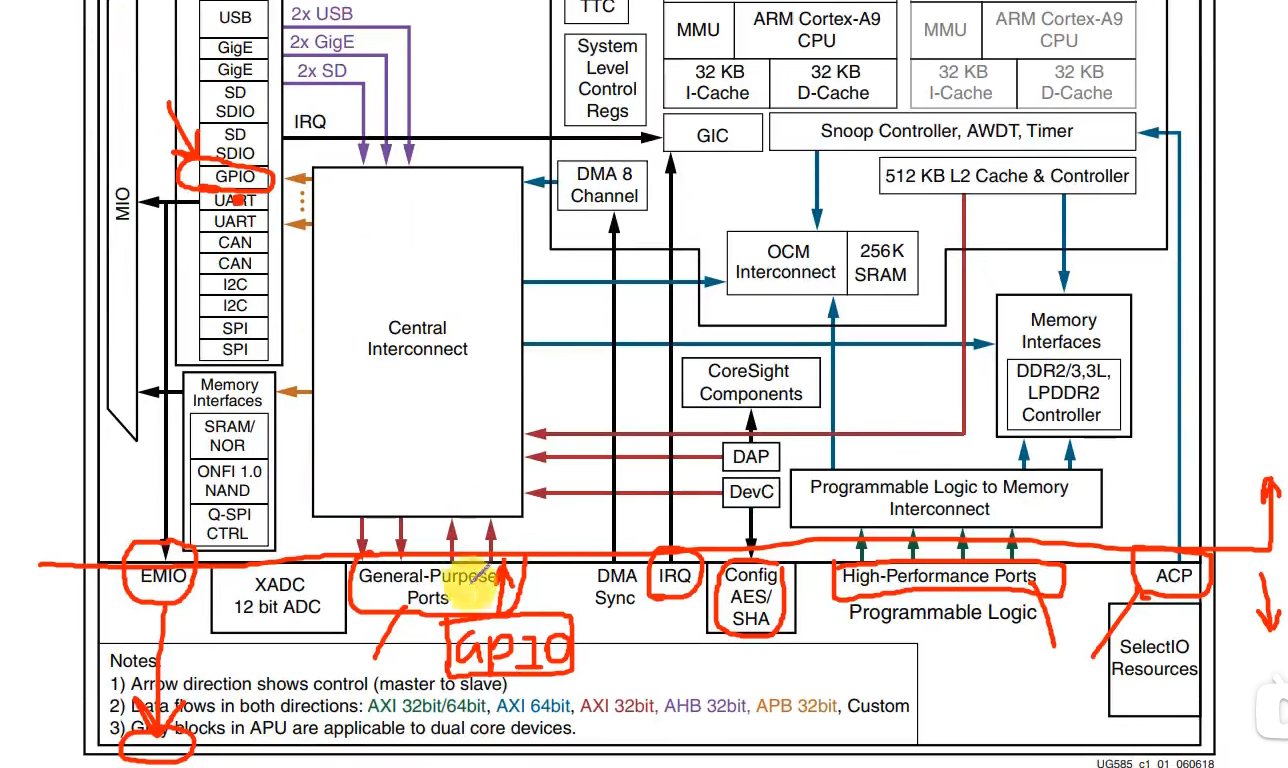

PROCESS SYSTEM(PS) 的 I/O PERIPHERALS (外设) 的 GPIO接口 是硬核

而 (IP) AXI-GPIO是一个软核的GPIO

硬核:芯片里面有这样的电路

软核:芯片里边实际上是没有这样的电路,是通过FPGA的逻辑去搭出来的,这样实现具有一定功能的电路成为软核

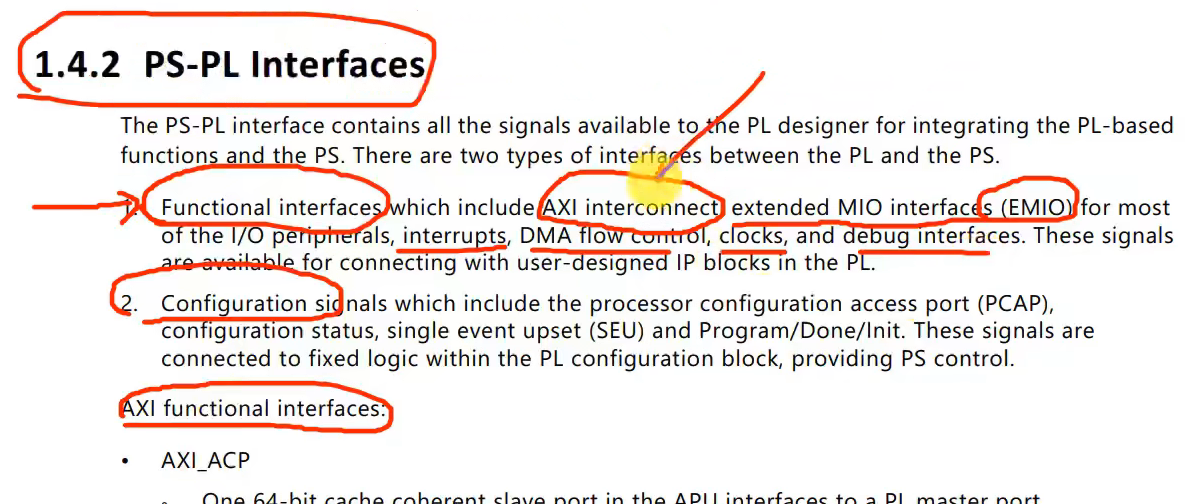

软核GPIO与PS部分有接口,为AXI接口

本次用一下GP接口

通过调用AXI-GPIO核,使用中断机制,实现底板上PL端按键控制核心板上PS端LED;

存储器映射:读操作写操作,执行操作的同时都给一个对应的地址。存储器每一个存储空间都有一个地址。

通过使能或关闭使能 三态缓冲器来对输入,输出进行动态配置(3-state buffer可以决定I/O是作为输出还是作为输入)。

每一个通道可以通过配置来产生中断,如果AXI GPIO IP核的输入引脚的电平状态发生改变,就可以产生一个中断信号,不管是从高电平变成低电平,还是低电平变成高电平(0到1,或者1到0 称为一个转换)

GPIO_T:当GPIO要控制LED时,为输出,其为0.当GPIO要控制KEY时,为输入,其为1.

当引脚的信号发生改变,就会产生中断(如果有勾选使用的话)

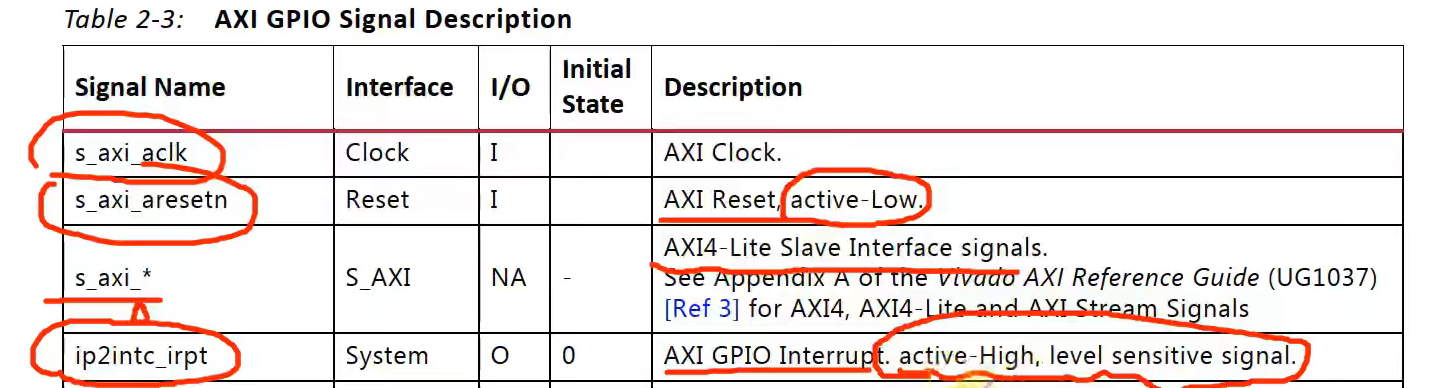

复位:低电平有效

s_axi_*: *表示一组信号

中断:高电平有效,电平敏感类型信号

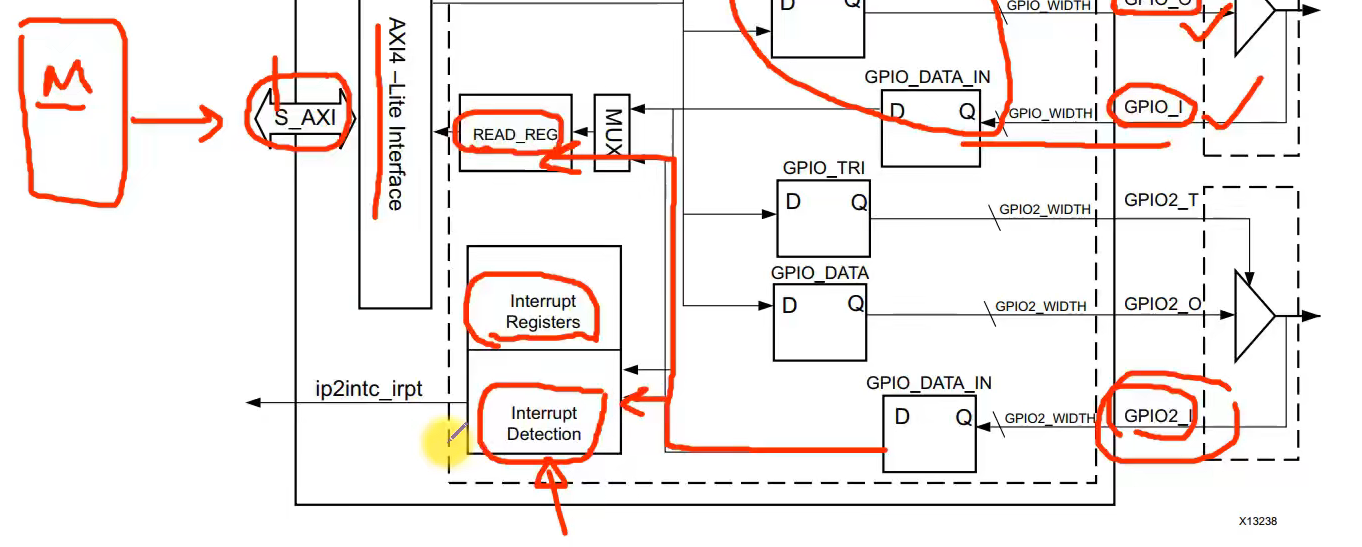

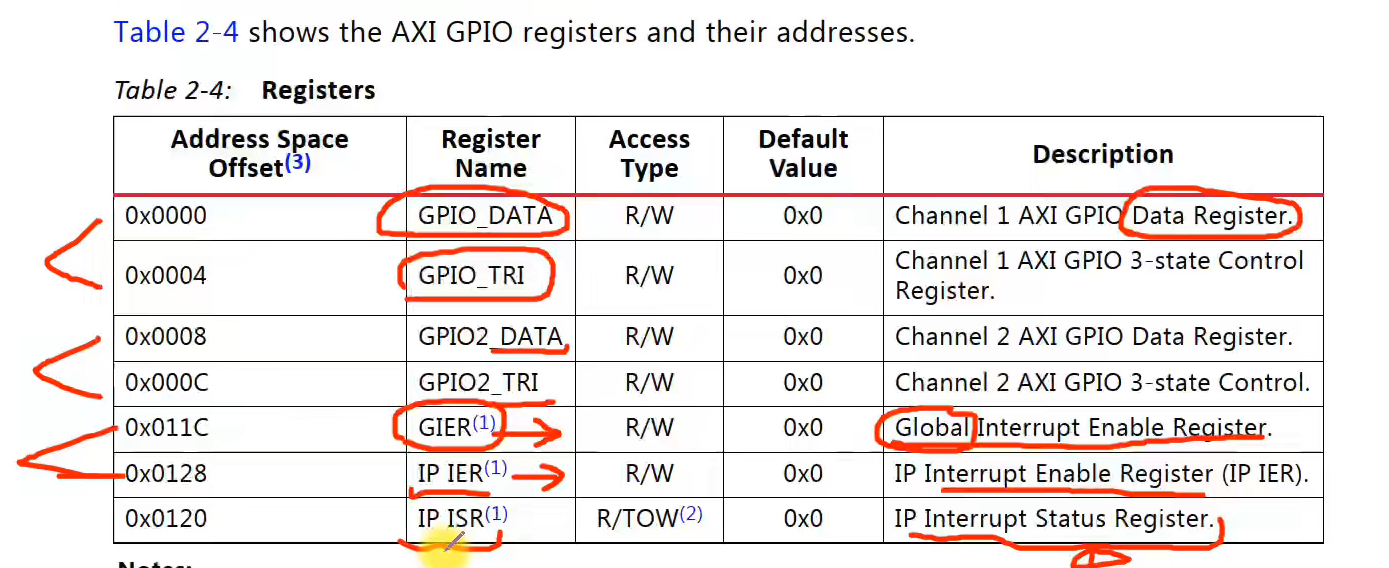

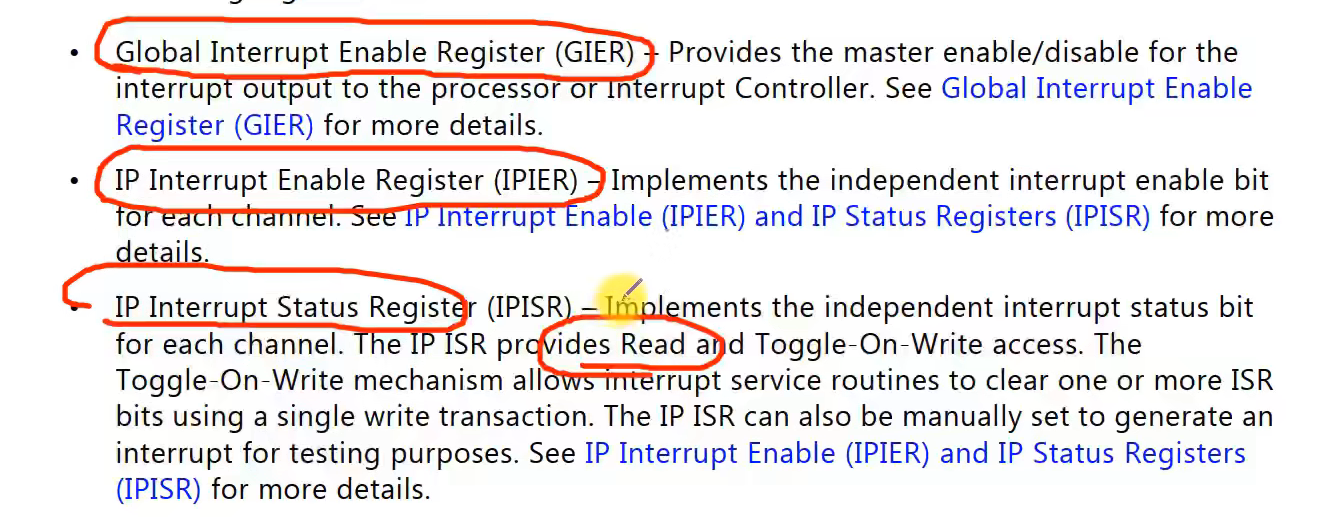

GIER全局中断(总开关),IP_IER(子开关),都打开才能进行中断。中断状态寄存器,可以读取中断,也可以清除中断

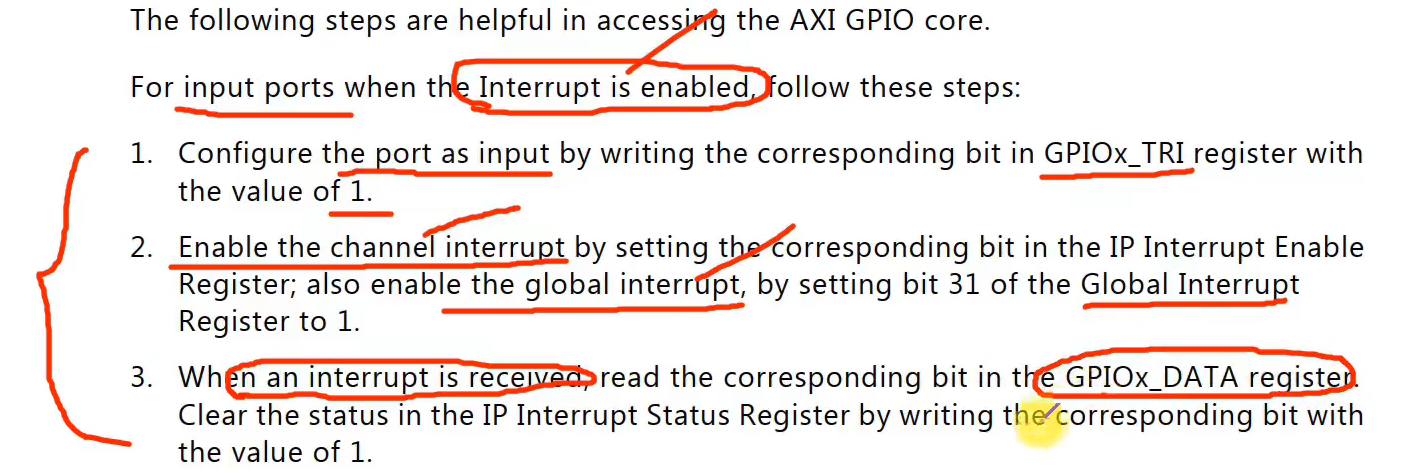

使用中断的话,对于输入部分

1.赋值为1设为输入

2.打开中断

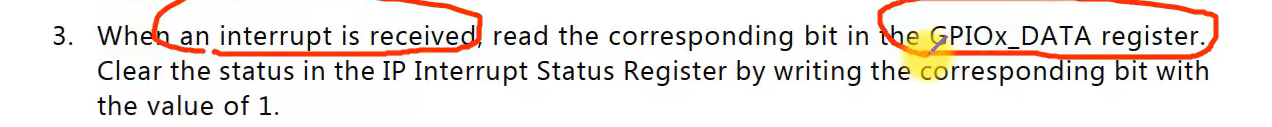

3.读取数据,然后清除中断状态寄存器,才能方便下次去检测中断的产生。

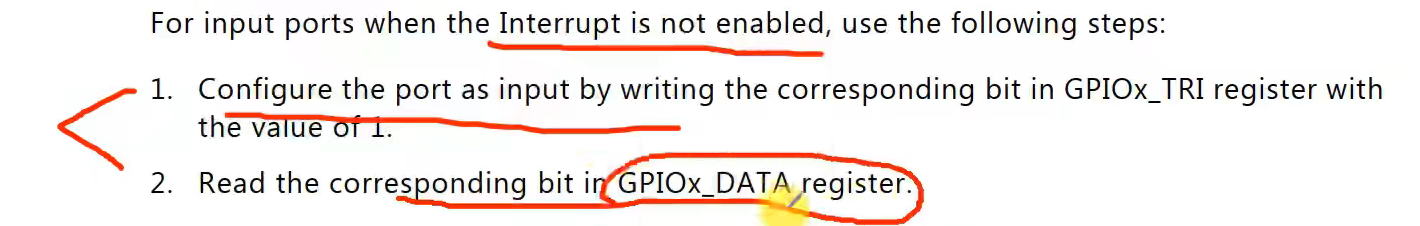

不使用中断的话,对于输入部分

1.设为输入

2.直接读取数据

对于输出

1.设为输出

2.王寄存器里写数据

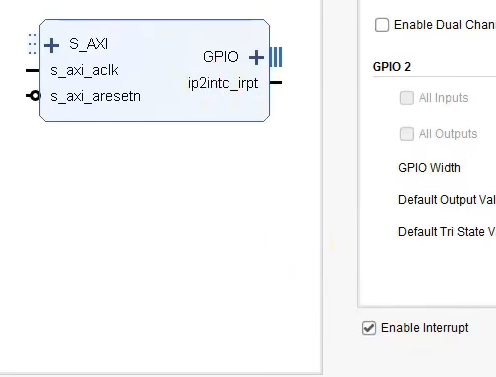

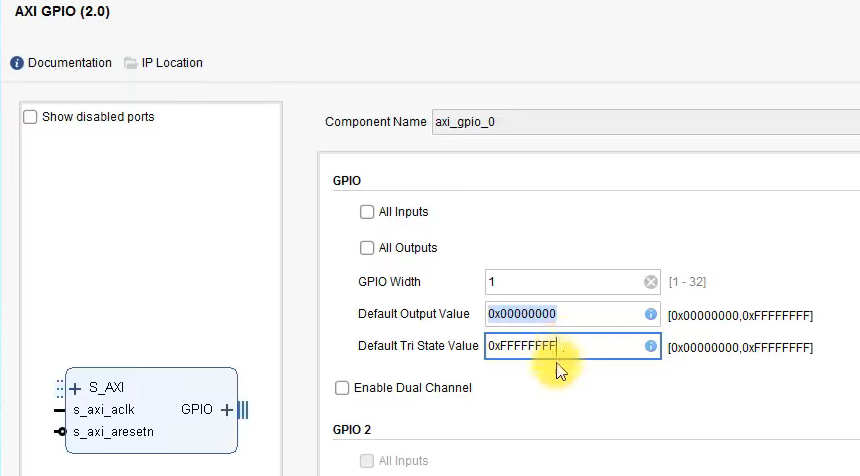

DEFAULT OUTPUT VALUE:作为输出时的值

DEFAULT TRI STATE VALUE :可看到默认的时候是全部设置为输入了

在输入模式下可以使用中断

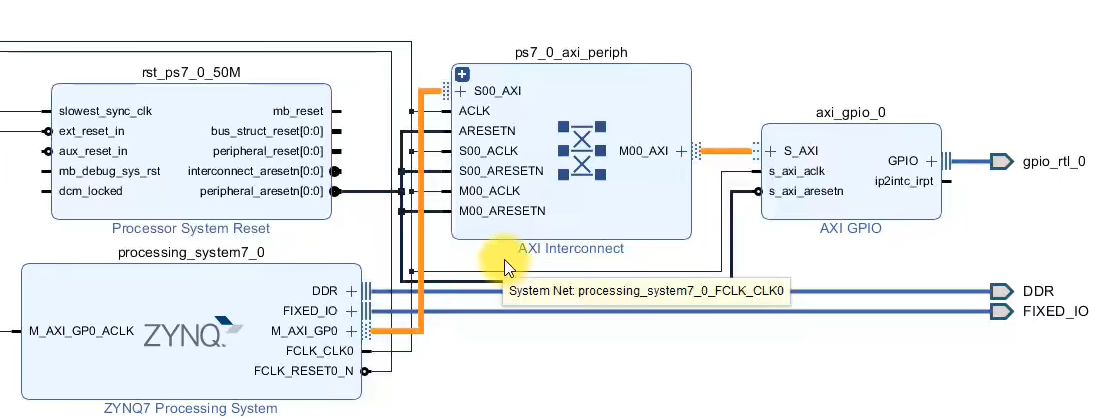

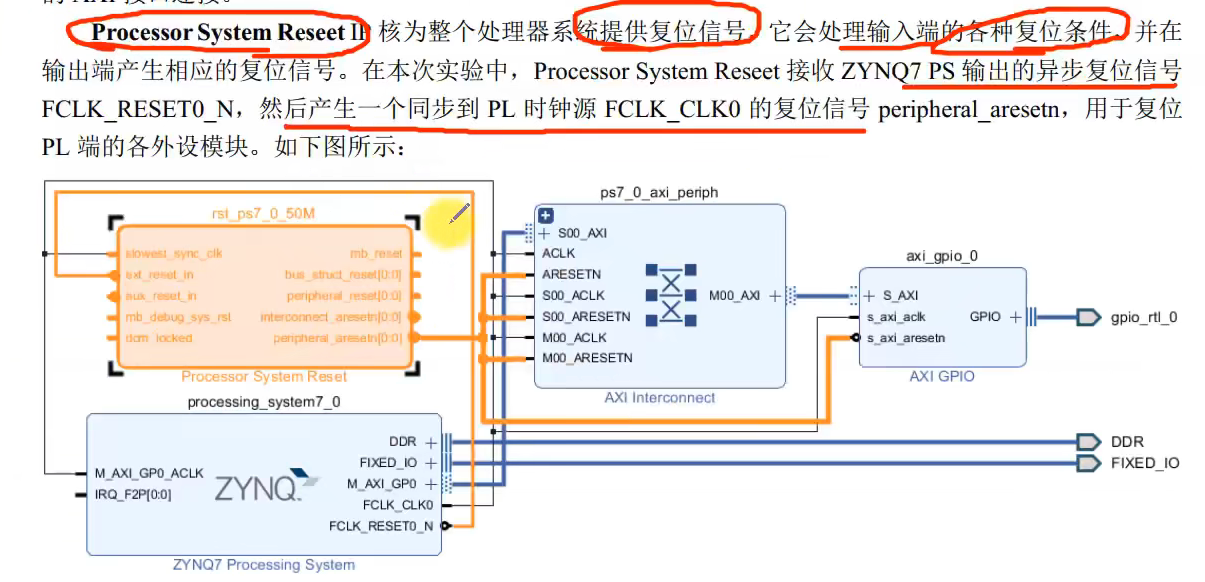

PS7_0_AXI_PERIPH不需要添加,会自动帮我们添加 。管理并指挥所连接的AXI接口之间的通信,可以实现一对多,多对1,多对多的AXI接口连接。

本次之中只有一个AXI IP,比较简单。如果有多个,就需要 PS7_0_AXI_PERIPH 来指挥连接,帮助我们主器件跟多个IP进行仲裁,管理。

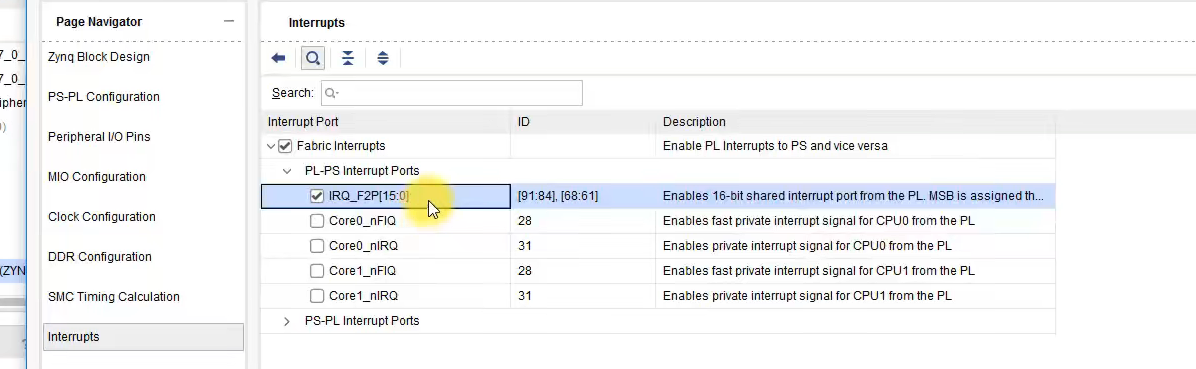

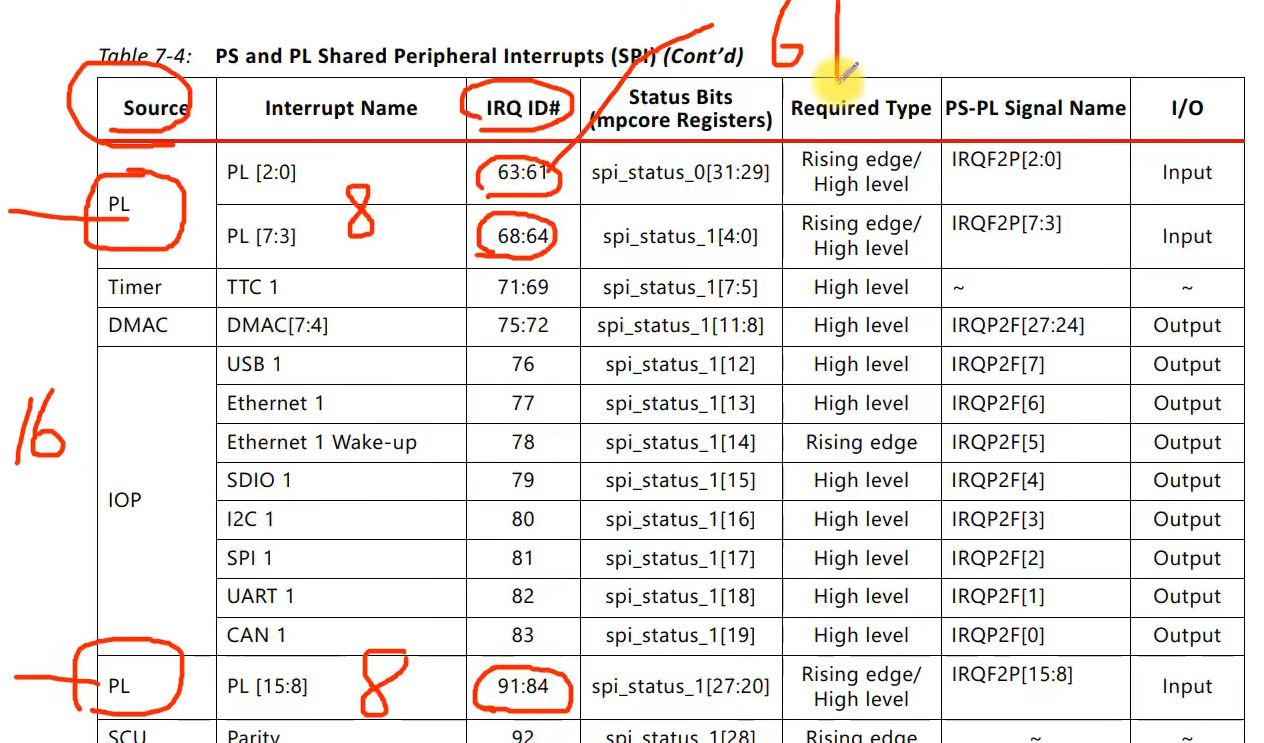

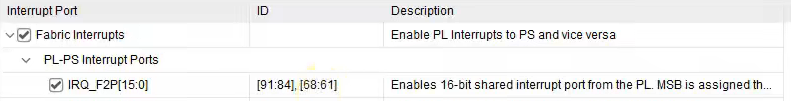

从PL到PS的中断

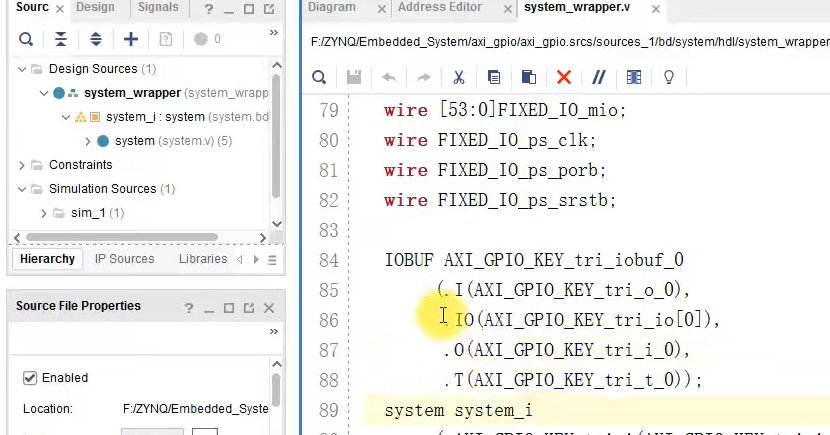

完成顶层文件自动帮我们添加3态缓冲器。

这是我们在PL里面使用FPGA资源所实现的软核GPIO

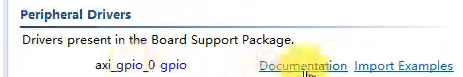

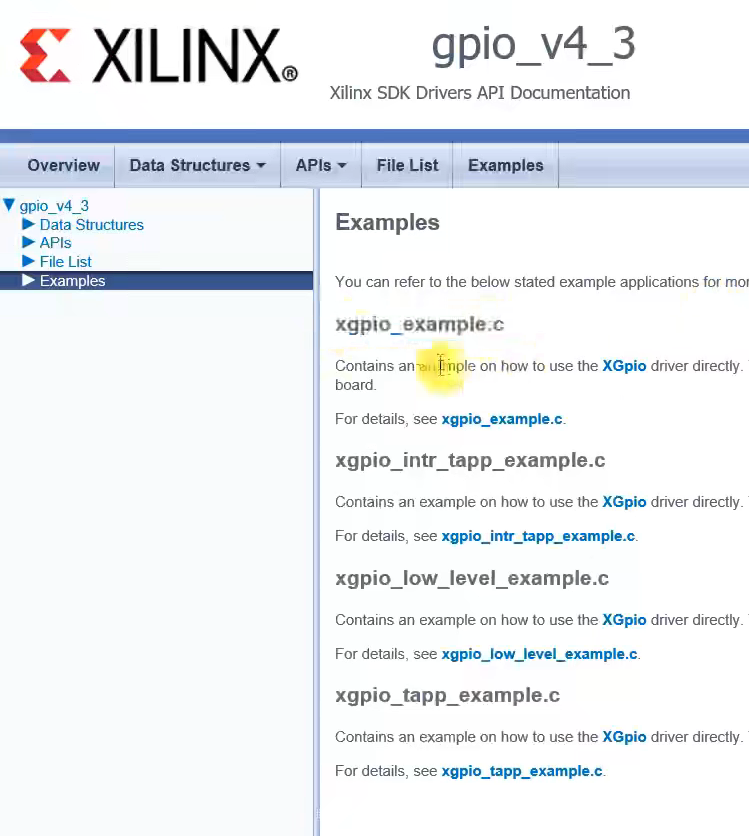

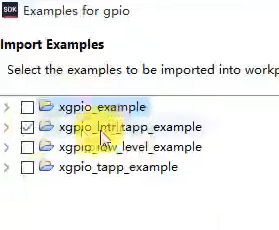

可以点开DOCUMENT在官方看一系列例子

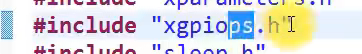

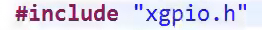

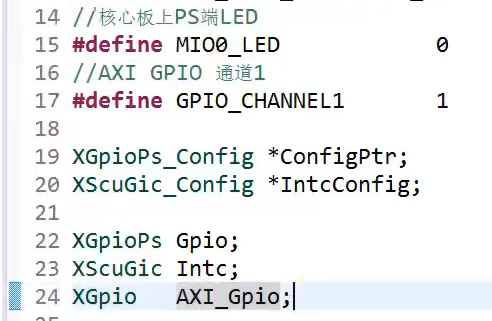

有PS说明是PS端的GPIO

这个才是AXI GPIO所需要的头文件

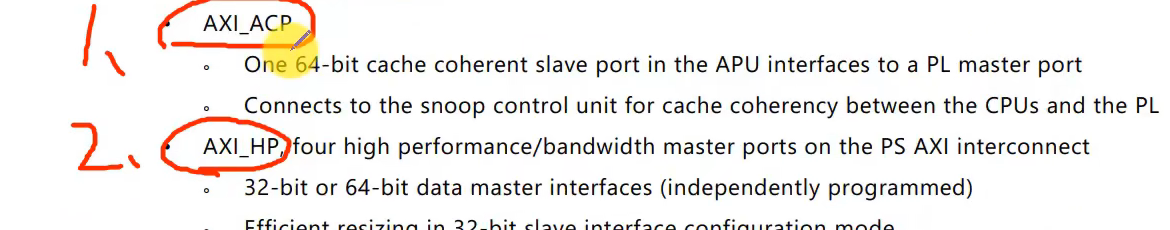

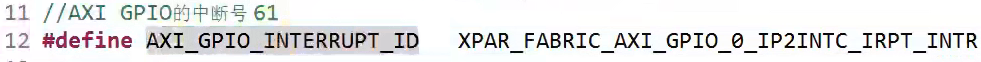

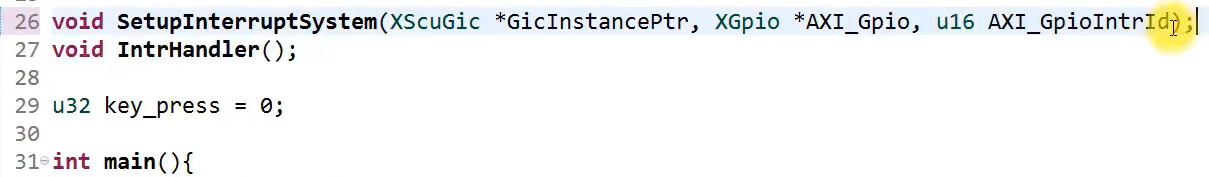

每个外设都有自己的终端号,AXI GPIO的中断是来自PL的中断,是PL到PS的中断

包含了PS到PL的中断,也包含PL到PS的中断

从PL到PS的共有16位中断,本次只用了1个,即中断号61 IRQ_F2P F:FPGA P:PS

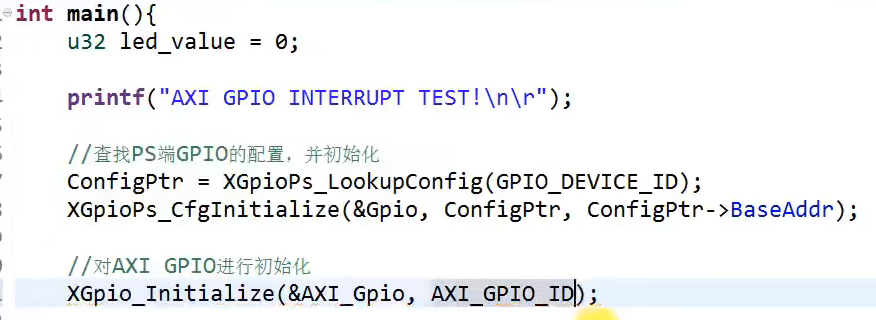

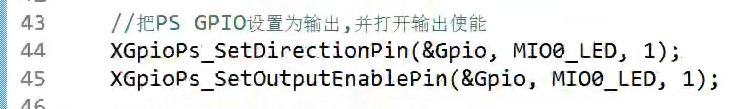

直接调用头文件里的初始化函数,指针类型所以&。也可以核PS GPIO一样分别调用

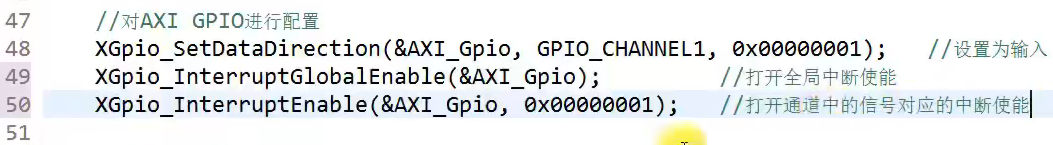

打开AXI_GPIO IP的中断之后搬到后面去了

使用最高位为输入的话是 0X8000_0000; 用的最低位 所以0X0000_0001 1表示输入

打开通道的中断使能信号,2部分:包括通道中断使能信号,全局中断使能信号

打开通道中信号对应的使能信号 MASK=0000_0001 1表示打开

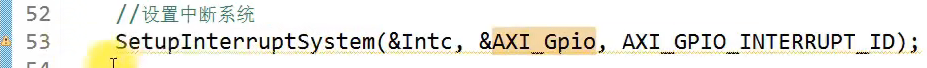

此处需要 &AXI_GPIO,为什么结合下面的想吧。

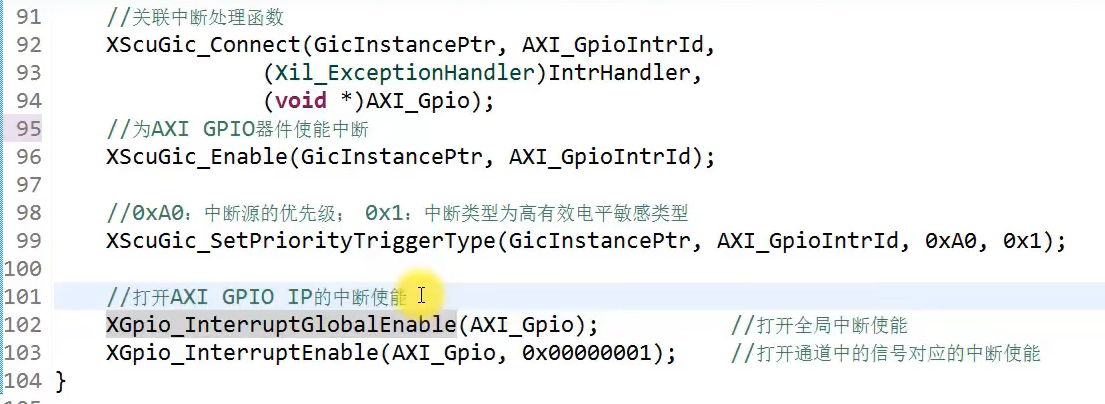

设置中断的优先级核触发类型给指定的中断源

打开AXI_GPIO IP的中断使能 在之前需要加 &,此处不用。因为此处参数是通过函数传递进来的,传递进来的时候就已经是一个指针类型的变量,相当于一个子函数的变量。二下面图中不需要&是因为这边是一个全局变量,含义不一样了

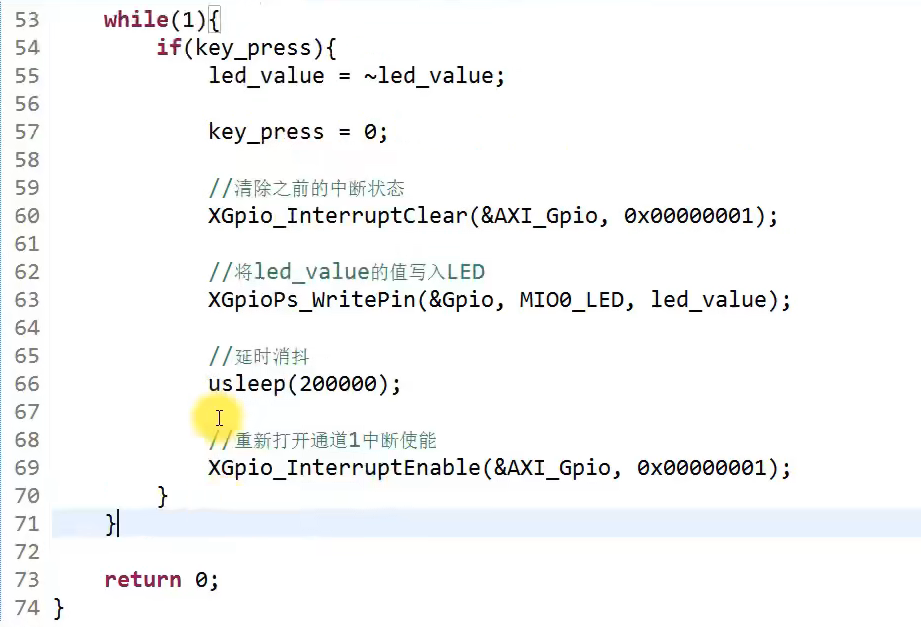

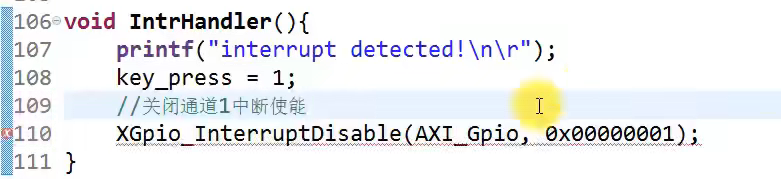

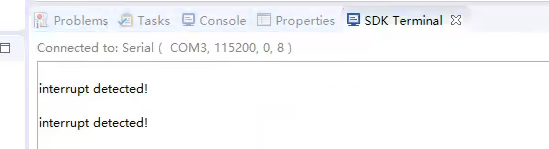

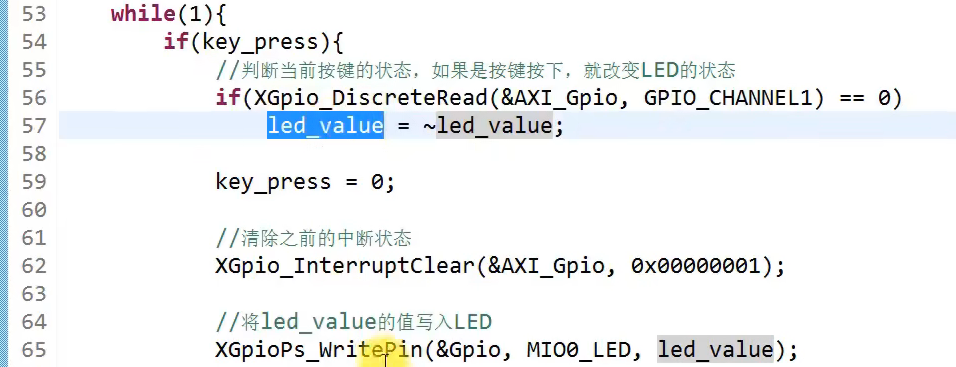

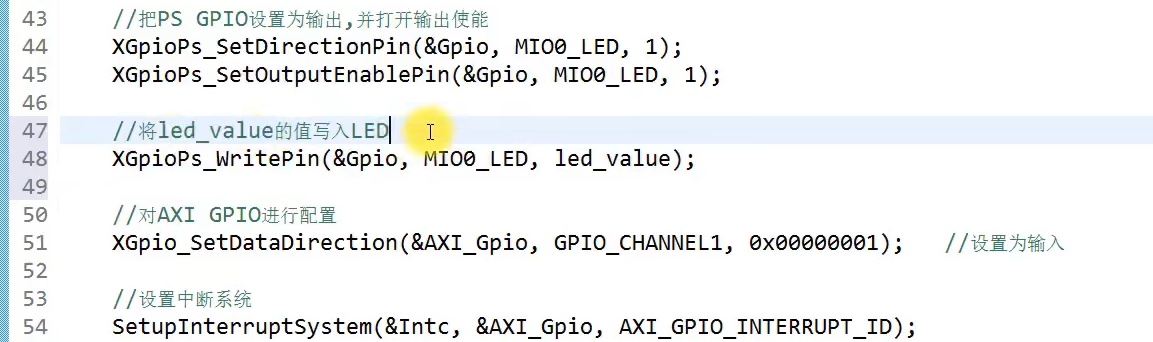

按一下打印两次中断信息,led松开就灭

因为按下的时候电平由高变低,松开由低变高,有两次变化的情况。所以检测到两次中断

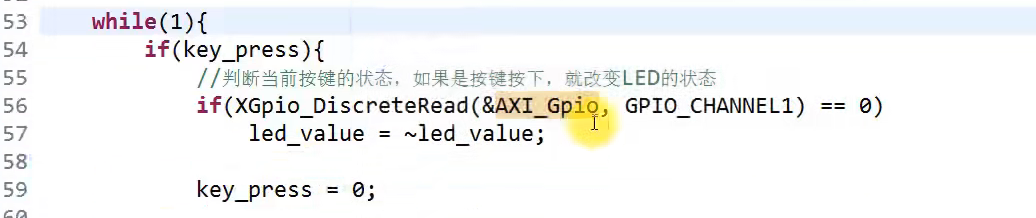

当检测到中断的时候,需要把对应的数据读出来,从而判断与AXI GPIO相连的信号的电平状态。

在代码中我们并没有去读这个数据

进行修改。按键按下,这个值为0

再进行修改

第一次LED赋值为0之后,并没有把这个0写到PS 端的 GPIO上,所以导致第一次按下按键的时候它的值没有改变。为了解决这个问题,先把LED的值先写到 PS GPIO里。

浙公网安备 33010602011771号

浙公网安备 33010602011771号