状态机

有限状态机(FSM)是时序逻辑电路设计创建的特殊模型技术。

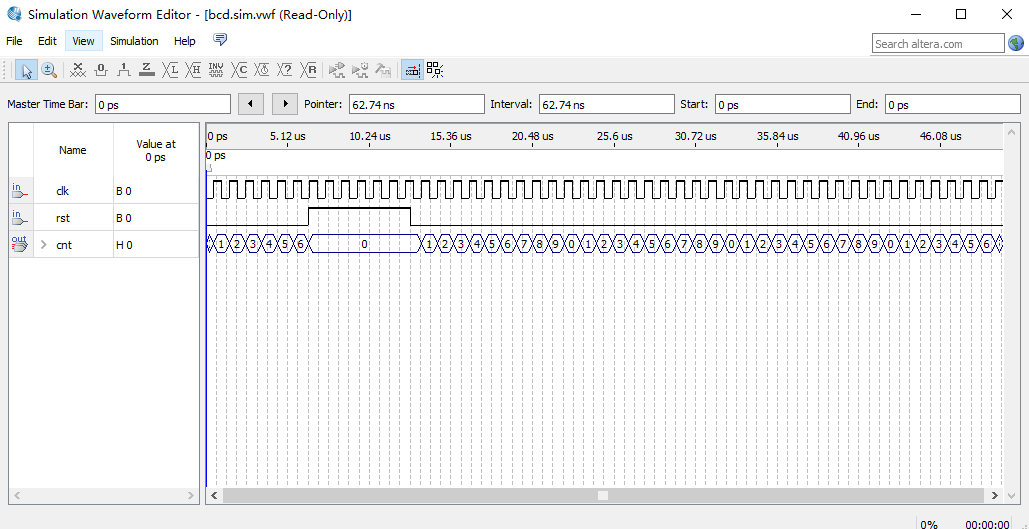

米里(摩尔)型状态机:

组合逻辑电路包含两部分:一部分是pr_stste(present state,当前状态),另一部分是实际的外部输入信号。

输出信号:nx_state(next state,下一个状态)和实际的电路输出信号。

时序逻辑电路:3个输入(clock,reset和nx_state)和一个输出(pr_state)。

米里(mealy)型状态机:输出信号不仅与电路的当前状态有关,还与当前的输入有关。

摩尔(moore)型状态机:状态机的当前输入仅仅有当前状态决定。

1、状态机的时序部分和组合逻辑部分可以分开独立设计。

时序逻辑部分包含寄存器:

process(reset,clock)

begin

if(reset='1') then

pr_state<=state0;

elisf clock'event and clock='1' then

pr_state<=nx_state;

end if;

end process;

组合逻辑部分的设计:

process(input,pr_state)

begin

case pr_state is

when state0=>

状态机模板:

library IEEE;

use ieee.std_logic_1164,all;

entity <entity_name> is

port(

input:in <date_type>;

reset,clk:in std_logic;

output:out <date_type>

);

end;

architecture <arch_name> of <entity_name> is

type state is(s0,s1,s2,s3,....);

signal pr_state,nx_state:state;

begin

process(reset,clk)

begin

if reset='1' then

pr_state<=s0;

elsif clk'event and clk='1' then

pr_state<=nx_state;

end if;

end process;

process(input,pr_state)

begin

case pr_state is

begin

case pr_state is

when s0=>

if input= then

output<=<value>;

nx_state<=s1;

else

end if;

when s1=>

.....

end case;

end process;

end;

例:

BCD计数器;

程序:

library ieee;

use ieee.std_logic_1164.all;

entity bcd is

port(

clk,rst:in std_logic;

cnt:out std_logic_vector(3 downto 0)

);

end bcd;

architecture bhv of bcd is

type state is(

zero,one,two,three,four,five,six,seven,eight,nine

);

signal pr_state,nx_state:state;

begin

process(rst,clk)

begin

if rst='1' then

pr_state<=zero;

elsif clk'event and clk='1' then

pr_state<=nx_state;

end if;

end process;

process(pr_state)

begin

case pr_state is

when zero => cnt<="0000";nx_state<=one;

when one => cnt<="0001";nx_state<=two;

when two => cnt<="0010";nx_state<=three;

when three => cnt<="0011";nx_state<=four;

when four => cnt<="0100";nx_state<=five;

when five => cnt<="0101";nx_state<=six;

when six => cnt<="0110";nx_state<=seven;

when seven => cnt<="0111";nx_state<=eight;

when eight => cnt<="1000";nx_state<=nine;

when nine => cnt<="1001";nx_state<=zero;

end case;

end process;

end bhv;

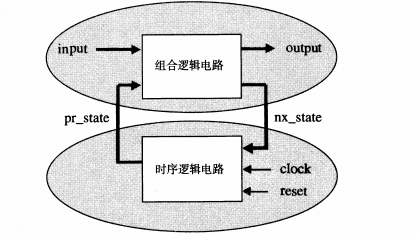

RTL原图:

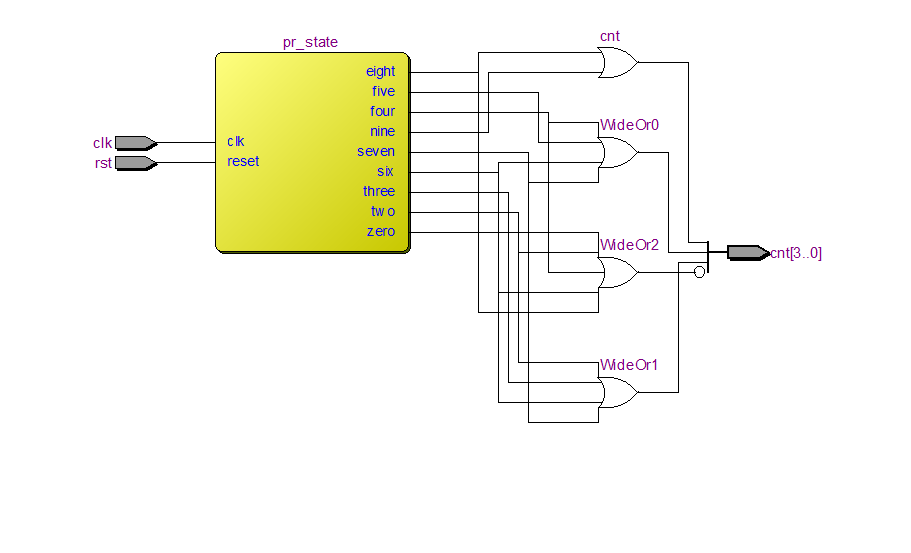

仿真图: