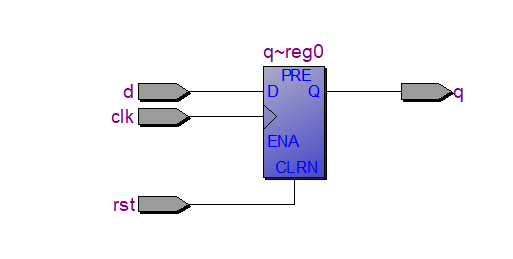

带有异步复位端的D触发器

异步复位端(rst)并采用时钟(clk)上升沿触发的D触发器(DFF)。当rst='1'时,无论时钟是什么状态,D触发器的输出

(q)都将被置为低电平。否则,只要时钟信号出现上升沿,输入的值就传递给输出(也就是说,D触发器是靠时钟的上升沿

触发的)。其原理图

程序:

library ieee;

use ieee.std_logic_1164.all;--库声明。其中std和work库是默认的,不必进行声明。

entity dff is

port(

d,clk,rst:in std_logic;--输入端口列表(输入端口的信号模式只能是in),输入信号类型std_logic。

q:out std_logic

);

end;

architecture bhv of dff is

begin

process(rst,clk)--每当敏感信号列表中的信号发生变化时,process就执行一次。

begin

if(rst='1') then

q<='0';--无论clk是什么状态,只要rst=‘1’,输出都将复位(异步复位)

elsif (clk'event and clk='1') then--如果rst是低电平;且clk出现上升沿(clk='1'),则输入信号将存储在D触发器中(q<=d)。

q<=d;

end if;

end process;

end bhv;

"<="操作符用来给信号(signal)赋值

":="用来给变量(variable)赋值。

默认情况下,entity中所有的端口都是信号。