ModelSim的TCL脚本仿真流程【超详细案例教学】

前言

在编写完成verilog代码时,我们常用需要使用modelsim软件进行仿真,一般我们都是在modelsim中手动添加文件,波形等等,小工程倒是无所谓,但是一旦信号量较多,涉及到观察以及编译方式使用GUI界面操作的方式未免有些麻烦,所以在此介绍利用tcl脚本去是实现modelsim的自动化仿真。

Tcl全称是Tool Command Language,其在fpga设计、ic设计和验证中作为一种比较常用的脚本语言(其他的还有:perl,shell,python)

环境准备:

1.已安装好modelsim软件

2.有notepad++或sublime等文本编辑器,用以编写tcl脚本

常用的tcl脚本仿真

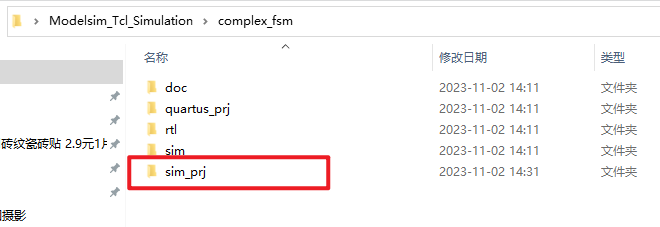

- 下载实验工程——Modelsim_Tcl_Simulation

- 一般我们的工程文件下有下列子文件夹,其中

sim_prj为存放tcl脚本等仿真文件的文件夹

- 打开sim_prj文件可以看到其中名为:

sim.tcl的文件,即为comflex_fsm工程的仿真脚本文件

其中内容如下,其实现了对于本工程的仿真说明:

############################## 基础配置#############################

#退出当前仿真

quit -sim

#清除命令和信息

.main clear

##############################编译和仿真文件#############################

#编译修改后的文件,这里把设计文件和仿真文件分开放了,所以写两个

vlog "../rtl/*.v"

vlog "../sim/*.v"

#vsim用于仿真

#-voptargs=+acc:加快仿真速度 work.xxxxxxxx:仿真的顶层设计模块的名称 -t ns:仿真时间分辨率

vsim -t ns -voptargs=+acc work.tb_complex_fsm

############################## 添加波形模板#############################

# 添加虚拟类型

virtual type {

{01 IDLE}

{02 HALF}

{04 ONE}

{08 ONE_HALF}

{16 TWO}

} vir_new_signal

#添加波形区分说明

add wave -divider {tb_complex_fsm}

#添加波形

add wave tb_complex_fsm/*

add wave -divider {complex_fsm_inst}

add wave -radix decimal tb_complex_fsm/complex_fsm_inst/*

virtual function {(vir_new_signal)tb_complex_fsm/complex_fsm_inst/state} new_state

add wave -color red -itemcolor blue tb_complex_fsm/complex_fsm_inst/new_state

###常用添加波形指令

#-radix red -----设置波形颜色

#-itemcolor Violet -----设置波形名字颜色

#常用颜色:red,blue,yellow,pink,orange,cyan,violet

#-radix decimal----定义显示进制形式

#常用进制有 binary, ascii, decimal, octal, hex, symbolic, time, and default

## 配置时间线单位(不配置时默认为ns)

configure wave -timelineunits us

############################## 运行#############################

run 10us

| 上述sim.tcl脚本补充解释 |

quit -sim退出仿真,即如果当前modelsim中具有仿真运行,可以将其中止并退出仿真界面

.main clear清除modelsim Transcript中的内容

vlog "../rtl/*.v",vlog为编译的意思,则../rtl/*.v代表路径,因为仿真工程在sim_prj中,所以需要利用../退到上一级文件夹,再选择/rtl/*.v,即rtl文件夹下的所有.v文件,当然如果不需要全部编译,也可以指定文件,eg:vlog "../rtl/complex_fsm.v"

# 添加虚拟类型

virtual type {

{01 IDLE}

{02 HALF}

{04 ONE}

{08 ONE_HALF}

{16 TWO}

} vir_new_signal

virtual function {(vir_new_signal)tb_complex_fsm/complex_fsm_inst/state} new_state

add wave -color red -itemcolor blue tb_complex_fsm/complex_fsm_inst/new_state

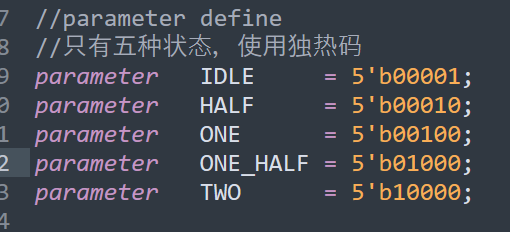

这块代码,比如在状态机中直接使用0001,0010....这种数字不太好直观体现变化以及观察,这里可以运用virtual type定义虚拟类型,这样让数值和字符一一对应,根据complex_fsm.v代码可以配置对应关系:

一般来说根据自己实际的状态机名字配置就可以了。

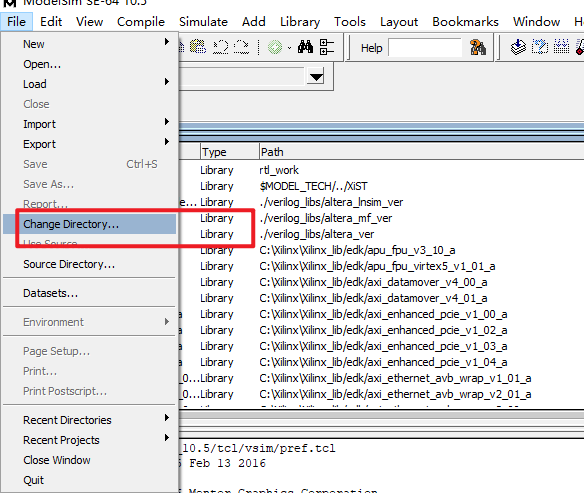

- 打开modelsim软件,切换路径至你下载仿真工程的sim_prj下(

xxxx\Modelsim_Tcl_Simulation\complex_fsm\sim_prj)

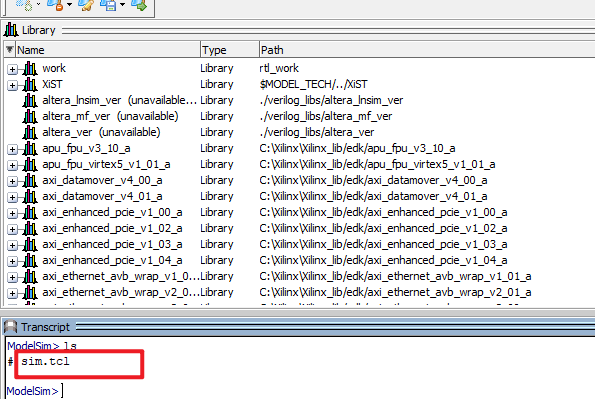

- 在命令窗口输入

ls可以看到sim_prj文件下的tcl脚本

- 输入指令

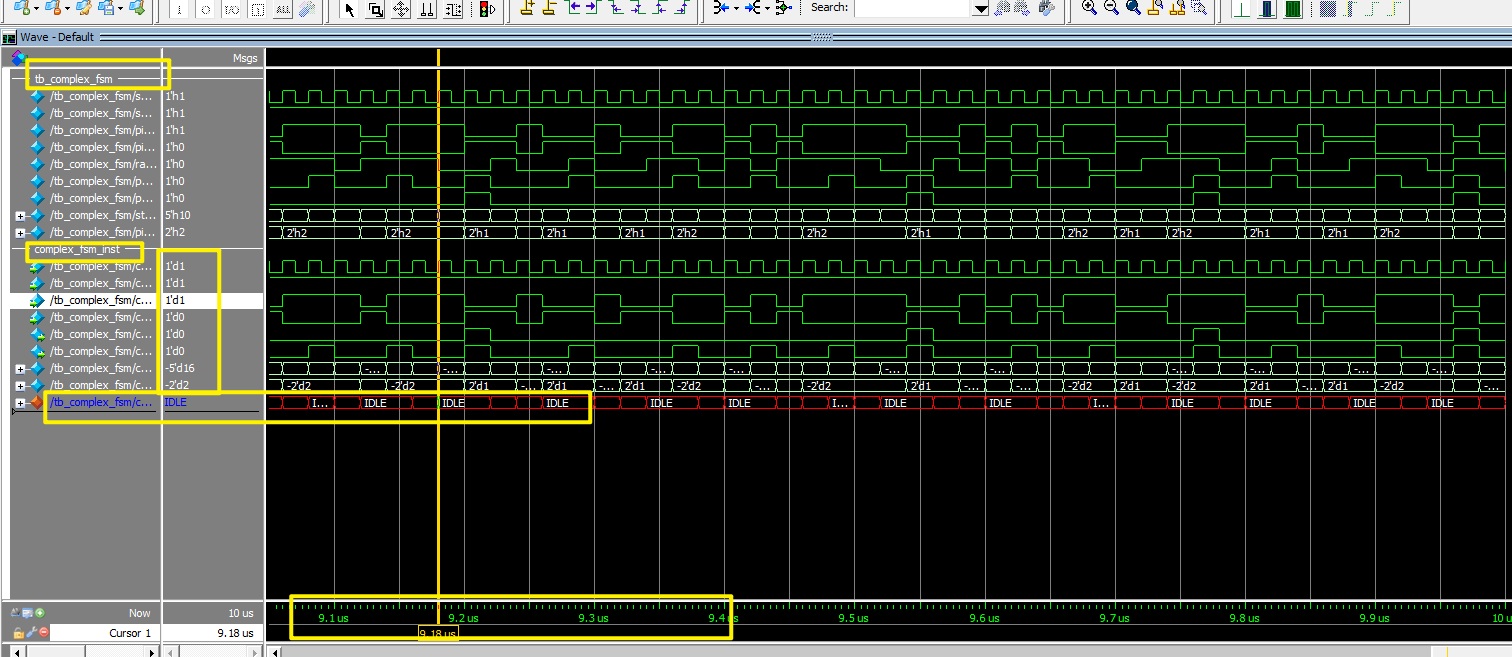

do sim.tcl,则执行编写的脚本内容,进行仿真,打开wave波形如下:

可以看到无论是波形分区说明,虚拟类型状态机(包括波形颜色,名称颜色),时间线单位,波形数据类型都和配置相符,说明了利用tcl脚本仿真的成功。

后面对于不同的仿真需要根据上述脚本模块进行修改即可

复杂tcl脚本仿真(以Quartus中带ipcore为例)

上面的仿真仅仅涉及自己编写的.v文件,但是在实际中我们可能需要添加ip核,并进行仿真,这就需要添加不同软件ip核仿真所支持的文件。

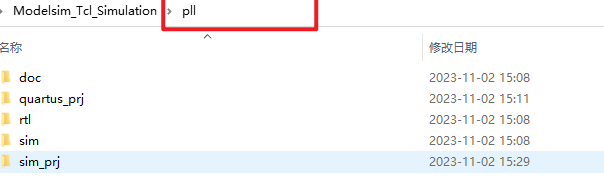

以quartus软件中生成pll锁相环为例。其重要在下载的仿真工程中:

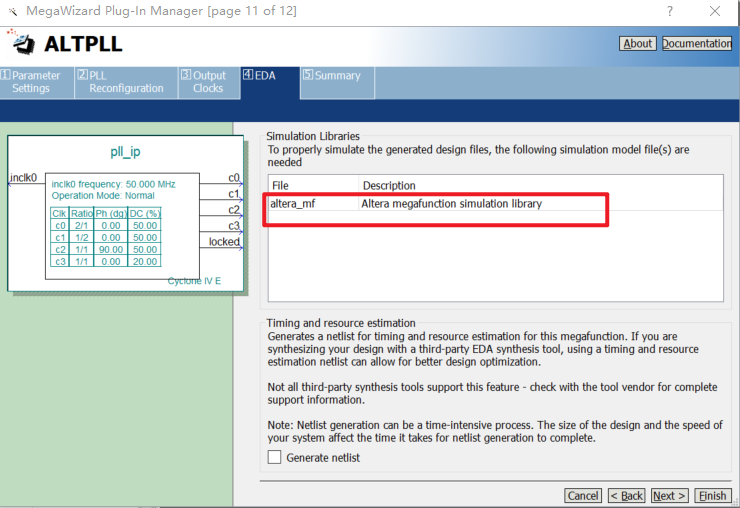

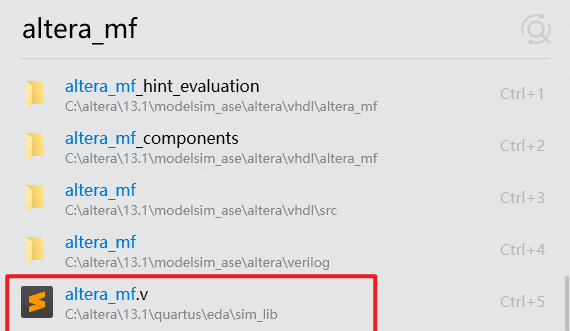

在配置pll锁相环中,quartus提醒借用第三方软件进行仿真需要添加Altera的仿真库文件altera_mf,所以在编译文件中需要将该文件添加至脚本编译

pll/sim_prj/sim.tcl脚本内容如下:

############################## 基础配置#############################

#退出当前仿真

quit -sim

#清除命令和信息

.main clear

##############################编译和仿真文件#############################

#创建库

vlib ./lib

vlib ./lib/base_lib

vlib ./lib/altera_lib

#映射逻辑库到物理目录

vmap base_lib ./lib/base_lib

vmap altera_lib ./lib/altera_lib

#编译修改后的文件,这里把设计文件和仿真文件分开放了,所以写两个

vlog -work base_lib "../rtl/*.v"

vlog -work base_lib "../sim/*.v"

vlog -work base_lib "../quartus_prj/ip_core/pll_ip.v"

vlog -work altera_lib "C:/altera/13.1/quartus/eda/sim_lib/altera_mf.v"

#vsim用于仿真

#-voptargs=+acc:加快仿真速度 work.xxxxxxxx:仿真的顶层设计模块的名称 -t ns:仿真时间分辨率

#由于创建了多个逻辑映射库,而启动仿真的时候的是需要链接库

#因此 -L 逻辑映射库1 -L 逻辑映射库2... 就把映射库链接起来

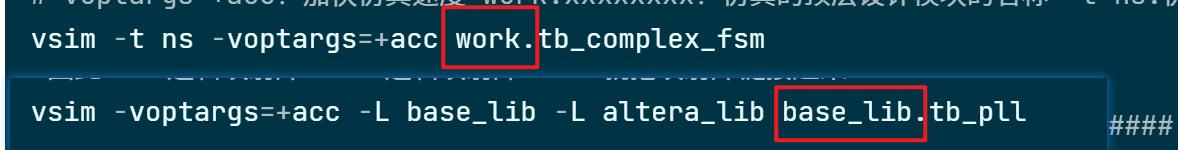

vsim -voptargs=+acc -L base_lib -L altera_lib base_lib.tb_pll

############################## 添加波形模板#############################

#添加波形区分说明

add wave -divider {tb_pll}

#添加波形

add wave tb_pll/*

add wave -divider {pll_inst}

add wave tb_pll/pll_inst/*

############################## 运行#############################

run 10us

| 上述sim.tcl脚本补充解释 |

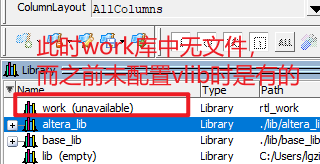

和常用的tcl脚本仿真中的sim.tcl相比,这里创立了lib,base_lib,altera_lib并进行物理路径进行映射。

vlog -work base_lib "../rtl/*.v"将rtl路径下的.v文件编译的结果和源文件放入base_lib,这样不同的编译结果仿真不同的地方方便进行管理。

此时由于顶层仿真文件在base_lib库中,所以tb_pll的库名字需要更改为:base_lib.tb_pll。之前常用的tcl脚本仿真中的sim.tcl未有vlib创建和vmap映射则默认对应work库,并且物理路径为./rtl_work,且之前的所有源文件和编译文件都在work库中,所以直接写work.tb_complex_fsm

此外,由于现在编译库不为默认的work库,所以需要利用-L lib_name去链接使用的库:vsim -voptargs=+acc -L base_lib -L altera_lib base_lib.tb_pll

|

|---|

|

最后注意的是:不同电脑的altera_mf.v路径不同,需要进行更改,我的文件路径如下:

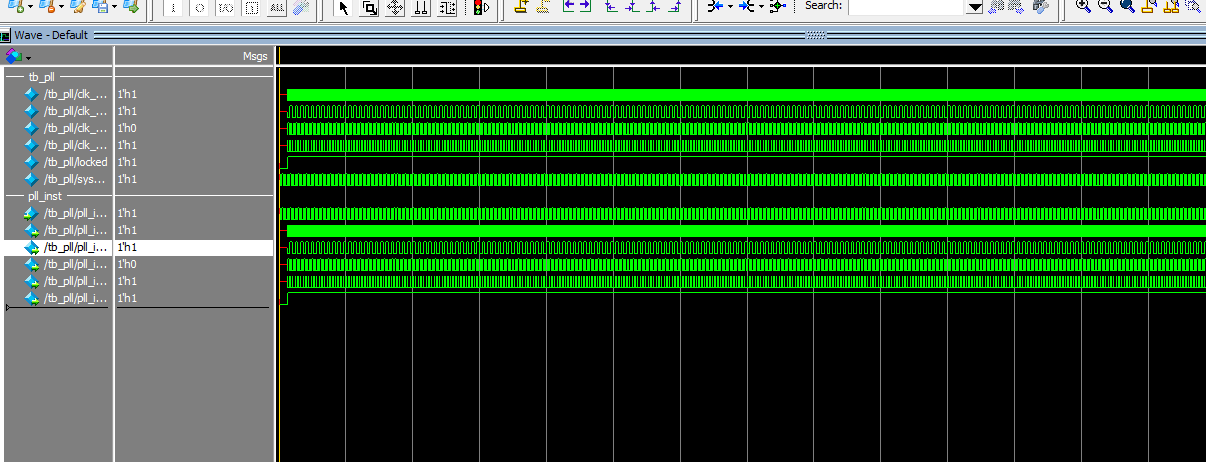

接着直接按照上一节的操作方法,进行仿真即可,结果如下。证明仿真是没问题的。

浙公网安备 33010602011771号

浙公网安备 33010602011771号