一、什么是竞争冒险,如何消除?

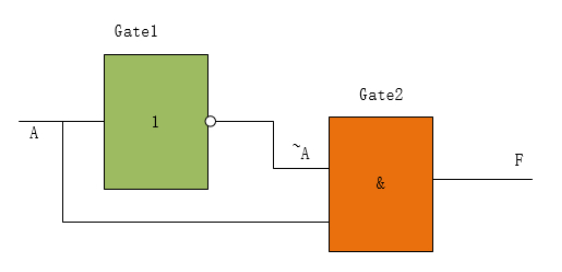

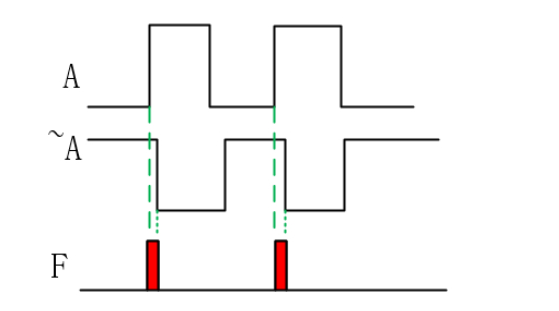

下面这个电路,使用了两个逻辑门,一个非门和一个与门,本来在理想情况下F的输出应该是一直稳定的0输出,但是

实际上每个门电路从输入到输出是一定会有时间延迟的,这个时间通常叫做电路的开关延迟。而且制作工艺、门的种

类甚至制造时微小的工艺偏差,都会引起这个开关延迟时间的变化。

实际上所谓的竞争冒险就是:就是逻辑门的延迟所导致的输入输出不同步的现象。算上逻辑门的延迟,信号经过不同路径到达某一个汇合点的时候在到达时间上会出现时间先后的现象,称之为竞争;由于竞争现象所引起的电路输出发生瞬间错误的现象,称之为冒险。在通常的FPGA设计中最简单的避免方法是使用时序逻辑同步输入输出。还有例如以下的方法:加滤波消除毛刺的影响;加选通信号,避开毛刺;增加冗余项,消除逻辑冒险。

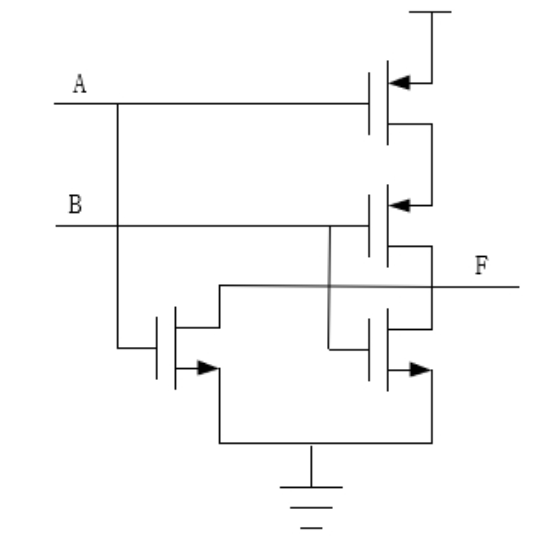

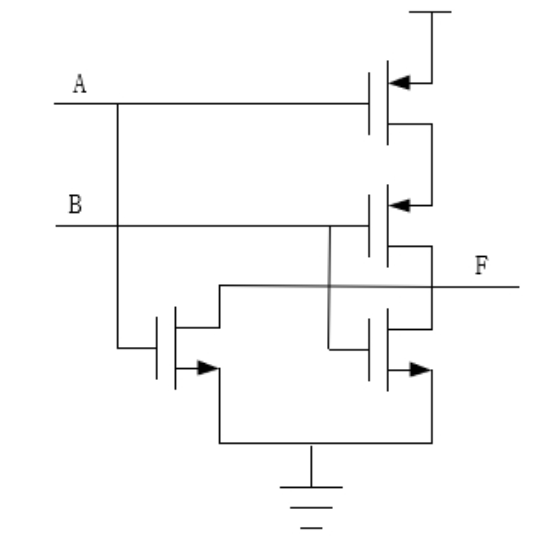

一、MOS逻辑门?

与非门:上并下串(上为PMOS,下为NMOS)

或非门:上串下并

反相器

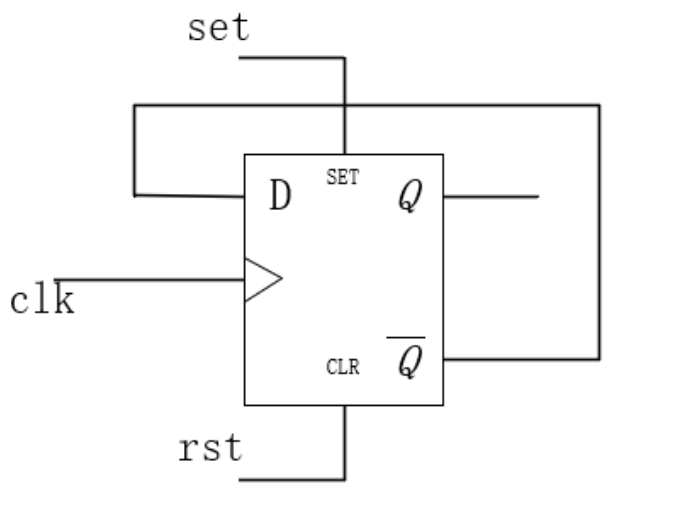

三、用D触发器带同步高置数和异步高复位端的二分频的电路,画出逻辑电路Verilog描述

1 reg Q; 2 always @(posedge clk or posedge rst)begin 3 if(rst == 1'b1) 4 Q <= 1'b0; 5 else if(set == 1'b1) 6 Q <= 1'b1; 7 else 8 Q <= ~Q; 9 end