在fpga 的大型项目中经常会用到时序分析,很多面试的场合也会遇到时序分析。经常用到的时序分析主要包括时钟时序分析,输入端的时序分析以及暑促短的时序分析。最基本的时序分析师归结到寄存器于寄存器之间的时序分析。主要是分析setup_slack建立时间裕量和hold_slack保持时间裕量。

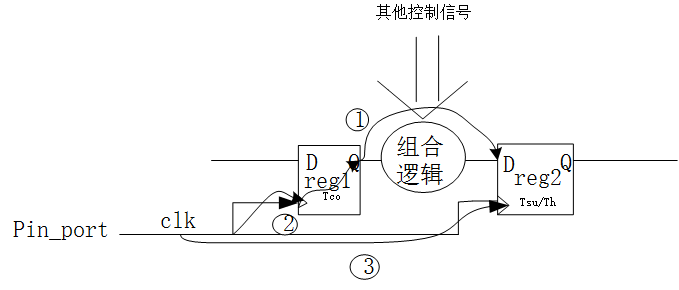

一、寄存器与寄存器之间的时序模型

1、第(1)条路径包括数据路径简称Tdata以及reg1内部的延迟Tco。数据沿着clk时钟到达寄存器的Q端,最后由Q端输出。在reg1内部数据随着时钟到达到达reg1的Q端的内部延迟为Tco,寄存器是边沿触发的。中间的数据传输与、或,非、异或等组合逻辑都有延迟特性会产生数据的延迟简称Tdata。

2、第(2)条路径是源时钟到达寄存器的时钟延迟简称Tclk1。

3,第(3)条路径是源端时钟到达reg2的时钟延迟简称Tclk2.

二、计算setup_slack和hold_slack。

根据以上的时序模型,可以数据传输的时序图如下所示:

clock_pad:是源短时钟。

clock_in_reg1:是到达寄存器reg1的时钟,Tclk1是时钟到达reg1的延迟。

reg1_q:是数据到达寄存器reg1的Q短的时刻。Tco寄存器内部的延迟。

reg2_d:是数据到达寄存器reg2的D端的时刻。Tdata数据延迟。

通过以上模型分型:数据到达的时间=Tclk1 + Tco + Tdata.

clock_pad:是源短时钟。

clock_in_reg1:是到达寄存器reg1的时钟,Tclk1是时钟到达reg1的延迟。

clock_in_reg2:是到达寄存器reg2的时钟,Tclk2是时钟到达reg2的延迟。

Tsu:数据据所需要的最小的建立时间。

寄存器reg2是用来采集数据的,而且是边沿采集,也就是说当数据到达第二个寄存器reg2的d端口,并且时钟到达寄存器reg2的上升沿,才能准确的采集到数据。其中在满足这个条件的同时根据我们芯片器件的属性还会有一个采集门限建立时间Tsu.就是在采集上升沿到来之前数据必须保持稳定的最小时间。所以数据要求到达的时间就应该是在第二个寄存器reg2的始终上升沿到来之前的一小段时间到达,这一小段时间就是就是需要的建立时间Tsu.因此可以得到数据到达的时间=一个时钟周期 + Tclk2 -Tsu.

那么数据的实际到达时间和数据要求到达的时间之间的差值就是建立时间裕量setup_slack.得到的计算公式为:

setup_slack=一个时钟周期 + Tclk2 -Tsu-(Tclk1 + Tco + Tdata)

在这里要引入时钟偏移的一个概念,假设时钟便宜用ΔT来表示,那么:ΔT = Tclk2 - Tclk1.那么setup_slack的表达公式就变为i:

setup_slack=一个时钟周期 +ΔT-Tsu-( Tco + Tdata)

数据的保持时间就没有那么复杂了:Thold = Tdata - ΔT .

三、相关分析

1、当得到setup_slack大于Tsu时,建立时间不违例。当得到setup_slack小于Tsu时,

2、会出现建立时间违例。当时钟便宜ΔT>0时,Thold收到影响。当时钟便宜ΔT<0时,setup_slack会受到影响.

3、而且始终越慢就会影响建立时间,时钟越快就会影响保持时间。

4、Fmax=1/(一个时钟周期-setup_slack)