上一节。我们已经把USB2.0的同步读写都调试通过,包括使用CHIPSCOP抓取波形,但是USB2.0的功能绝不是仅仅这些,但是基于本次项目我们只需要这些。那么下来就是我们要讲解一下几乎每一个大项目都要用到的DDR。

具体关于DDR的一些基础知识,大家自行补习。话不多说。开始吧。

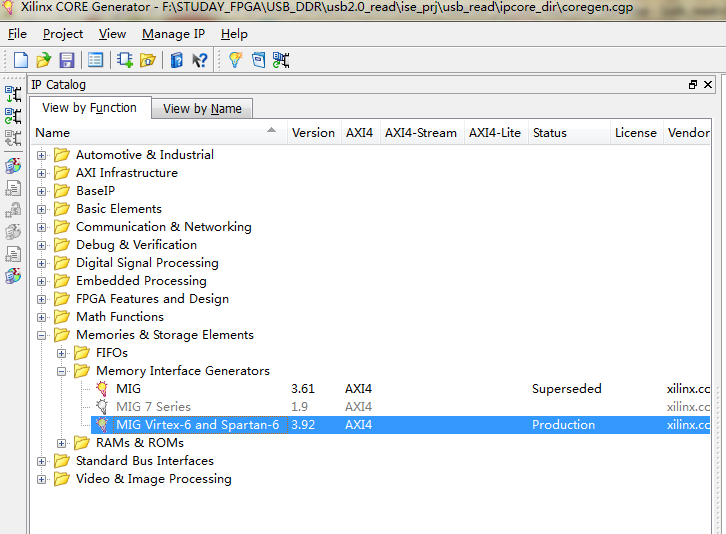

第一步:创建DDRIP。如下图所示,DDR 是在MIG中

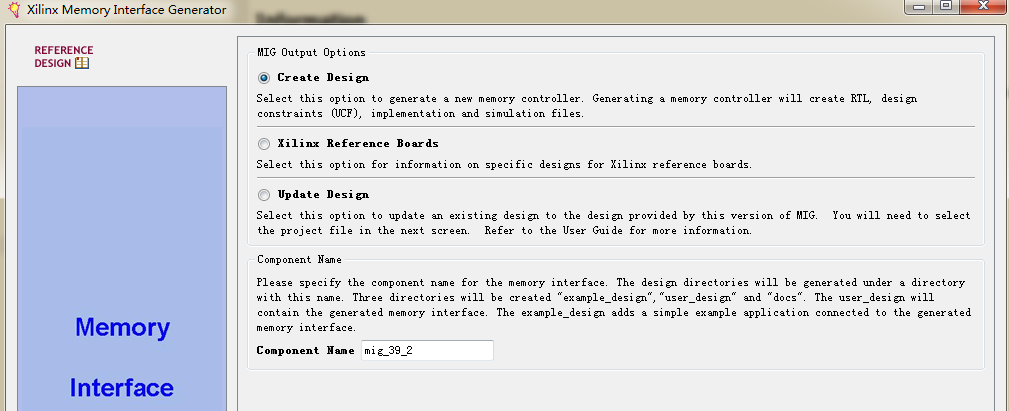

第二步:在这步中,有四个选项,分别是创建一个DDR、使用XILINX自带的DDR,更新已存在的DDR、DDR的名字。这里我们选择第一个创建DDR,名字不做改变(这个根据自己意愿),点击下一步

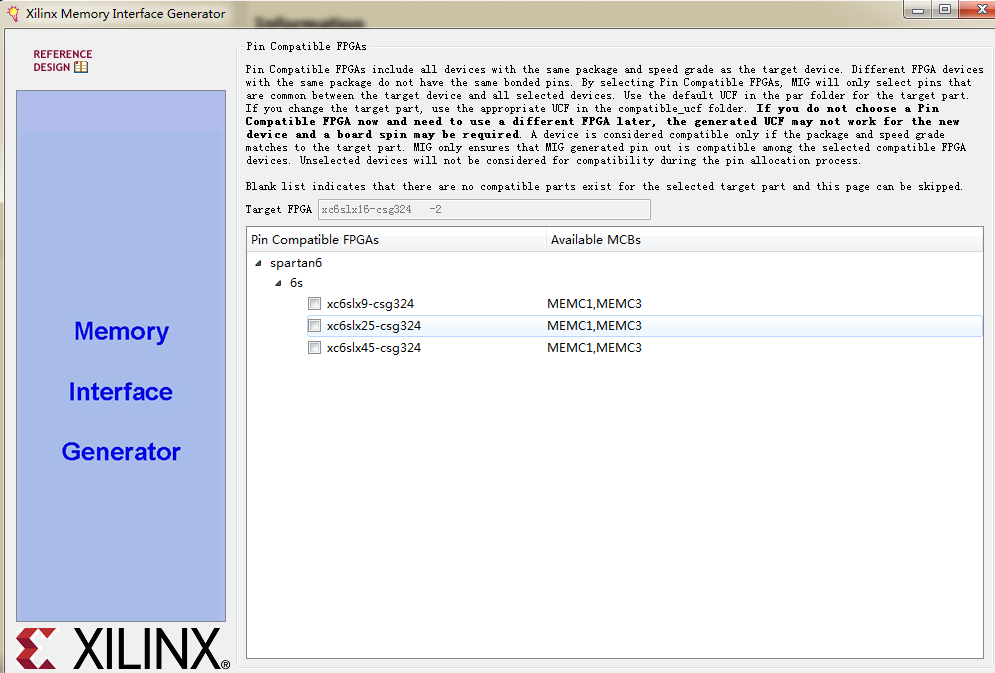

第三步:下图显示的意思是,我们选择的目标FOGA的型号,同时XILINX也给出了当前与我们选择的型号兼容的一些型号,这里保持默认状态,不做选择。直接点击下一步。

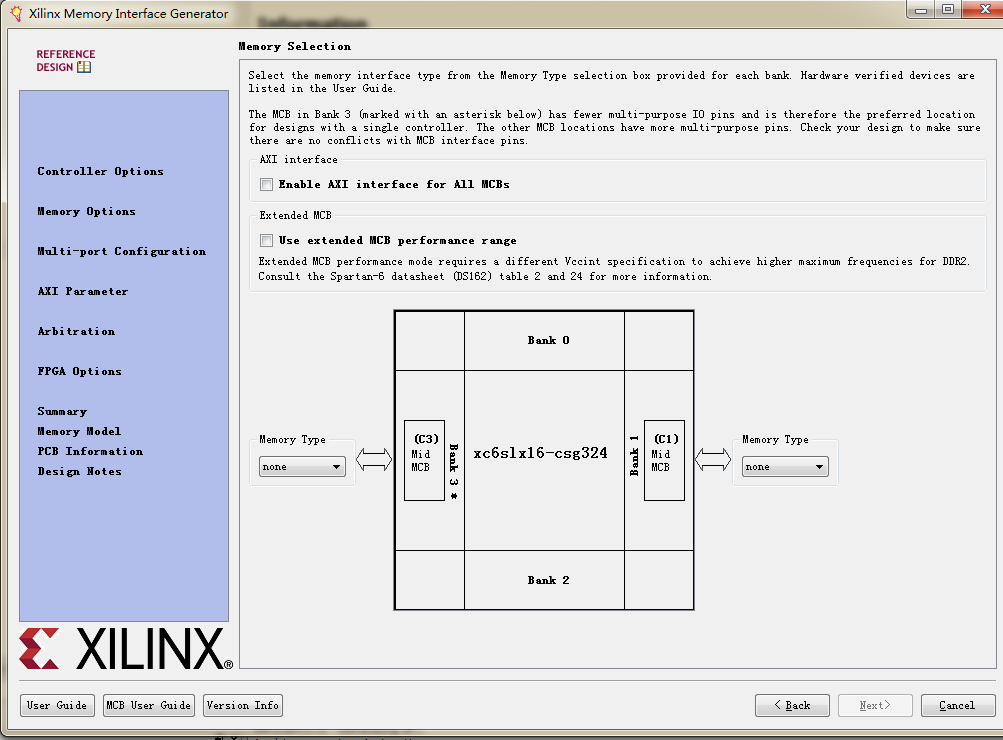

第四步:如下图所示分别是AXI接口的DDR、标准类型的DDR。下面的框图中BANK1和BANK3是可以外接DDR,这个具体选择要看你选择的开发板,看一下开发板DDR是连接在那一端的。因为我使用的开发板是连接在BANK1的。所以在BANK1 选择DDR3 SDRAM。然后点击下一步。

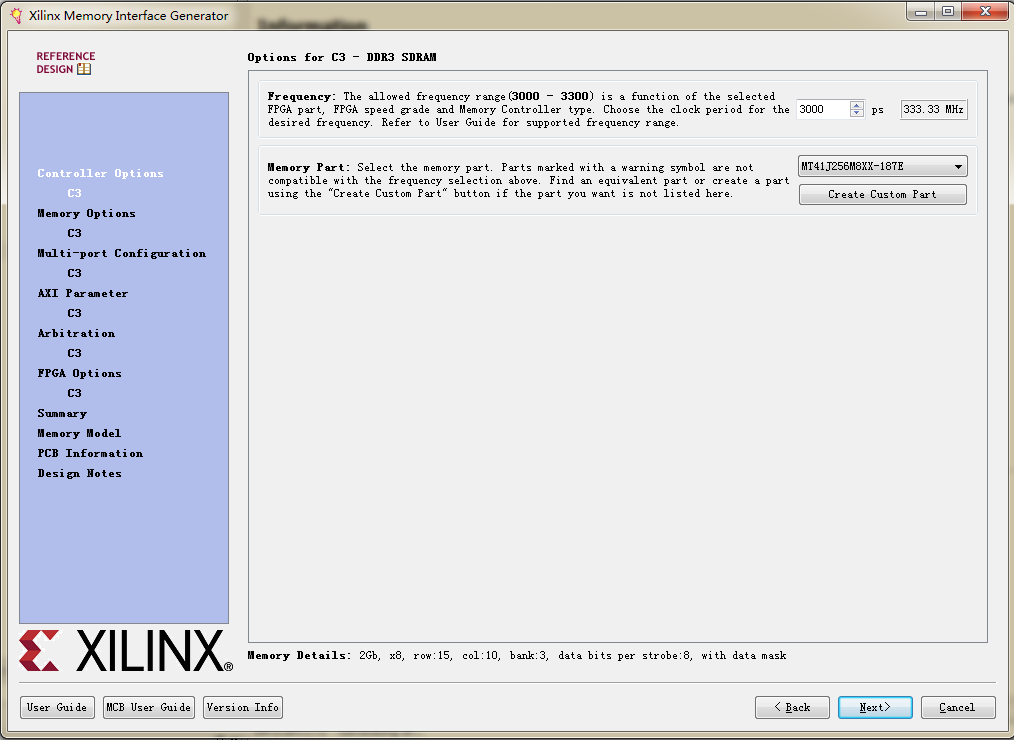

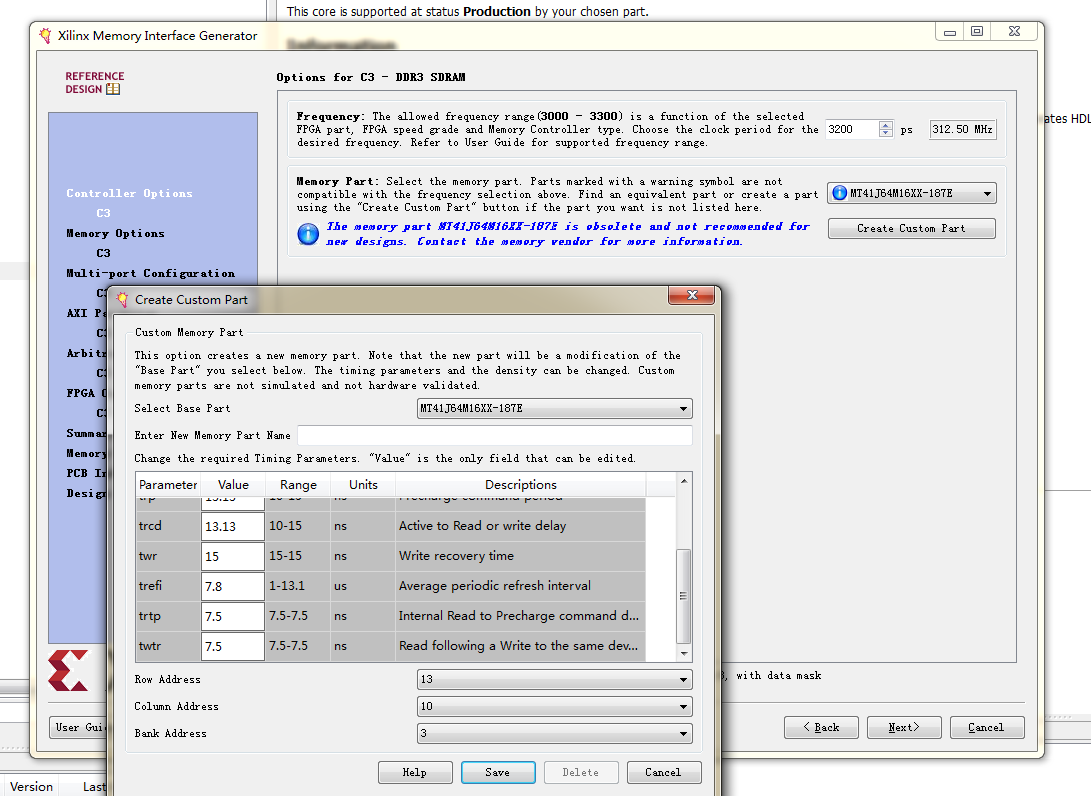

第五步:频率选择这里的选择可以是3000-3300Ps这个时钟有两层含义,第一:表示DDR芯片的工作频率,第二:表示IP CORE的参考时钟;Memery part :表示你用的开发班上DDR3的芯片对应的型号;Creat Custom Part : 表示如果没有你板子上对应的DDR型号,你可以自己创建,但是需要的参数比较多。我们在这里选择3200PS,型号与我开发板上的DDR相对应。点击下一步

第六步:这一步不足要做任何设置,则里的这几个设置主要是关于开发板的阻抗设置,我们直接点击下一步。

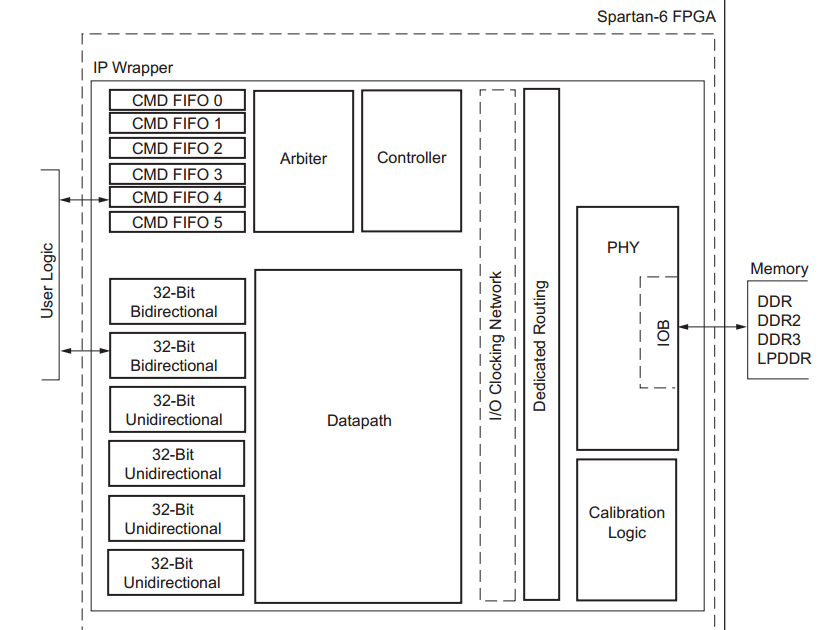

第七步:这是我们要选择的DDR的输入输出,不同模式的端口。根据数据手册如下图所示两个单向的32BIT读写接口和4个单向的续写端口,我们在此选择64BIT的双向读写端口。同时地址的映射顺序选择第二行的BANK、ROW、COLUMN,然后点击下一步。

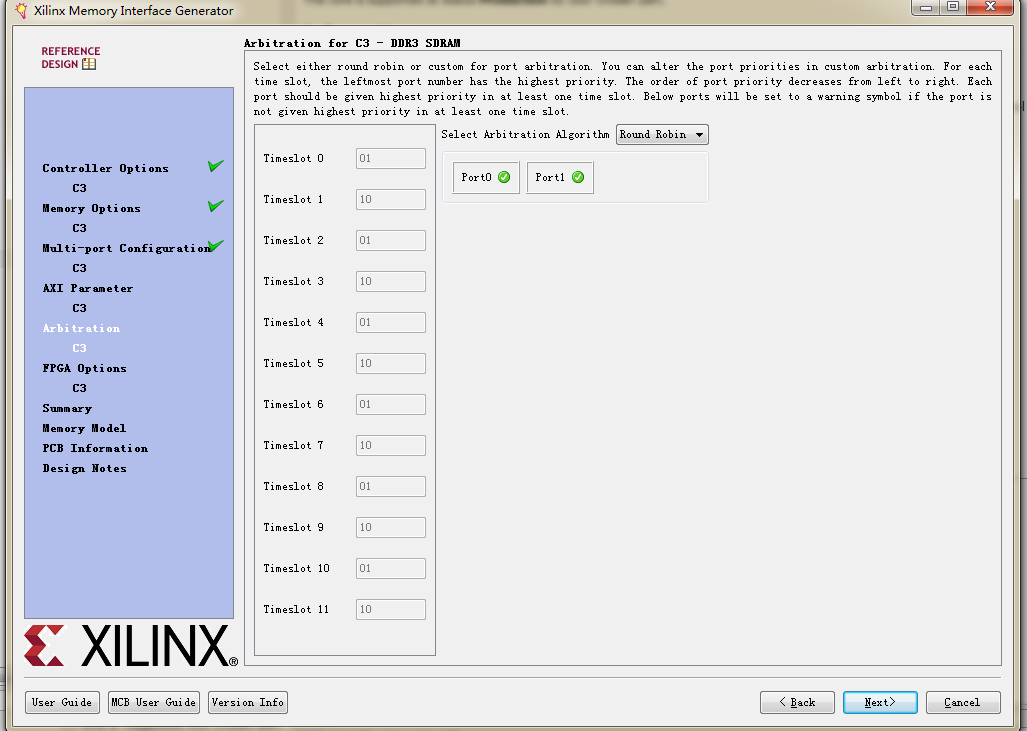

第八步:这里选择罗宾循环来轮训这些端口。点击下一步。

第九步;这里主要是输入阻抗匹配的配置,选择第一个用外接电阻来匹配,RZQ的管脚选择L6,ZIO的管脚选择C2(这两个管脚的选择要根据自己的开发板来择,就是连接DDR的管脚中有接下拉电阻的两个管脚,分别是FPGA ONE CHIP TERM1和FPGA ONE CHIP TERM2),然后就是DEBUG信号的加入,我们这里不加入,不使能、系统的时钟类型要根据自己的开发班子来,我这里是单端时钟。点击下一步

剩下的一路NEXT就好,这样就生成了我们经常所说的IP CORE。

就hi诶西安来就是搭建提供的例子的仿真魔性了,

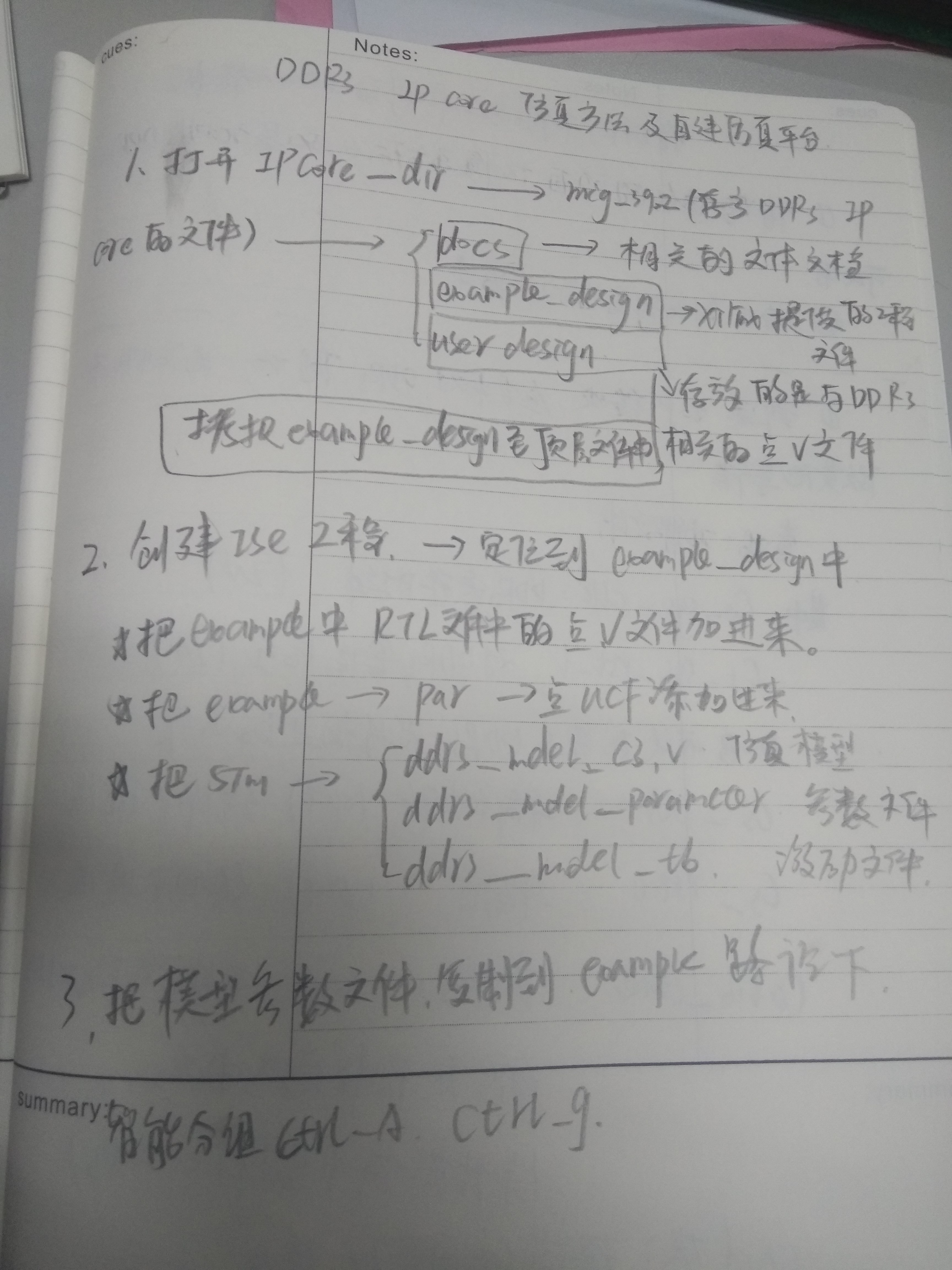

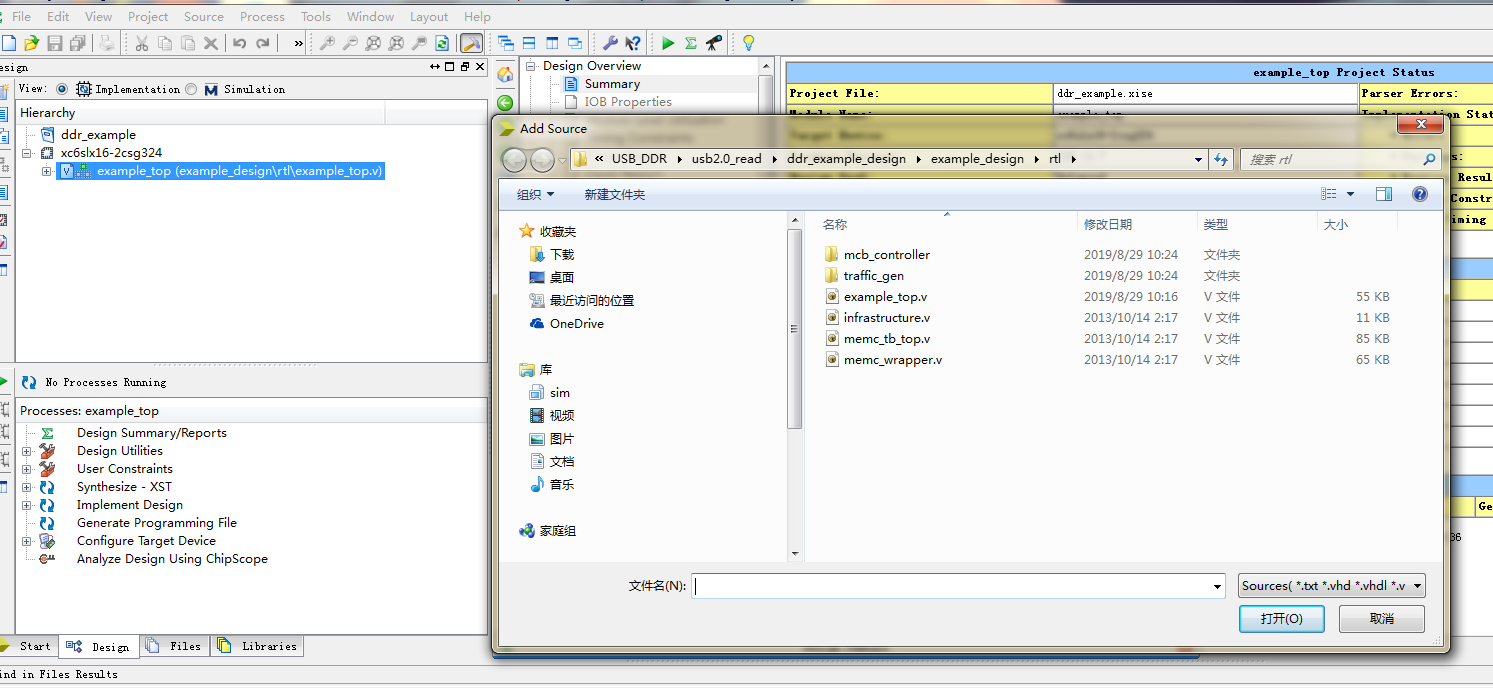

第十步:按照以下步骤搭建工程

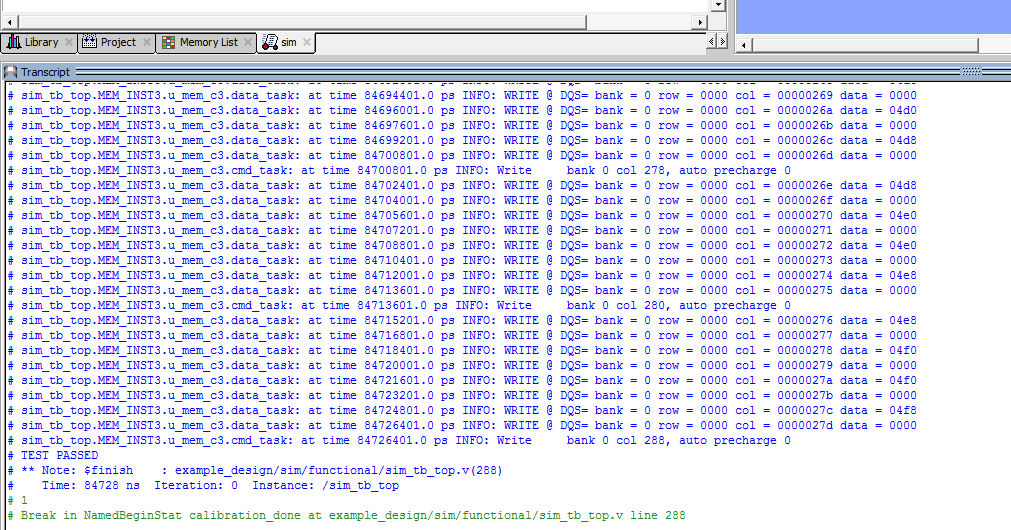

第十一步:当出现TEST PASSED说明搭建成功。

OK完工!

浙公网安备 33010602011771号

浙公网安备 33010602011771号