USB2.0的开发与设置主要包括三部分,第一:基于keil 的USB2.0的固件开发,这里主要是借用黑金开发板516上面自带的固件进行相关的设置预配置:第二:是基于C# 或者C++对于USB2.0的上位机的开发;第三:主要是基于FPGA的对于USB2.0的同步传输。

首先,通过固件修改将USB2.0配置为同步传输模式,这里用到的是EZ-USB,板载芯片是Cypress68013A。黑金开发板默认的是异步传输。

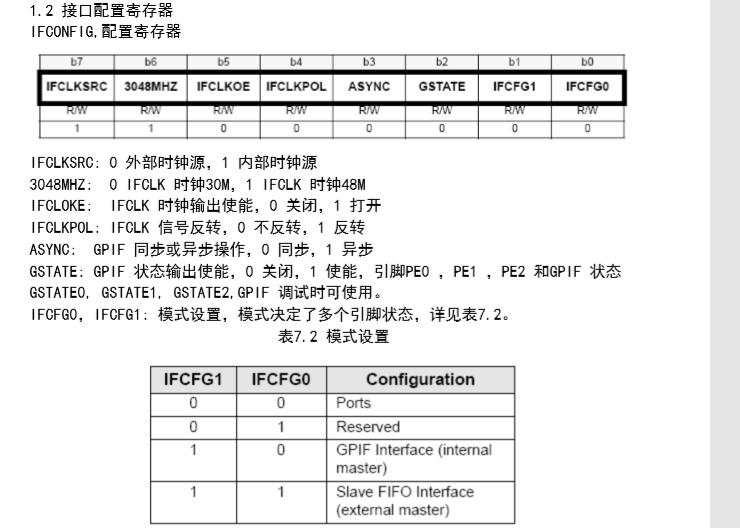

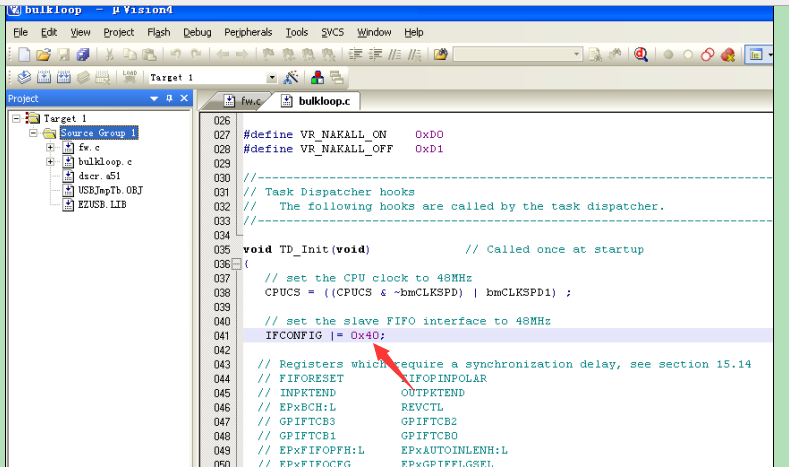

将固件中的IFCONFIG 寄存器配置成为0xE3,即配置成了同步模式,即图示位置

将改好后的固件编译后,同过黑金提供的上位机,将生成的HEX文件或者IIC文件下载到USB2.0中,重新上电即可,如下图所示DONWLOAD是用来下载HEX文件,掉电丢失;LG EEPROM是用来下载IIC文件时机哦保存在RRPROm中的。

固件配置好后就是 FPGA Verilog 程序设计了;在本次测试中实现的是FPGA想USB中写数据,在PC端通过上位机显示出来。代码很少;

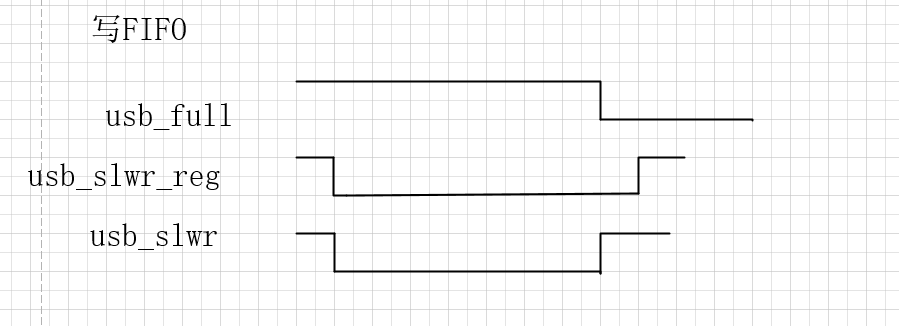

1 module top( 2 // system signals 3 input s_rst_n , 4 // system signals 5 input usb_ifclk , 6 input usb_full , 7 input usb_empty , 8 output wire usb_slcs , 9 output wire usb_slwr , 10 output wire usb_slrd , 11 output wire usb_sloe , 12 output wire [ 1:0] usb_fifoadr , 13 output reg [15:0] usb_fdata 14 ); 15 16 //========================================================================\ 17 // =========== Define Parameter and Internal signals =========== 18 //========================================================================/ 19 20 reg usb_slwr_reg ; 21 22 //============================================================================= 23 //************** Main Code ************** 24 //============================================================================= 25 assign usb_slcs = 1'b0; 26 assign usb_slwr = (usb_full == 1'b1 && usb_slwr_reg == 1'b0) ? 1'b0 : 1'b1; 27 assign usb_slrd = 1'b1; 28 assign usb_sloe = 1'b1; 29 assign usb_fifoadr = 2'b10; // 2,4,6,8 30 31 32 always @(posedge usb_ifclk or negedge s_rst_n) begin 33 if(s_rst_n == 1'b0) 34 usb_slwr_reg <= 1'b1; 35 else if(usb_full == 1'b1) 36 usb_slwr_reg <= 1'b0; 37 else 38 usb_slwr_reg <= 1'b1; 39 end 40 41 42 always @(posedge usb_ifclk or negedge s_rst_n) begin 43 if(s_rst_n == 1'b0) 44 usb_fdata <= 'd0; 45 else if(usb_slwr == 1'b0) 46 usb_fdata <= usb_fdata + 1'b1; 47 end 48 49 50 endmodule

介绍一下端口的设计:usb_ifclk :是输入时钟这是针对于FPGA来说,数据的输出和时钟都是基于此时钟,同步写数据的时候。

usb_full:写满标志,因为我们设置的是slave FIFO模式。高电平表示为写满,拉低的是后标志写满。

usb_empty:读空标志,高电平表示没有读空,拉低表示读空。

usb_scls:片选信号

usb_sloe:输出使能信号,

usb_slrd:;读触发信号

usb_slwr:写出发信号

usb_fifoadr[1:0]:表示你要操作那个FIFO

usb_fifodata[15:0]:表示传输的数据位。

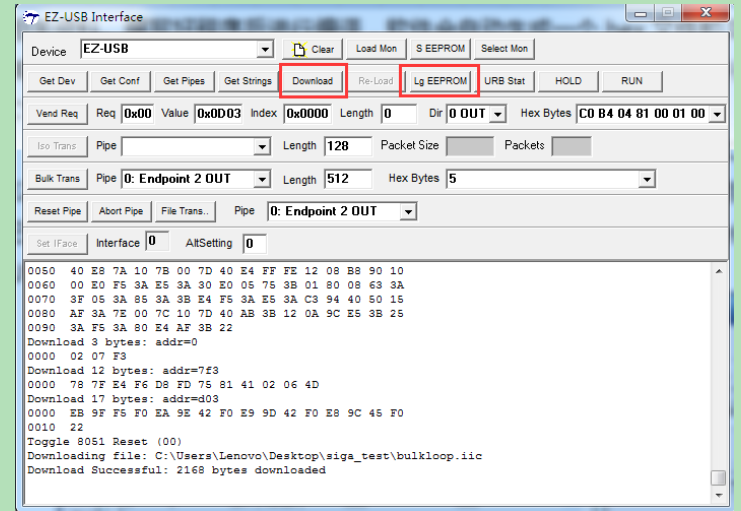

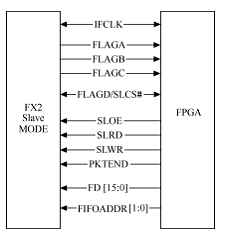

在数据手册中我们可以总结出的信号连接图在SlaveFIFO方式下,FPGA与FX2的连接信号图如图:

在数据手册中各个管脚的作用:

下面是信号线的说明。

IFCLK:FX2输出的时钟,可作为通信的同步时钟。

FLAGA、FLAGB、FLAGC、FLAGD:FX2输出的FIFO状态信息,如满、空等。

SLCS:FIFO的片选信号,外部逻辑控制,当SLCS输出高时,不可进行数据传输。

SLOE:FIFO输出使能,外部逻辑控制,当SLOE无效时,数据线不输出有效数据。

SLRD:FIFO读信号,外部逻辑控制,同步读时,FIFO指针在SLRD有效时的每个IFCLK的上升沿递增,异步读时,FIFO读指针在SLRD的每个有效至无效的跳变沿时递增。

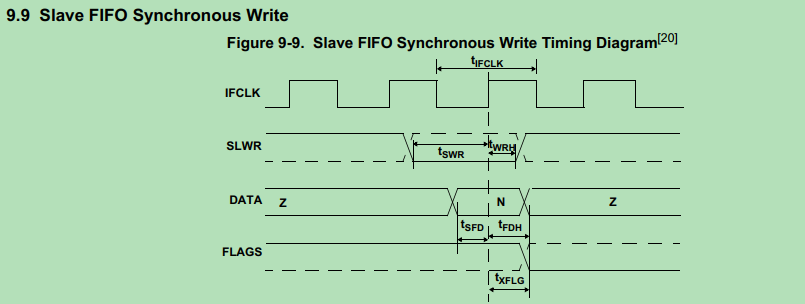

SLWR:FIFO写信号,外部逻辑控制,同步写时,在SLWR有效时的每个IFCLK的上升沿时数据被写入,FIFO指针递增,异步写时,在SLWR的每个有效至无效的跳变沿时数据被写入,FIFO写指针递增。

PKTEND:包结束信号,外部逻辑控制,在正常情况下,外部逻辑向FX2的FIFO中写数,当写入FIFO端点的字节数等于FX2固件设定的包大小时,数据将自动被打成一包进行传输,但有时外部逻辑可能需要传输一个字节数小于FX2固件设定的包大小的包,这时,它只需在写入一定数目的字节后,声明此信号,此时FX2硬件不管外部逻辑写入了多少字节,都自动将之打成一包进行传输。

FD[15:0]:数据线。

FIFOADR[1:0]:选择4个FIFO端点的地址线,外部逻辑控制。

逻辑思维梳理:

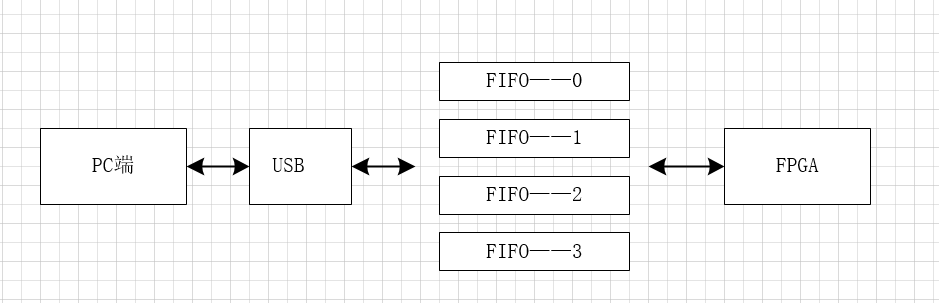

当按照以上所述的模式设置时。USB与PC端通信可以理解为以下模式:

官方同步写数据的时序图:

可以理解为以下时序图:

后续》》》》》