DMA cache一致性一:基本概念

本节内容参考《宋宝华:Linux设备驱动开发详解》

cache和DMA本身似乎是两个毫无关联的事物。cache被用作CPU针对内存的缓存,利用程序的空间局部性和时间局部性原理,达到较高的命中率,从而避免CPU每次都必须要与相对慢速的内存交互数据来提高数据的访问速率。DMA可以作为内存与外设之间传输数据的方式,在这种传输之下,CPU并不需要经过CPU中转

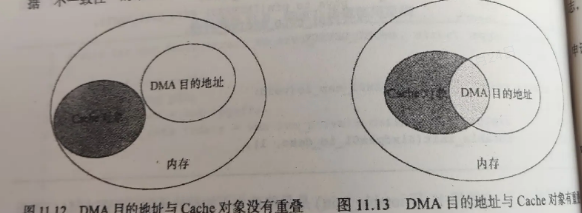

假设DMA针对内存的目的地址与cache缓存的对象没有重叠区域,DMA与cache之间相安无事。但是DMA的目的地址与cache缓存的内存地址访问有重叠,经过DMA操作,与cache缓存对应的内存中的数据已经被修改,而CPU本身并不知道,CPU仍然认为cache中的数据就是内存中的数据,那么以后访问cache映射的内存时,CPU仍然使用dirty的cache数据,这样就会发生cache与内存之间数据‘“不一致性”的错误,如下图:

所谓cache数据与内存数据的不一致性,是指采用cache的系统中,同样一个数据可能存在于cache中,也可能存在于主存中,cache与主存中的数据一样就具有一致性,数据若不一样则不具有一致性

需要特别注意,发生cache与内存不一致性错误后,驱动将无法正常运行,并且此种问题很难定位。cache的不一致性问题并不是只发生在DMA的情况下,实际上,它还存在cache使能和关闭的时候。例如,对于带MMU的ARM处理器,在开启MMU之前,需要先将cache无效,对于TLB,也是如此,下面的汇编可实现此功能:

// 使cache无效 mov r0,#0 mcr p15, 0, r0, c7, c7, 0 // 使数据和icache无效 mcr p15, 0, r0, c7, c10, 4 // 放空写缓冲 mcr p15, 0, r0, c8, c7, 0 // 使TLB无效

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 25岁的心里话

· 闲置电脑爆改个人服务器(超详细) #公网映射 #Vmware虚拟网络编辑器

· 零经验选手,Compose 一天开发一款小游戏!

· 通过 API 将Deepseek响应流式内容输出到前端

· AI Agent开发,如何调用三方的API Function,是通过提示词来发起调用的吗