ARM-V8基础知识学习笔记(一)

参考文章:ARM官方文档

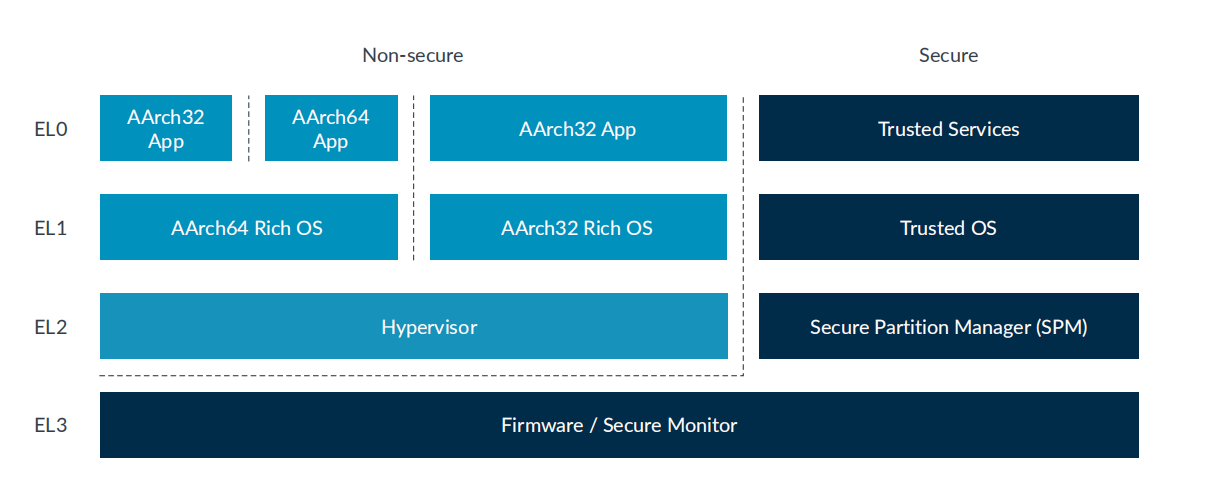

ARM异常等级:

在 ARMv8 中,执行发生在四个异常级别之一。在 AArch64 中,异常级别决定了特权级别,类似于ARMv7中定义的特权级别。异常级别决定特权级别,因此在 ELn 执行对应于特权PLn。类似地,具有比另一个更大的n值的异常级别处于更高的异常级别。一个数字比另一个小的异常级别被描述为处于较低的异常级别。

这里也显示出来了与ARM-V7的差异点,可参考https://www.cnblogs.com/lethe1203/p/18077266

异常级别提供了适用于 ARMv8 架构的所有操作状态的软件执行权限的逻辑分离。它类似于并支持计算机科学中常见的分层保护域的概念。

- EL0 Normal user applications.

- EL1 Operating system kernel typically described as privileged.

- EL2 Hypervisor.

- EL3 Low-level firmware, including the Secure Monitor.

通常,一个软件,例如应用程序、操作系统的内核或管理程序,占用一个异常级别。此规则的一个例外是内核中的虚拟机管理程序,例如 KVM,它在EL2和 EL1 上运行。

ARMv8‑A 提供两种安全状态,安全和非安全。非安全状态也称为正常世界。这使操作系统 (OS) 能够与受信任的操作系统在同一硬件上并行运新g,并提供针对某些软件攻击和硬件攻击的保护。 ARM

TrustZone 技术使系统能够在正常和安全世界之间进行分区。与 ARMv7‑A 架构一样,安全监视器充当在正常和安全世界之间移动的网关。

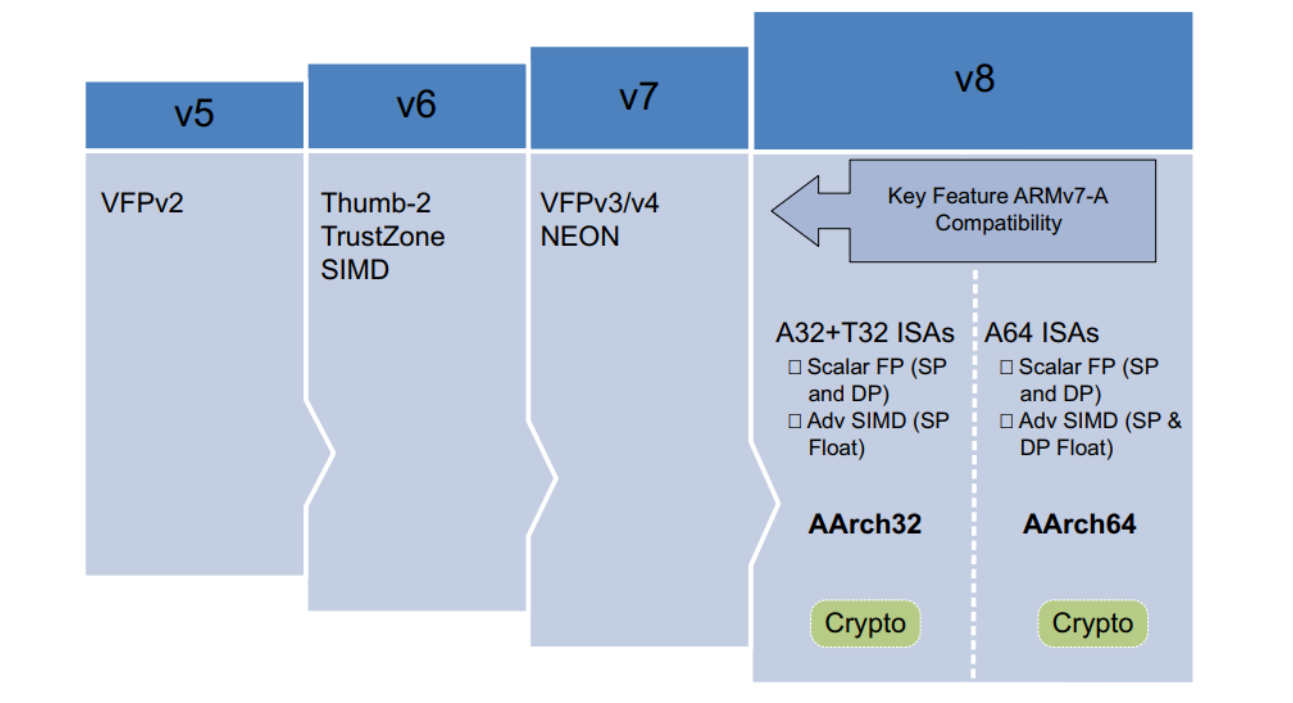

ARM-V8新更改:

ARMv8 体系结构包括 32 位执行和 64 位执行。它引入了使用 64 位宽寄存器,同时保持了与现有 ARMv7 软件的向后兼容性:

- 大物理地址(Large physical address),这使处理器能够访问超过 4GB 的物理内存。

- 64 位虚拟寻址(64-bit virtual addressing),这使虚拟内存超出 4GB 限制。这对于使用内存映射文件 I/O 或稀疏寻址的现代桌面和服务器软件很重要。

- 自动事件信号(Automatic event signaling),这可以实现节能、高性能的自旋锁

- 更大的寄存器文件(Larger register files),31 个 64 位通用寄存器可提高性能并减少堆栈使用。

- 高效的 64 位立即生成(Efficient 64-bit immediate generation),对文字池的需求较少

- 较大的 PC 相对寻址范围(Large PC-relative addressing range),一个 +/‑4GB 的寻址范围,用于在共享库和与位置无关的可执行文件中进行有效的数据寻址。

- 额外的 16KB 和 64KB 翻译颗粒(Additional 16KB and 64KB translation granules),这降低了翻译后备缓冲区(TLB) 未命中率和页面遍历深度。

- 新的异常模型(New exception model),这降低了操作系统和管理程序软件的复杂性。

- 高效的缓存管理理Efficient cache management),用户空间缓存操作提高了动态代码生成效率。使用数据缓存零指令快速清除数据缓存。

- 硬件加速密码学(Hardware-accelerated cryptography),提供 3 到 10 倍更好的软件加密性能。这对于小粒度解密和加密非常有用,因为太小而无法有效地卸载到硬件加速器,例如 https。

- 加载‑获取、存储‑释放指令(Load-Acquire, Store-Release instructions),专为 C++11、C11、Java 内存模型而设计。它们通过消除显式内存屏障指令来提高线程安全代码的性能。

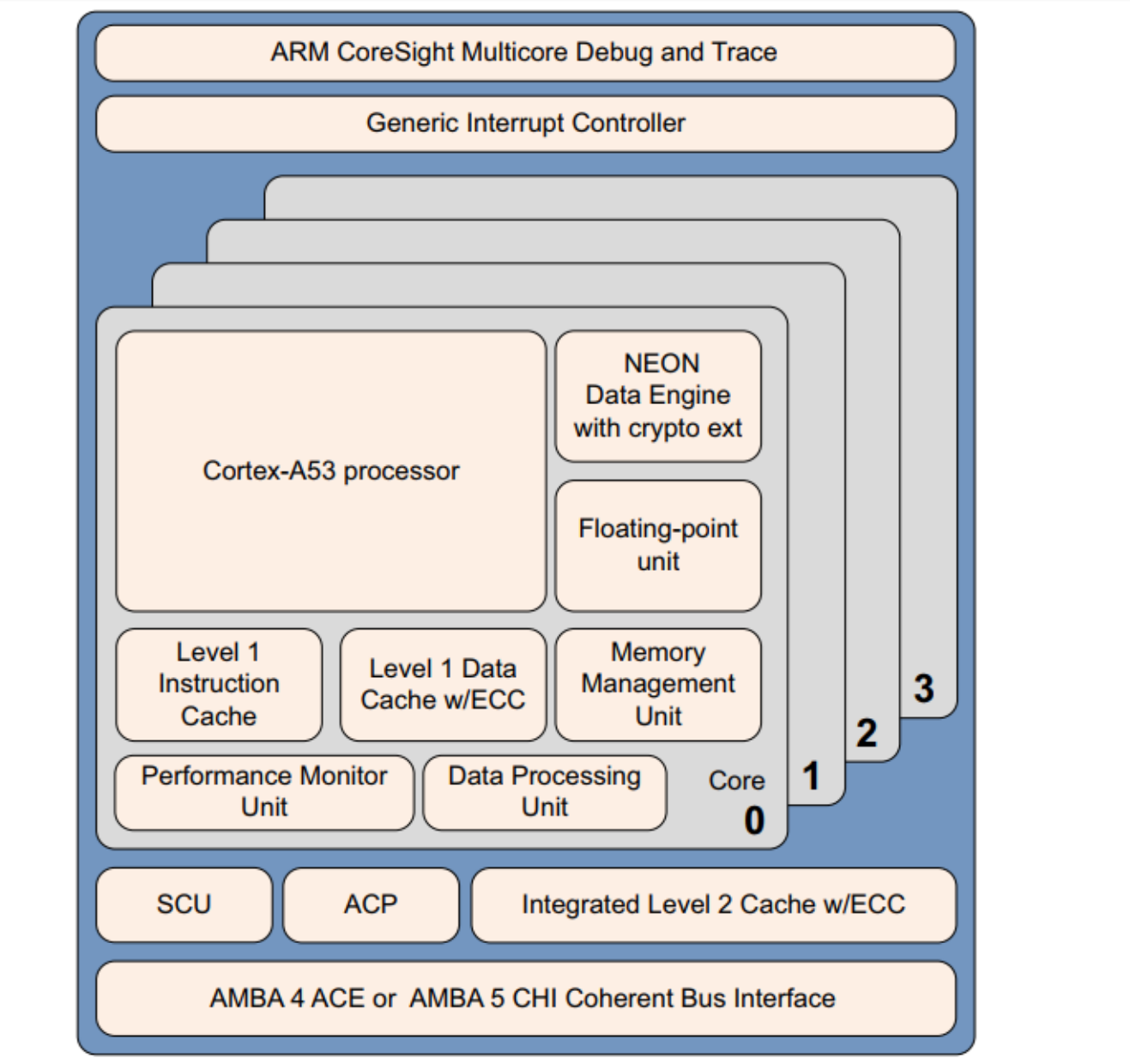

介绍下基于ARM-V8架构的Cortex-A53处理器:

Cortex‑A53 处理器是一款中档、低功耗处理器,在单个集群中具有一到四个内核,每个内核都有一个L1 缓存子系统、一个可选的集成 GICv3/4 接口和一个可选的 L2 缓存控制器。Cortex‑A53 处理器是一款非常节能的处理器,能够支持 32 位和 64 位代码。它提供了比非常成功的Cortex‑A7 处理器更高的性能。它能够部署为独立的应用处理器,或在 big.LITTLE 配置中与Cortex‑A57 处理器配对,以获得最佳性能、可扩展性和能源效率。

Cortex‑A53 处理器具有以下特性:

- 有序的八级流水线。

- 通过使用分层时钟门控、电源域和高级保留模式来降低功耗。

- 通过重复执行资源和双指令解码器提高双发能力。

- 功耗优化的二级缓存设计可提供更低的延迟并在性能与效率之间取得平衡。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具