ARM-V7架构(一)

cortex-A7基于ARMV7-A架构,复习一下armv7

ARM体系庞大,个人只复习下自己需要的基础知识,内容单薄

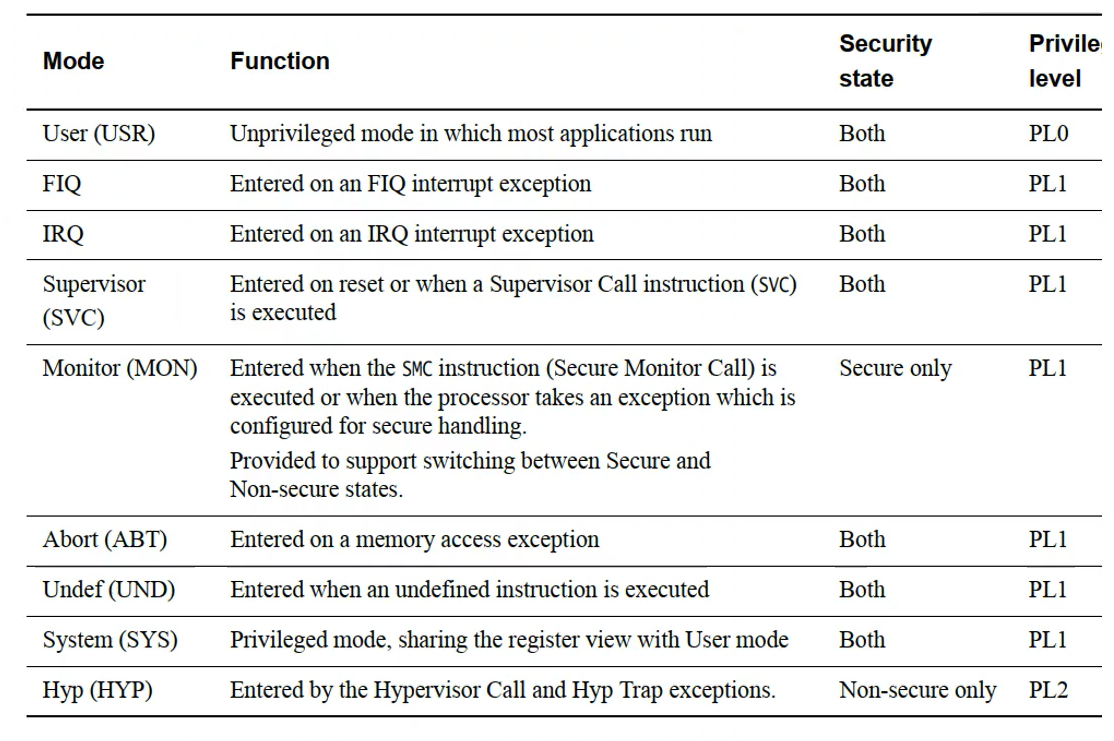

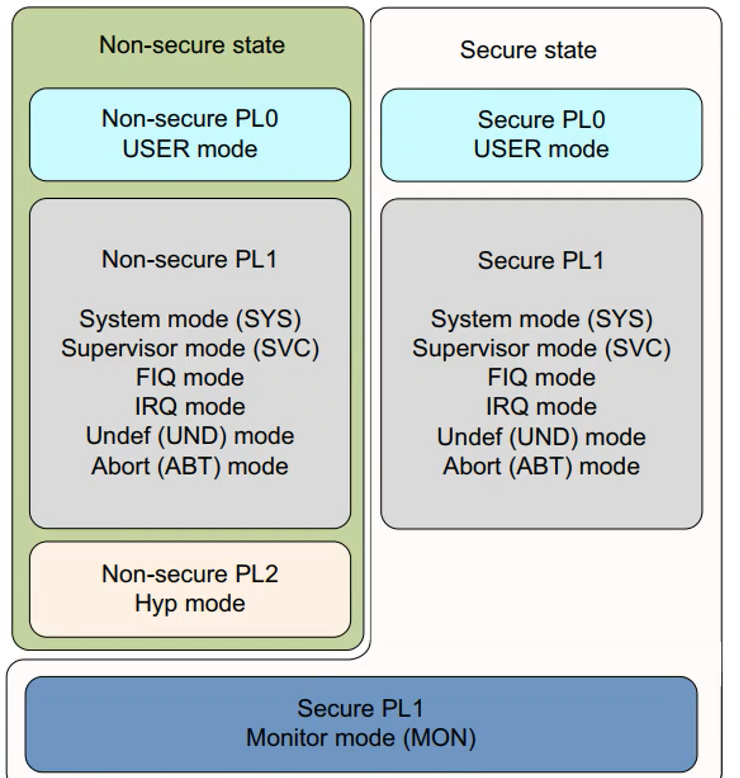

ARM-V7的模式类型如下:

FIQ快速中断和IRQ外部中断的区别:当一个高优先级中断产生时将会进入FIQ,一般用于高速数据传输和通道处理。当一个低优先级中断产生将会进入IRQ,一般用于通常的中断处理

处理器模式可以通过软件控制进行切换,也可以通过外部中断或异常处理过程进行切换。大多数用户程序运行在用户模式下。当处理器工作在用户模式时,应用程序不能访问受操作系统保护的一些系统资源,应用程序也不能直接进行处理器模式切换。当需要进行处理器模式切换时,应用程序可以产生异常处理,在异常处理过程中进行处理器模式切换。这种体系结构可以使操作系统控制整个系统资源的使用。

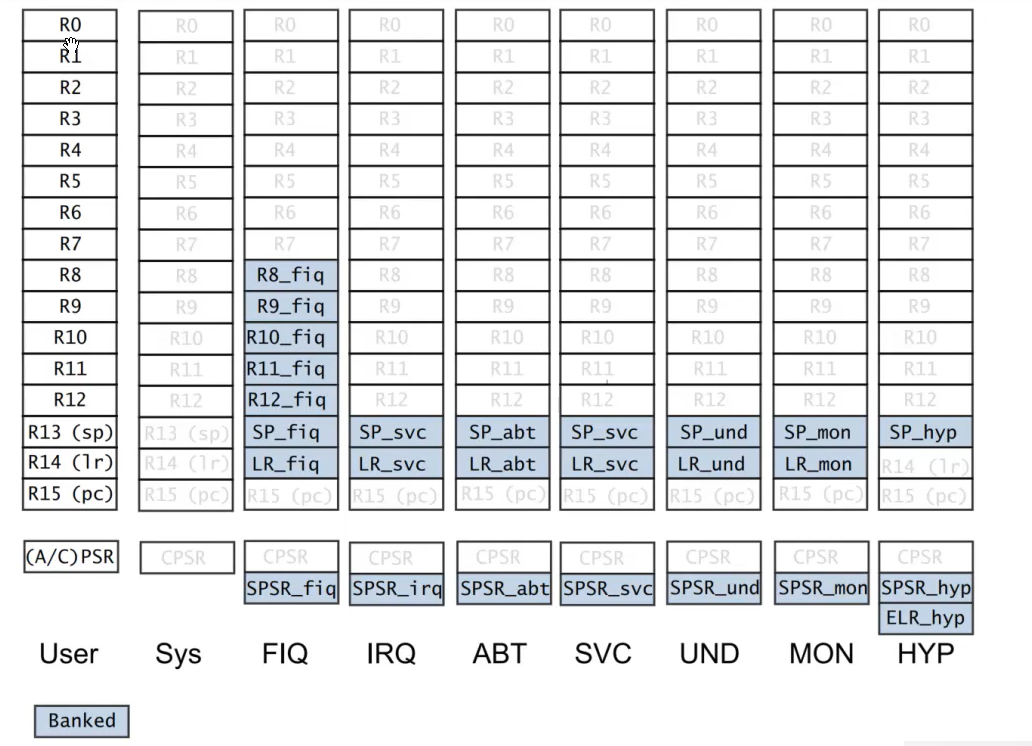

Cortex-A7处理器寄存器组:

1、在寄存器组中,每个方块都是一个寄存器,每个寄存器都是32位的

2、寄存器没有地址,访问寄存器通过编号进行访问,r0-r15,cpsr,spsr(spsr是cpsr的影子寄存器)

3、banked类型的寄存器属于该模式下私有的寄存器,而非banked类型的寄存器属于公有寄存器组

4、user模式和system模式最多可以访问17个寄存器,HYP模式最多可以访问19个寄存器,其他模式可访问18个寄存器

5、cortex-A7寄存器组中一共只有43个寄存器,因此开发中尽量不要定义register类型的变量

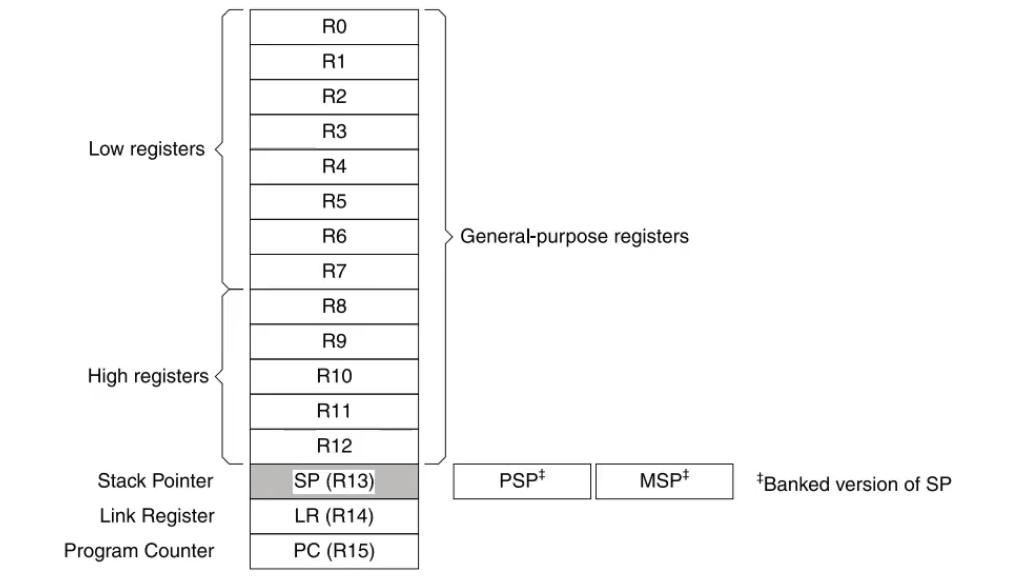

6、通用寄存器可分为两类:

未分组寄存器,包括R0-R7。

分组寄存器,包括R8-R12。

栈指针寄存器R13

R13寄存器在ARM处理器中常用为栈指针,称为SP。

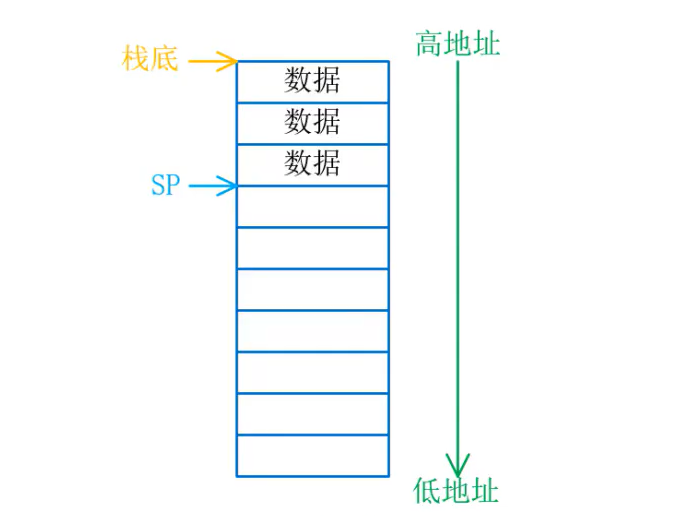

每一种异常模式拥有自己的R13。异常处理程序负责初始化自己的R13,使其指向该异常模式专用的栈地址。在异常处理程序入口处,将用到的其他寄存器的值保存在堆栈中,返回时,重新将这些值加载到寄存器。通过这种保护程序现场的方法,异常不会破坏被其中断的程序现场

SP栈指针寄存器存放的是栈指针指向的栈空间的地址。此栈是用来压栈保护现场的,特点是先进后出

满减栈如图所示:

代码分析:

给每一个模式都设置对应的栈空间

init_stack: ldr r0,stacktop /*get stack top pointer,stacktop是一个地址*/ /********svc mode stack********/ mov sp,r0 sub r0,#128*4 /*512 byte for irq mode of stack*/ /****irq mode stack**/ msr cpsr,#0xd2 /*切换至IRQ模式*/ mov sp,r0 sub r0,#128*4 /*512 byte for irq mode of stack*/ /***fiq mode stack***/ msr cpsr,#0xd1 mov sp,r0 sub r0,#0 /***abort mode stack***/ msr cpsr,#0xd7 mov sp,r0 sub r0,#0 /***undefine mode stack***/ msr cpsr,#0xdb mov sp,r0 sub r0,#0 /*** sys mode and usr mode stack ***/ msr cpsr,#0x10 mov sp,r0 /*1024 byte for user mode of stack*/

测试栈:

/****irq mode stack**/ msr cpsr,#0xd2 /*切换至IRQ模式*/ mov sp,r0 sub r0,#128*4 /*512 byte for irq mode of stack*/ mov r5, #0x11 /*0x11赋给r5*/ mov r6, #0x23 /*0x23赋给r6*/ stmfd sp!, {r5, r6} /*r5,r6入栈*/ ldmfd sp!, {r7, r8} /*出栈值给到r7, r8*/

监控寄存器的值和栈指针的变化:

|

寄存器

|

执行完第四行

|

执行完第五行

|

执行完第六行

|

执行完第七行

|

执行完第八行

|

|

r5

|

0

|

0x11

|

0x11

|

0x11

|

0x11

|

|

r6

|

259635441

|

259635441

|

0x23

|

0x23

|

0x23

|

|

r7

|

1667

|

1667

|

1667

|

1667

|

0x11

|

|

r8

|

384526877

|

384526877

|

384526877

|

384526877

|

0x23

|

|

sp

|

0xc200844

|

0xc200844

|

0xc200844

|

0xc20083c

|

0xc200844

|

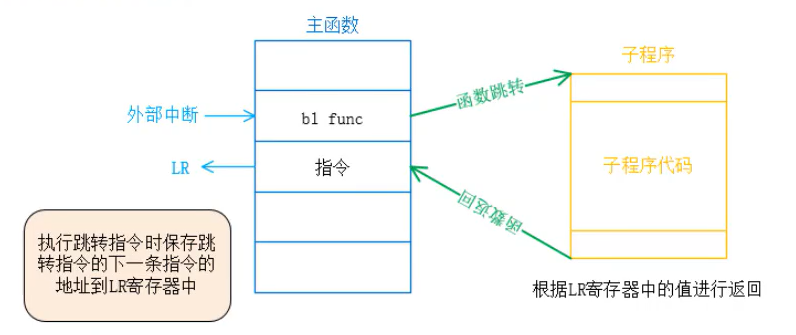

连接寄存器R14:

寄存器R14又被称为连接寄存器(Link Register,LR),可以被用作通用寄存器使用。在ARM体系结构中具有下面两种特殊的作用。每一种处理器模式用自己的R14存放当前子程序的返回地址,比如中断异常处理模式。当通过BL或BLX指令调用子程序时,R14被设置为该子程序的返回地址。在子程序返回时,把R14的值复制给程序计数器PC,典型的用法如下:

使用方法一:

mov pc,lr

bx lr

使用方法二:

在子程序入口处使用下面的指令将PC保存到栈中。

stmfd sp!, {,lr}

在子程序返回时,使用以下相应的配套指令返回:

ldmfd sp!, {,pc}

当异常中断发生时,该异常模式特定的物理寄存器R14被设置为该异常模式的返回地址。

程序计数寄存器R15:

R15又被称为PC程序计数寄存器。PC寄存器中存储的是当前取值的指令的地址,当完成取值操作之后,PC中的值会自动加4指向下一条指令

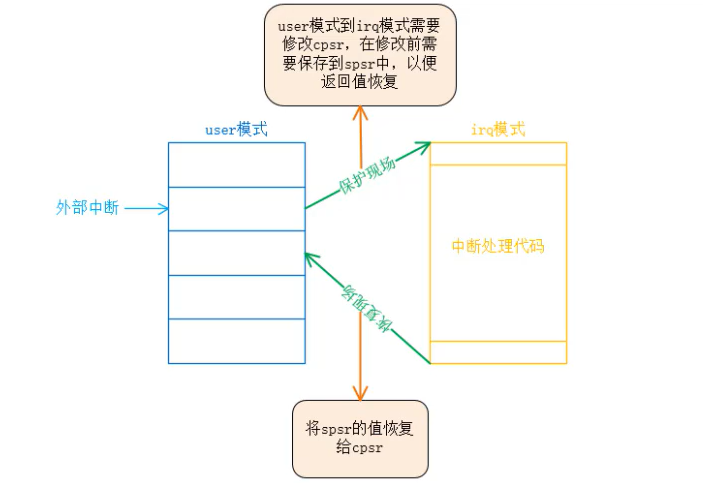

程序状态寄存器CPSR:

所有的处理器模式都共用一个 CPSR 物理寄存器,因此 CPSR 可以在任何模式下被访问。CPSR 是当前程序状态寄存器,该寄存器包含了条件标志位、中断禁止位、当前处理器模式标志

等一些状态位以及一些控制位。所有的处理器模式都共用一个 CPSR 必然会导致冲突,为此,除了 User 和 Sys 这两个模式以外,其他 7 个模式每个都配备了一个专用的物理状态寄存器,叫

做 SPSR(备份程序状态寄存器),当特定的异常中断发生时,SPSR 寄存器用来保存当前程序状态寄存器(CPSR)的值,当异常退出以后可以用 SPSR 中保存的值来恢复 CPSR。

因为 User 和 Sys 这两个模式不是异常模式,所以并没有配备 SPSR,因此不能在 User 和Sys 模式下访问 SPSR,会导致不可预知的结果。由于 SPSR 是 CPSR 的备份,因此 SPSR 和CPSR 的寄存器结构相同,

CPSR寄存器包含下列内容:

- ALU(逻辑运算单元)状态标志

- 当前处理器模式

- 中断使能标志

- 设置处理器的状态

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具