ARM MMU和cache简介

参考博客:

MMU:memory management unit,称为内存管理单元,或者是存储器管理单元,MMU是硬件设备,它被保存在主存(main memory)的两级也表控制,并且是由协处理器CP15的寄存器1的M位来决定是enabled还是disabled。MMU的主要作用是负责从CPU内核发出的虚拟地址到物理地址的映射,并提供硬件机制的内存访问权限检查。MMU使得每个用户进程拥有自己的地址空间(对于WINCE5.0,每个进程是32MB;而对于WINCE6.0,每个进程的独占的虚拟空间是2GB),并通过内存访问权限的检查保护每个进程所用的内存不被其他进程破坏。

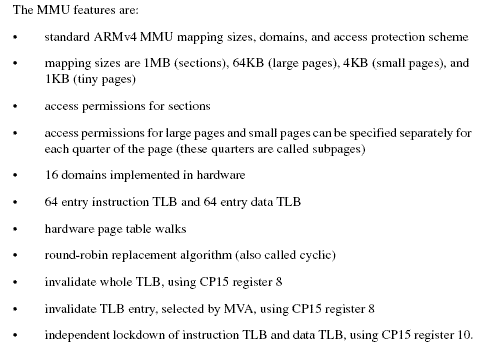

mmu features:

基础概念:

VA:virtual address称为虚拟地址,PA:physical address称为物理地址。CPU通过地址来访问内存中的单元,如果CPU没有MMU,或者有MMU但没有启动,那么CPU内核在取指令或者访问内存时发出的地址(此时必须是物理地址,假如是虚拟地址,那么当前的动作无效)将直接传到CPU芯片的外部地址引脚上,直接被内存芯片(物理内存)接收,这时候的地址就是物理地址。如果CPU启用了MMU(一般是在bootloader中的eboot阶段的进入main()函数的时候启用),CPU内核发出的地址将被MMU截获,这时候从CPU到MMU的地址称为虚拟地址,而MMU将这个VA翻译成为PA发到CPU芯片的外部地址引脚上,也就是将VA映射到PA中。MMU将VA映射到PA是以页(page)为单位的,对于32位的CPU,通常一页为4k,物理内存中的一个物理页面称页为一个页框(page frame)。虚拟地址空间划分成称为页(page)的单位,而相应的物理地址空间也被进行划分,单位是页框(frame).页和页框的大小必须相同。

CPU访问内存时的硬件操作顺序:

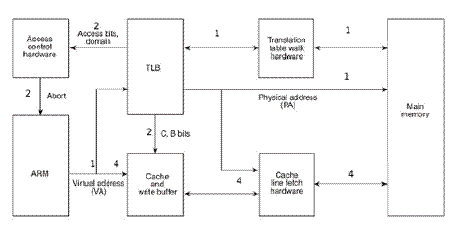

CPU访问内存时的硬件操作顺序,各步骤在图中有对应的标号:

1 CPU内核(图中的ARM)发出VA请求读数据,TLB(translation lookaside buffer)接收到该地址,那为什么是TLB先接收到该地址呢?因为TLB是MMU中的一块高速缓存(也是一种cache,是CPU内核和物理内存之间的cache),它缓存最近查找过的VA对应的页表项,如果TLB里缓存了当前VA的页表项就不必做translation table walk了,否则就去物理内存中读出页表项保存在TLB中,TLB缓存可以减少访问物理内存的次数。

2 页表项中不仅保存着物理页面的基地址,还保存着权限和是否允许cache的标志。MMU首先检查权限位,如果没有访问权限,就引发一个异常给CPU内核。然后检查是否允许cache,如果允许cache就启动cache和CPU内核互操作。

3 如果不允许cache,那直接发出PA从物理内存中读取数据到CPU内核。

4 如果允许cache,则以VA为索引到cache中查找是否缓存了要读取的数据,如果cache中已经缓存了该数据(称为cache hit)则直接返回给CPU内核,如果cache中没有缓存该数据(称为cache miss),则发出PA从物理内存中读取数据并缓存到cache中,同时返回给CPU内核。但是cache并不是只去CPU内核所需要的数据,而是把相邻的数据都去上来缓存,这称为一个cache line。例如ARM920T的cache line是32个字节,例如CPU内核要读取地址0x30000134~0x3000137的4个字节数据,cache会把地址0x30000120~0x3000137(对齐到32字节地址边界)的32字节都取上来缓存。

cache的由来:

cpu访问速度和内存速度严重不匹配,由此引出了cache的概念,即高速缓存区。高速缓存区的速率跟cpu访问相匹配。

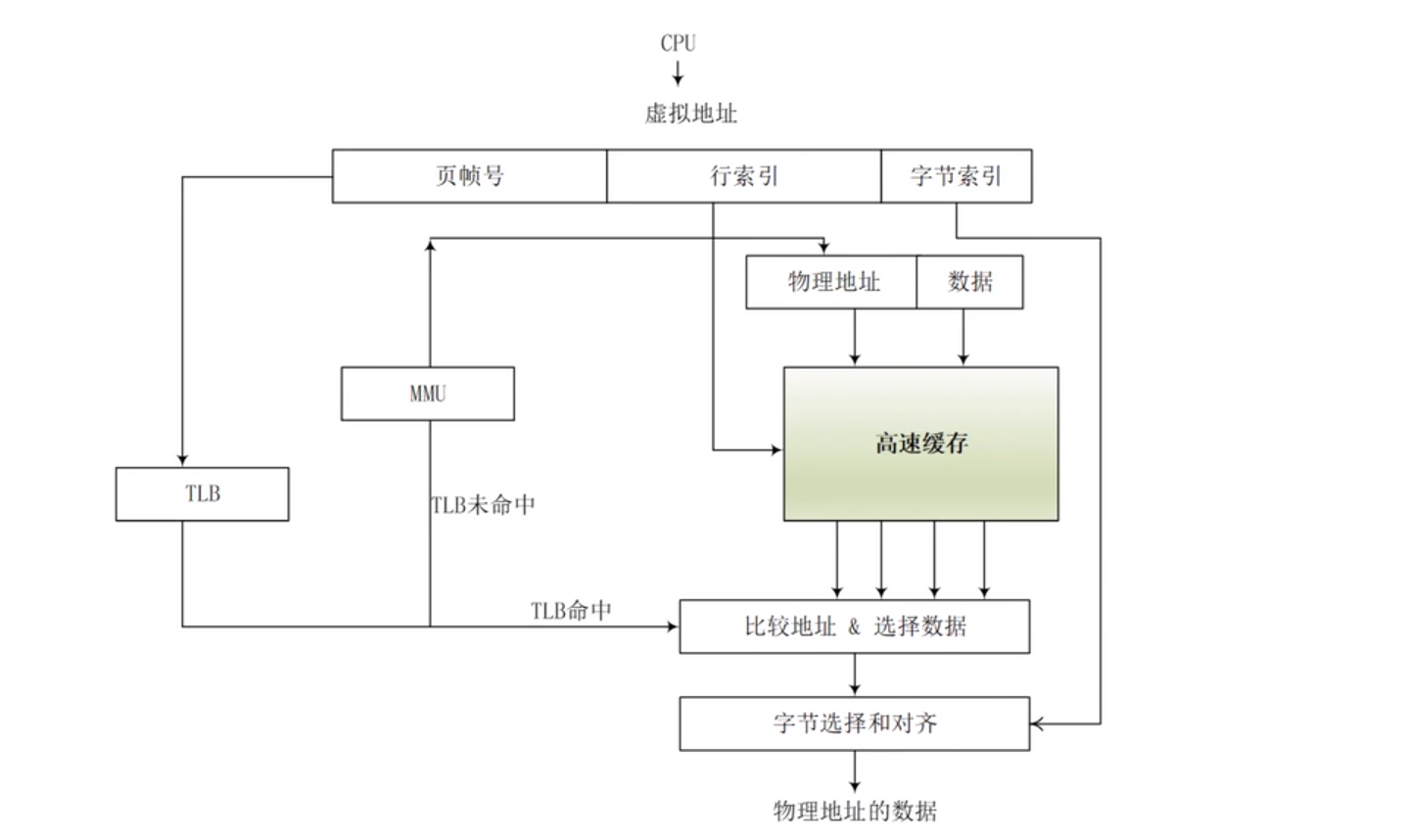

经典cache架构VIPT(Virtually Indexed, Physically Tagge)缓存结构与访存方式:

CPU发出的地址是虚拟地址,CPU访问内存会把该地址发送给TLB和cache,TLB是MMU的一块小缓冲区,用来存放虚拟地址和物理地址的映射关系。处理器会使用EPN(Effective Page Number),kernel会维护一个页表,将虚拟地址的EPN映射到物理内存中的页框号。这个映射关系由kernel进行管理和维护。经过TLB,如果有对应的RPN(real page number),则会出现TLB命中,如果TLB未命中,那么则需要访问MMU了。CPU发出的虚拟地址在cache中查找时,如果要访问的数据或者指令在cache中已经存在了,这种情况则成为cache hit,在缓存命中的情况下,CPU可以直接从缓存中获取所需要的数据,而无需访问更慢的主存。相反,如果访问的数据或指令不在cache中,需要从主存中加载到cache中,这种情况被称为cache miss,cache miss会导致额外的访问延迟。

除了上述说明的VIPT,还有VIVT,PIPT等等cache架构方式

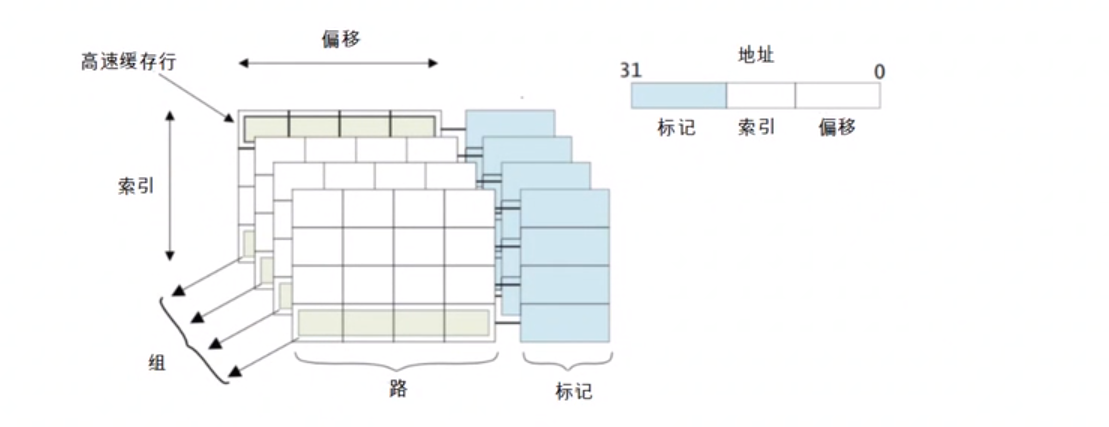

cache内部结构图:

高速缓存行:高速缓存中最小的访问单元

tag:存储在cache中的内存地址的一部分,用于标识与此行数据关联的主内存地址。64位地址中的top bits来告诉cache这个数据来自主内存的位置,称为tag。虽然total cache size表示cache可以保存的总的数据量,但是用于保存tag的RAM没有包含在total cache size中。而且tag会占用cache的物理空间

cache line:如果每个cache中的主内存地址都对应一个tag,光保存tag就会占用很大空间,效率十分低下,因此,cache中通常用一个tag记录主存中的连续字块,cache中的这个逻辑块通常被称为cache line,代表缓存中最小的可加载单元。cache line包含缓存数据或指令时称为valid,不包含缓存数据或指令时称为invalid。与cache line关联的是一个或多个状态位。通常,有一个valid bit来标识此cache line包含可使用的数据,这意味着地址标签代表一些实际值。在dcache中,还可能有一个或多个dirty bits,用于标记cache line(或其中一部分)是否包含与主内存内容不同(更新)的数据。

index:索引是内存地址的一部分,用于确定在哪个cache line中找到地址。index用作cache RAMs的地址,不需要作为tag的一部分进行存储。后面将更详细地介绍这一点。

way/set:way是cache的一个细分,每个way大小相同,索引方式相同。set由所有ways中index相同的cache lines组成

这意味着地址底部的几个位(称为偏移量)不需要存储在tag中。你需要整行的地址,而不是该行中的每个字节的地址,因此五个或六个最低位始终为0

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 无需6万激活码!GitHub神秘组织3小时极速复刻Manus,手把手教你使用OpenManus搭建本

· Manus爆火,是硬核还是营销?

· 终于写完轮子一部分:tcp代理 了,记录一下

· 别再用vector<bool>了!Google高级工程师:这可能是STL最大的设计失误

· 单元测试从入门到精通