SMMU简介

名词解析:

TCU:translation control unit

TBU:tanslation buffer unit

IOVA:IO virtual address

IPA:intermediate physical address

SMMU基础概念:

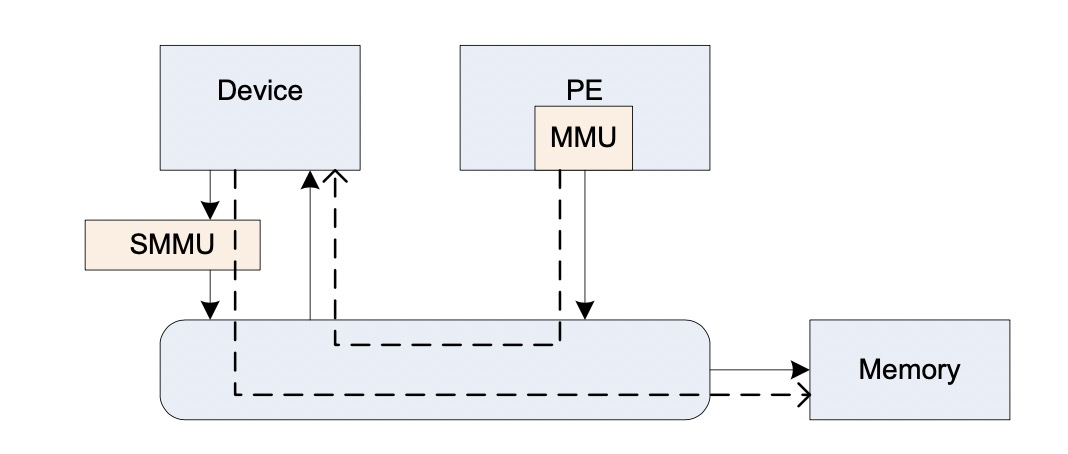

MMU是用于CPU访问资源(DDR、外设等)做地址转换,SMMU是用于外设(可以发起访问的master设备)访问资源(DDR、外设等)做地址转换的。

TCU用来管理页表,master发出一个VA请求,首先到TCU,TCU会去找页表,找到之后将PA传给TBU,TBU实际发送访问

TCU:SMMU(System MMU)中的子模块,主要负责地址转换和内存访问权限的控制。

在虚拟化环境中,SMMU起到了管理设备和主存之间内存映射关系的作用。SMMU TCU是其中一个重要的组成部分,它负责处理虚拟地址到物理地址的转换和权限控制。

SMMU TCU通过管理页表或映射表等数据结构来实现地址转换。当设备发送一个虚拟地址到SMMU时,TCU会根据页表或映射表查找相应的映射关系,然后将虚拟地址转换为物理地址。这个过程可能需要考虑页表的级联、TLB(Translation Lookaside Buffer)缓存的管理等。

同时,SMMU TCU也负责对内存访问的权限进行控制。它会检查设备对内存的读写权限,并与页表或映射表中的权限位进行比较,以确定是否允许设备执行相应的内存访问操作。

通过使用SMMU TCU,可以实现对设备访问物理内存的控制和隔离。它可以保护系统的安全性,防止设备越权访问内存,并提供更灵活的内存管理和地址转换功能,以适应虚拟化环境的需求。

TBU:SMMU(System MMU)中的子模块,主要用于缓存设备和SMMU之间交互的事务,以提高系统性能。

在虚拟化环境中,SMMU起到了管理设备与主存之间内存映射关系的作用。当设备进行一次内存访问时,需要经过多次的地址转换和权限检查等操作。这些操作可能涉及到多个硬件模块和复杂的计算,会对系统性能产生负面影响。

为了提高系统性能,SMMU引入了TBU模块。当设备发送一个内存访问请求到SMMU时,TBU会将请求缓存到内部的事务队列中,并等待SMMU完成相关操作后再将结果返回给设备。这样,在多个访问请求之间可以实现乱序执行,从而提高系统并发度和吞吐量。

同时,SMMU TBU还支持多种优化技术,例如乱序执行、流水线运行、事务合并等。这些技术可以进一步提高系统性能,减少因硬件调度带来的延迟和开销,并确保设备和SMMU之间的数据一致性

IOVA是设备的虚拟地址,它是设备看到的地址。当设备进行DMA访问时,使用的是IOVA作为地址进行内存操作。IOVA通常是由设备驱动程序根据设备的规格和约束生成的,用于标识设备需要读写的内存位置。

IPA是系统中的一个特定地址空间,用于表示设备访问的中间物理地址。当设备的IOVA需要转换成物理地址时,系统会使用SMMU(System MMU)等硬件模块将IOVA转换为IPA,然后再进一步转换为最终的物理地址。

这个IOVA到IPA的转换过程涉及到地址映射和权限控制等操作。在虚拟化环境下,SMMU负责管理设备和主存之间的内存映射关系,并进行IOVA到IPA的转换。SMMU会根据页表或映射表等数据结构,查找对应的映射关系,将IOVA转换为IPA,然后再由物理地址生成最终的物理地址。

TLB:System MMU Translation Lookaside Buffer,是SMMU的翻译后备缓冲器

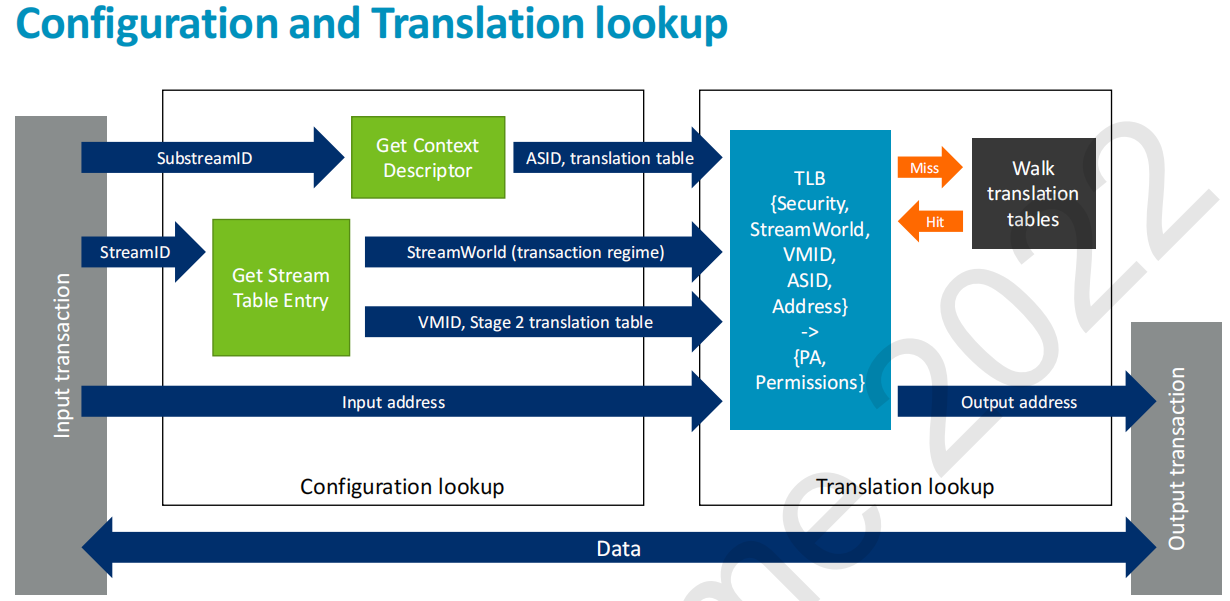

StreamID: device 通过物理线连接到SMMU ,这个StreamID就是用来标识SMMU上连接的设备。想象一个8 ports hub上连接了8个物理设备,这8个设备就可以通过portID来标识,比如port 0代表第一个设备,同理steamID。

STE: stream Table Entry,可以理解为SMMU页表转换的第一级索引,每一个streamID代表着一个STE,通过这个STE指向的连接可以找到真正的虚地址-->物理地址转换的页表。假设SMMU上连接着8个具体设备,每个设备都有自己的StreamID,那就有至少8个STE表项。

CD: Context Descriptor, stage 1的页表配置项,用于一个设备中不同的进程,它其中的TTB0指向了真正的页表信息,比如PGD, PMD, PTE等,完全和MMU的页表转换原理一样;

SMMU输入:substreamId,streamId,input address

master在访问某个地址时,就会随着地址一并发出substreamId,streamId给到SMMU

SMMU根据streamID和substreamID来做index找到对应的页表,然后进行地址转换

SMMU的数据结构:

smmu的重要的用来dma地址翻译的数据结构都是放在内存中的,由smmu的寄存器保存着这些表在内存中的基地址,首先就是Stream

Table Entry(STE),这ste 表既包含stage1的翻译表结构也包含stage2的翻译结构,所谓stage1负责VA 到 PA的转换,stage2负责IPA到PA的转换。

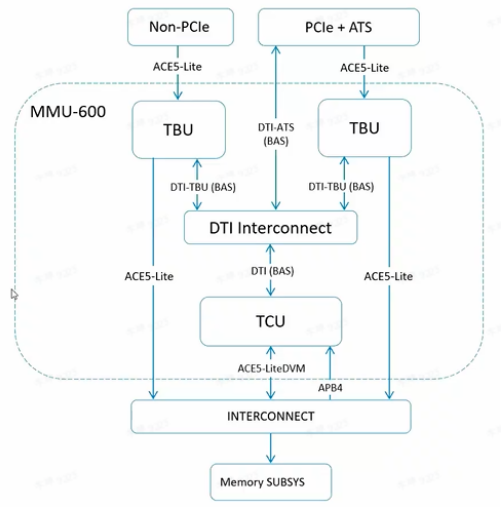

SMMU的组成:

TCU + N TBU的分布式设计(一个SMMU至少包含一个TCU和一个TBU),TBU一般是放在靠近master的地方,TCU一般是放在离interconnect近的地方

TBU:内部是包含TLB的,⽤来直接连接上游master。

TLB:前面介绍到的用于缓存VA->PA转换关系的一种特殊cache。

TCU:这个是⽤来直接是跟TBU连接的,负责page table walk或者是configuration table walk(STE、CD的信息等)。TCU主要就是负责把这些信息拿回来,包括event queue的访问等也是TCU。TCU内部也是有⼀些cache,但是不叫TLB cache。

DTI:TBU和TCU之间的双向交互的通信协议。