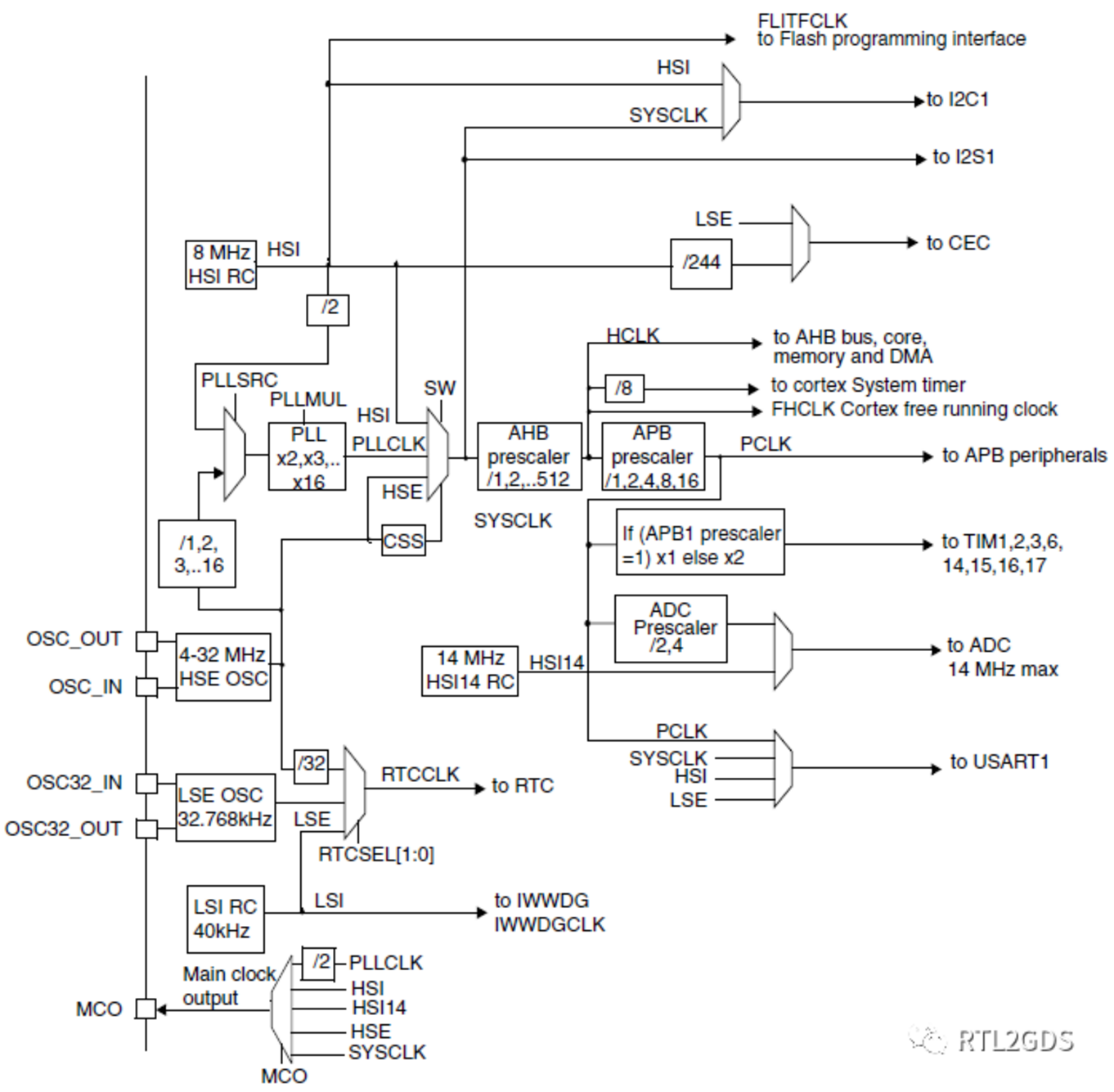

基于详细的时钟结构图,定义时钟的命令有两个:create_clock和create_generated_clock

其中,create_clock命令比较简单易懂,格式如下

create_clock [-name clock_name] \-period period_value \[-waveform edge_list] \[-add] \[source_objects]

create_generated_clock命令解析:create_generated_clock命令格式如下,主要是定义generated clock和master clock的关系:

create_generated_clock [-name clock_name] \-source master_pin \[-master_clock clock] \[-edge edge_list] \[-edge_shift shift_list] \[-divide_by factor] \[-multiply_by factor] \[-duty_cycle percent] \[-combinational][-add] \source_objects

create_generated_clock 需要指定源时钟(master clock)的master_pin,在CTS时,默认会去balance这两个时钟(即generated clock 和 master clock),让skew尽可能小。

而且在计算generated clock的clock latency时,会把从master clock pin 到generated clock pin之间的delay也考虑在内。

在工具中report_timing的时候,通过选项-path_type full_clock_expanded可以将master clock的部分也展开。

report_timing -path_type full_clockreport_timing -path_type full_clock_expanded

需要注意:在使用create_generated_clock时,需要保证电路结构和命令的效果是一致的,否则工具在report_timing时会报错,比如下面的错误(UITE-461),这时就要仔细检查分频电路结构了。

Error: Generated clock 'CLKdiv2 with source pin Udiv/Q' 'rise_edge' is not satisfiable; zerosource latency will be used. (UITE-461)Error: Generated clock 'CLKdiv2 with source pin Udiv/Q' 'fall_edge' is not satisfiable; zerosource latency will be used. (UITE-461)

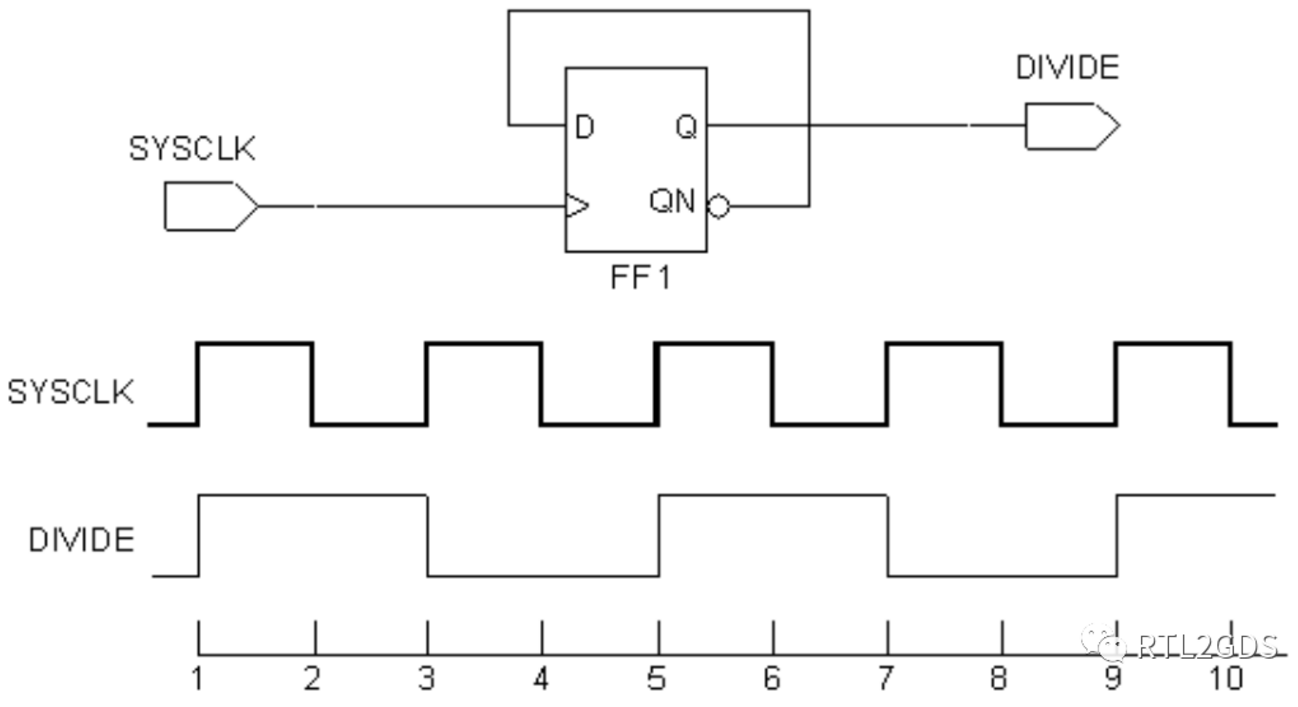

简单2分频

先看一个简单的2分频的实际的例子,命令和效果图如下:

create_clock -name SYSCLK \-period 2 \[get_ports SYSCLK]create_generated_clock -name DIVIDE \-source [get_ports SYSCLK] \-divide_by 2 \[get_pins FF1/Q]

![]()

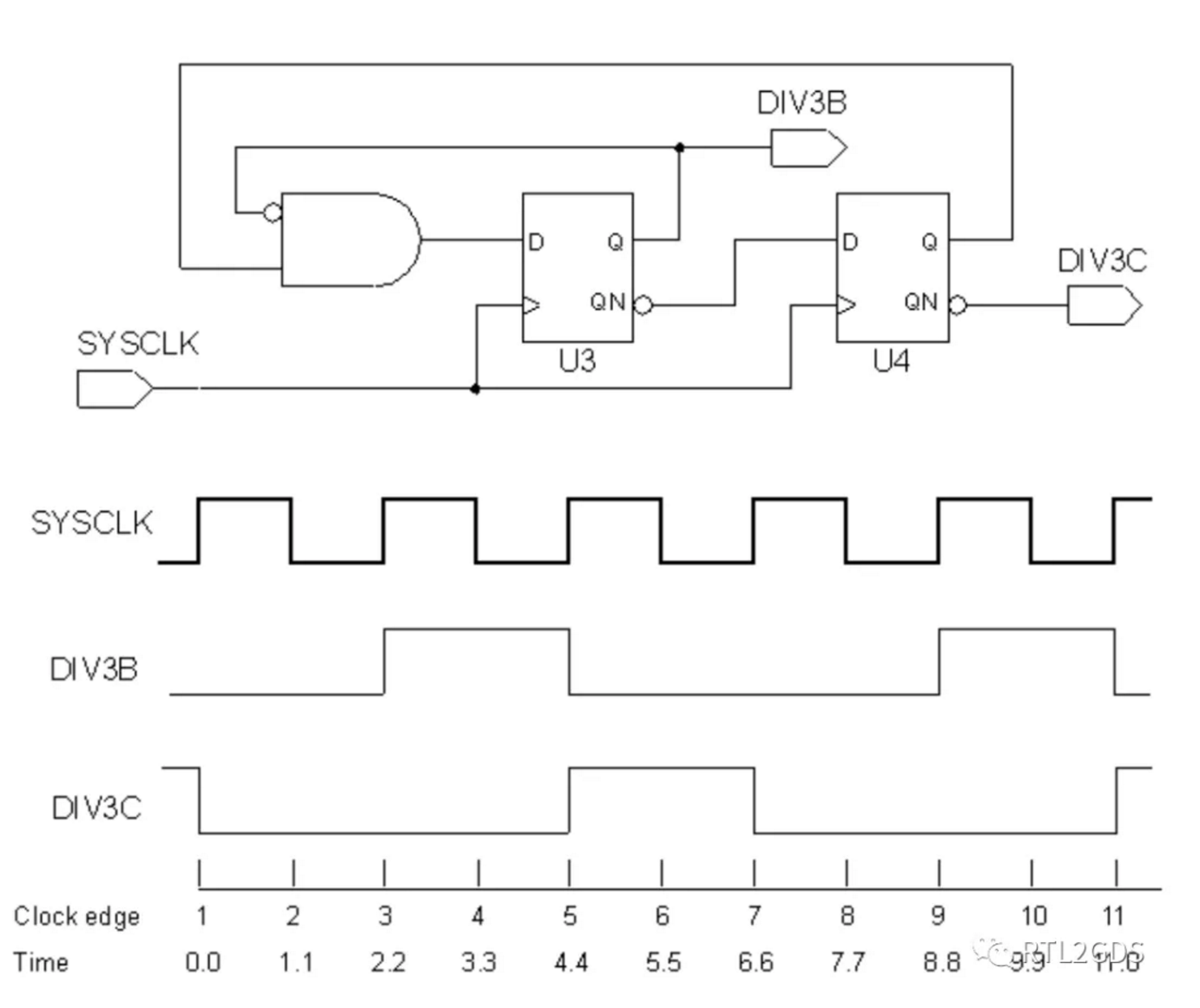

考虑了edge/edge_shift的3分频实例

下面是3分频的实例,-edge选项中{3 5 9}分别表示SYSCLK的第3、5、9个时钟沿(clock edge),也分别对应DIV3B的一个完整时钟周期(上升、下降、上升)的时钟沿时间点。

而-edge_shift选项{2.2 2.2 2.2}表示将DIV3B每个时钟沿都往后延迟2.2ns,命令和效果图如下:

create_clock -name SYSCLK \-period 2.2 \[get_ports SYSCLK]create_generated_clock -name DIV3B \-source [get_ports SYSCLK] \-edges { 3 5 9 } \[get_pins U3/Q]create_generated_clock -name DIV3C \-source [get_ports SYSCLK] \-edges { 3 5 9 } \-edge_shift {2.2 2.2 2.2} \[get_pins U4/QN]

![]()

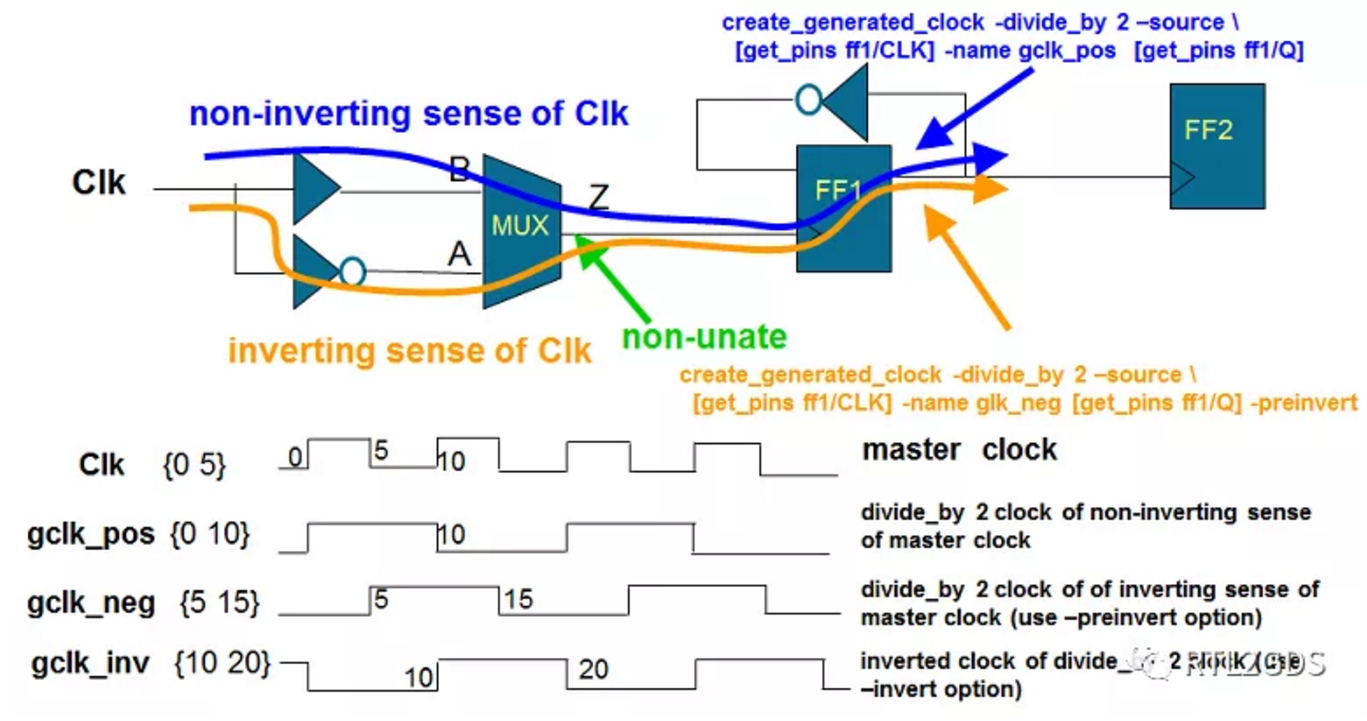

考虑invert/preinvert的实例

create_generated_clock使用-invert/-preinvert选项都表明generated clock与master clock相位相反,但这两个选项的区别是:

-

preinvert : Creates a generated clock based on the inverted sense of the master clock.

-

invert : Creates an inverted generated clock based on the non-inverted sense of the master clock.

命令和效果图如下:

create_generated_clock -name gclk_pos \-source [get_pins FF1/CLK] \-divide_by 2 \[get_pins FF1/Q]create_generated_clock -name gclk_neg \-source [get_pins FF1/CLK] \-divide_by 2 \-preinvert \[get_pins FF1/Q]create_generated_clock -name glk_inv \-source [get_pins FF1/CLK] \-divide_by 2 \-invert \[get_pins FF1/Q]

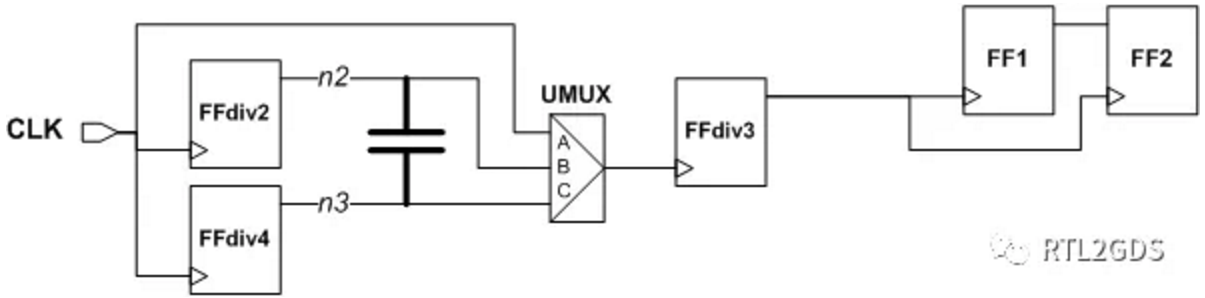

同一点定义多个generated clock

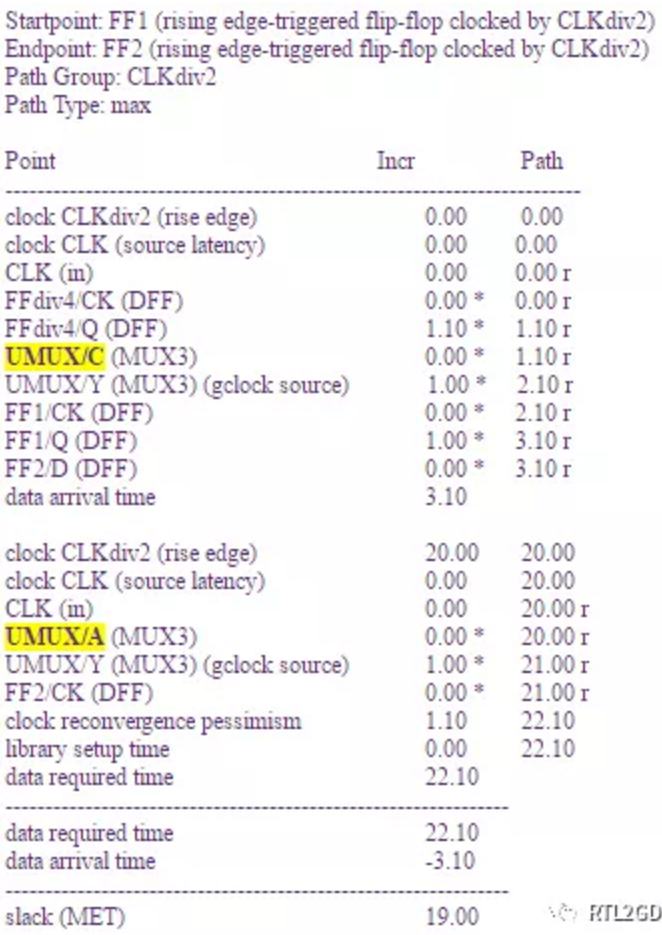

在实际电路中比较常见的情况是,不同的场景下使用不同频率的时钟来驱动电路,如下图所示,同一个时钟,与经过二分频,四分频后的时钟经过MUX输出给电路使用。

这种情况下,需要在UMUX输出点定义三个时钟CLKbypass/CLKdiv2/CLKdiv4,而且这三个时钟在物理上是不能共存的(physically_exclusive),可以考虑使用以下命令来定义时钟:

create_clock -period 10 CLKcreate_generated_clock -name CLKbypass \-source [get_ports CLK] \-master CLK \-divide_by 1 \-combinational \-add \UMUX/Ycreate_generated_clock -name CLKdiv2 \-source FFdiv2/CK \-master CLK \-divide_by 2 \-add \UMUX/Ycreate_generated_clock -name CLKdiv4 \-source FFdiv4/CK \-master CLK \-divide_by 4 \-add \UMUX/Yset_clock_groups -physically_exclusive \-group {CLKbypass} \-group {CLKdiv2} \-group {CLKdiv4}

注意,这种方式定义时钟看似合理,但是容易造成问题,因为在CLK和UMUX/Y之间有三条不同的路径,延迟大小不同,所以在计算timing时,在launch path和capture path上选择的路径会不同,带来悲观的影响,如下图所示,也有可能在计算min_pulse_width时造成假的违例。

在Solvnet上给出了更恰当的处理方式,具体命令如下:

create_clock -period 10 CLKcreate_generated_clock -name CLKdiv2 -divide_by 2 FFdiv2/Q -source FFdiv2/CKcreate_generated_clock -name CLKdiv4 -divide_by 4 FFdiv4/Q -source FFdiv4/CKcreate_generated_clock -name CLK_mux -combinational UMUX/A -source UMUX/Acreate_generated_clock -name CLKdiv2_mux -combinational UMUX/B -source UMUX/Bcreate_generated_clock -name CLKdiv4_mux -combinational UMUX/C -source UMUX/Ccreate_generated_clock -name CLK_mux_div3 \-divide_by 3 FFdiv3/Q -source FFdiv3/CK -master CLK_mux -addcreate_generated_clock -name CLKdiv2_mux_div3 \-divide_by 3 FFdiv3/Q -source FFdiv3/CK -master CLKdiv2_mux -addcreate_generated_clock -name CLKdiv4_mux_div3 \-divide_by 3 FFdiv3/Q -source FFdiv3/CK -master CLKdiv4_mux -addset_clock_groups -physically_exclusive \-group {CLK_mux CLK_mux_div3} \-group {CLKdiv2_mux CLKdiv2_mux_div3} \-group {CLKdiv4_mux CLKdiv4_mux_div3}

浙公网安备 33010602011771号

浙公网安备 33010602011771号