芯片制造涉及到许多复杂重复的过程,如:光刻、蚀刻、离子注入、扩散、退火。而且都是原子级操作,尽管控制非常严格,但偏差不可避免。

工艺偏差会导致芯片物理参数偏差,如:线宽、沟道掺杂浓度、线厚、临界尺寸、栅氧厚度;

而物理参数偏差会导致电特性参数偏差,如:线的电容电阻、阈值电压、饱和电流、栅极电容;

电特性参数偏差会导致 cell delay, cell transtion, net delay的偏差,这正是STA 要如此重视variation 的原因所在。

-

Environmental variation: 电压跟温度的变化,也就是PVT 中的V跟T。

-

Process variation: 工艺制造过程的偏差,工艺偏差一部分用PVT 中的P来模拟,另一部分用OCV 来模拟。

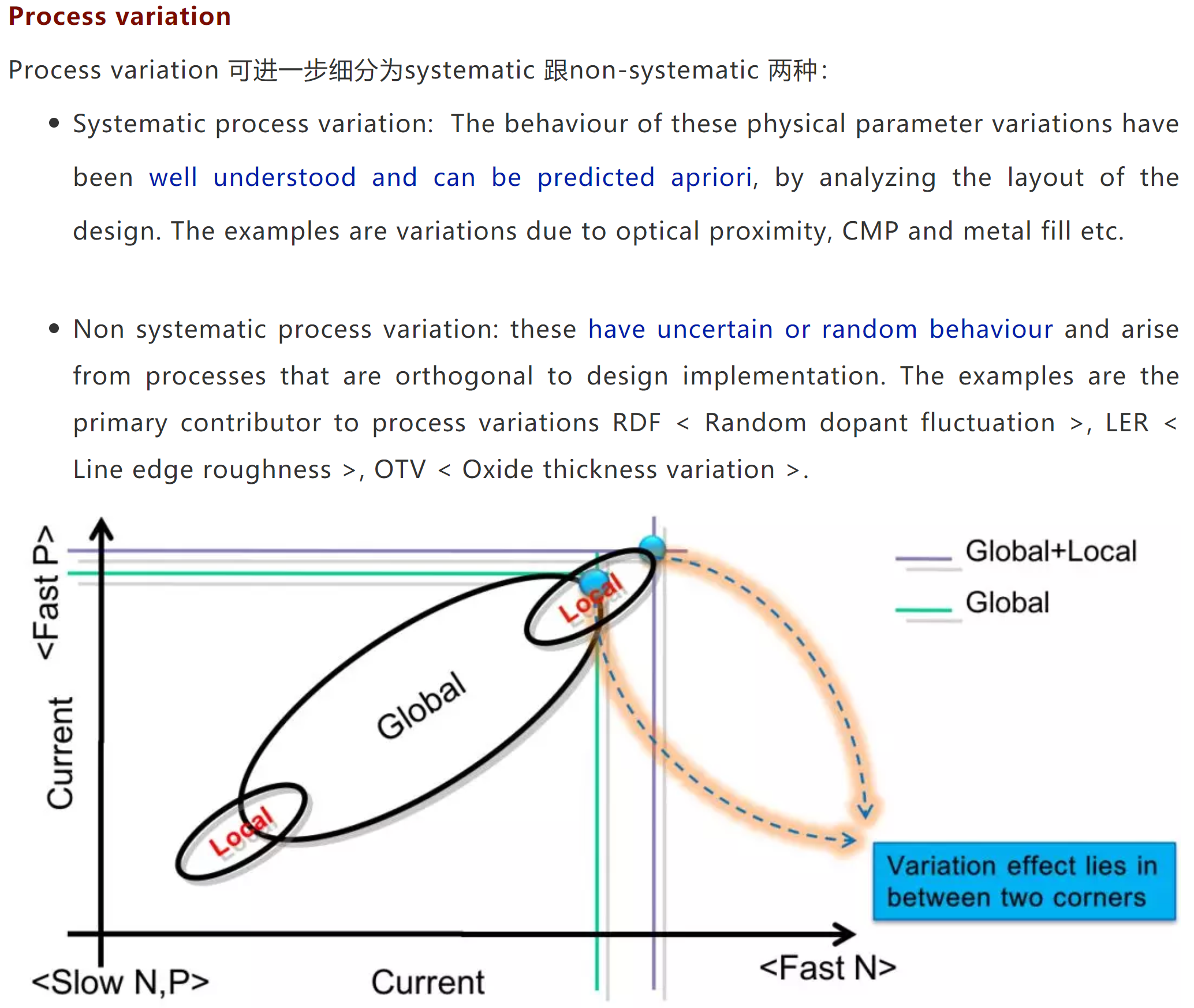

而Non systematic process variation又可以进一步细分为Global varation 和local variation:

-

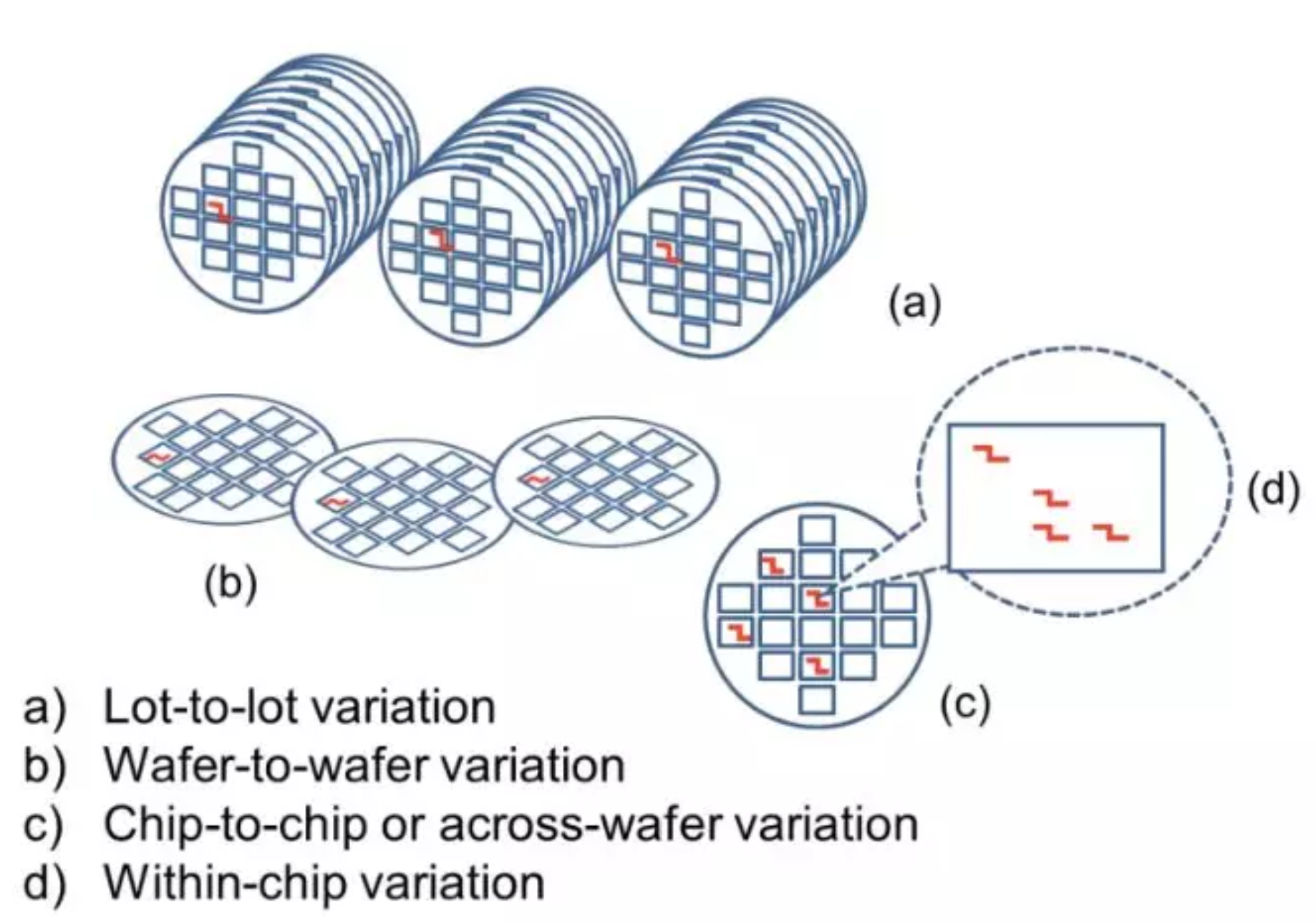

Global variation: 由于工艺偏移导致的die-to-die, wafer to wafer, lot to lot 之间偏差,如:同一个chip上所有管子的沟道长度都比典型值偏大或偏小。

- Local variation (within-die or intra-die): 同一芯片上不同管子受工艺偏差影响不同< 注:on chip variation 之源>,如:同一芯片上有些管子的沟道长度偏小,而有些管子的沟道长度却偏大。显然,local variation 比 global variation 小。

Local variation又可以进一步细分:

-

Spatially correlated variations: 相较于距离相距较远的管子,相邻管子有像似特征。这也是AOCV 跟 SOCV / POCV 要考虑 spatial / distance 的原因。

-

Random or independent variation: 在统计学上完全随机独立,故需要SSTA 对其进行更精确模拟,而作为SSTA的简化模型,SOCV / POCV的精确性从下图可见一斑。

结:

-

工艺偏差导致芯片物理参数偏差,进一步导致管子电特性偏差,在STA 中表现于cell delay, cell trantion 跟 net delay的偏差。

-

STA 用PVT + OCV 来模拟cell 的timing,用Spice 仿真得到cell delay 跟variation。

-

STA 用RC corner来模拟互连线的variation。

-

PVT 跟RC corner 用于模拟Global varition。

-

Flatten OCV, AOCV, SOCV / POCV 用于模拟local variation.

参考文献:

http://ceng.usc.edu/techreports/2012/Gupta%20CENG-2012-6.pdf

https://www2.eecs.berkeley.edu/Pubs/TechRpts/2015/EECS-2015-165.pdf

https://community.cadence.com/cadence_blogs_8/b/ii/posts/signoff-summit-an-update-on-ocv-aocv-socv-and-statistical-timing

https://m.eet.com/media/1177441/variation-aware%20ch4a.pdf

浙公网安备 33010602011771号

浙公网安备 33010602011771号