1.via

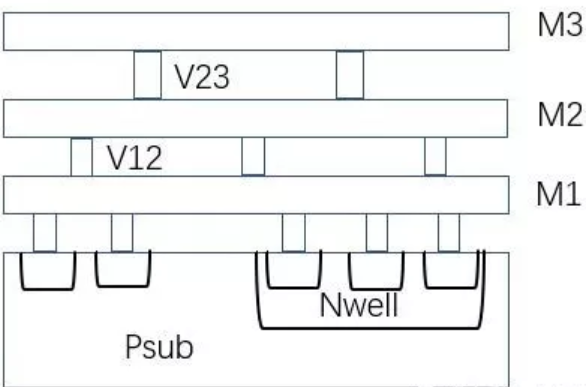

中文名称互连线通孔。我们知道,芯片的连线有不同层的金属互连线相互连接。而Via的作用就是连接这些不同层的金属。如下图所示:

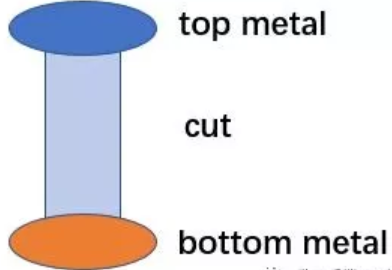

一个完整的通孔是由三层组成的,包括两个互连层和一个cut层,cut层可以理解为连接两层互连线的接口。比如V23,就代表着Metal 3与Metal 2之间的Via,中间是cut层,Metal 3是它的top metal, Metal 2是它的bottom metal。如下图所示:

Via的种类也分好多种,按照功能划分,可以分成regular via(信号线通孔)和power via(电源线通孔)。这个很好理解,信号线之间的连接用regular via,通常比较小一点;电源线之间的连接使用power via,通常会大一点。

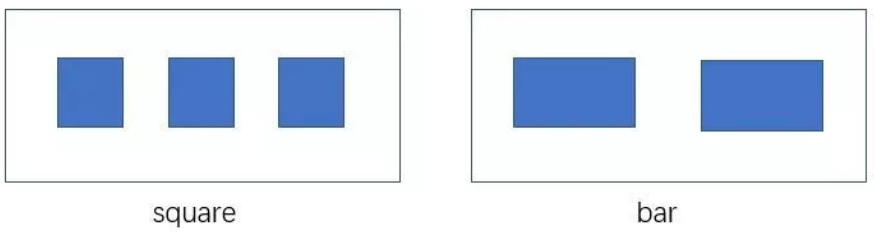

按照cut的形状,可以分为square(正方形)和bar(长方形)via,bar via拥有更大的cut面积,电阻可以更小一点。

按照cut的数量,可以分为single cut(单孔)和double cut(双孔),面积允许的话,一般建议尽量选择双孔的Via,电阻会较小。

2.

routing blockage(绕线阻碍物)。这个概念很简单,就是给某些金属加上blockage属性,让工具走线时不通过该区域。

可以使用命令create_routing_blockage创建

3.

Size Blockage,中文名称是扩散阻碍物

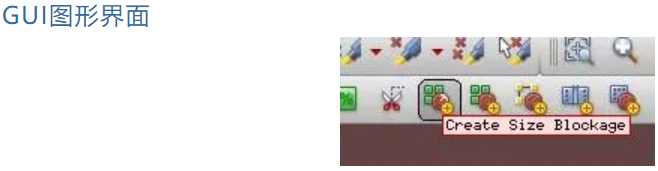

相对于其他blockage,这个blockage的使用频率很低。用处也不大,它可以阻止resize line穿过Size Blockage。换而言之,在做resize Floorplan时,被Size Blockage覆盖住的地方不会被resize,macro的相对位置会被keep住。但这只对自动resize Floorplan时有用,对于手动画resize line的方式,相对位置无法被keep住。

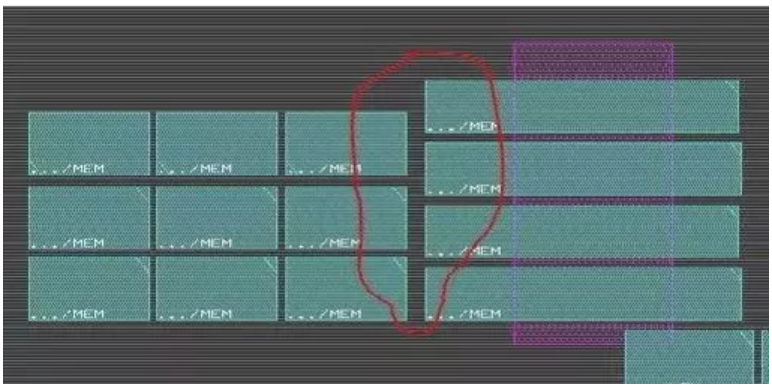

对照上下两图,当做了resize Floorplan将design的沿X方向扩大100um以后,Size blockage覆盖住的区域(红圈处),macro之间的相对位置不会变。

使用方法

addSizeBlockage

addSizeBlockage -name sBlkg1 -box 200 200 400 400

4.wire

后端工具里面的wire并不是指verilog网表里的wire线型。它是将net物理化的概念,每一条net在后端工具里面是由许多小段的wire组成,每一小段wire我们称之为wire segment.

wire按照类型可以分为Regular Wire(信号线),Special Wire(电源线),Patch Wire(补丁线)。

Regular Wire就是我们平常见到的信号连线,连接各个Signal Pin的金属线段。每层金属层上的Regular wire默认的宽度都是一样的。

Special Wire就是电源接地线,平常我们所见到的power ring,stripes,power rail等都是Special Wire。一般用高层金属走线。

Patch Wire,我们称之为补丁线。这是先进工艺中的一种走线,用于修复Min Area,Min Step等DRC,不属于任何net。

使用方法

create_shape

create_shape -shape_type polygon -layer METAL -boundary {{0 0} {0 1000} {500 1000} {500 0}}

5.

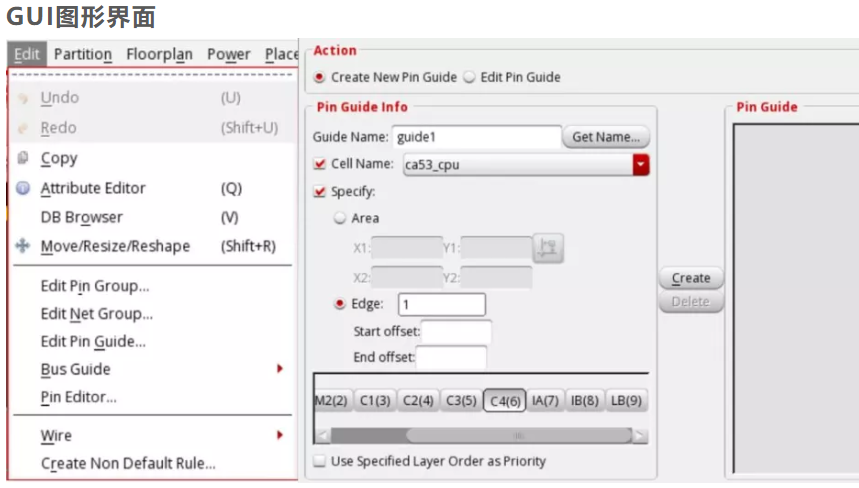

Pin Guide。这也是一种pin的约束。Pin Guide可以在partition边界上创建一块特定的区域,然后属于该Pin Guide中的bus, net, pin, net group, pin group都会被摆放在这块区域中。我们也可以给Pin Guide指定layer或者edge。通常,Pin Guide一般与pin group搭配使用。

使用方法

createPinGuide

createPinGroup pGroup1 -cell ALU -pin {INT[0] INT[2] INT[3]} -spacing 2

createPinGuide -area 678 371 778 787 -pinGroup pGroup1 -cell ALU

pGroup1会被摆放在pin guide区域{678 371 778 787}中,并且pGroup1中的pin会以间距为2的spacing,相邻摆放。

createPinGroup pGroup2 -cell TDSP -pinp_addr*

createPinGuide -edge 2 -pinGroup pGroup2-cell TDSP -layer Metal5

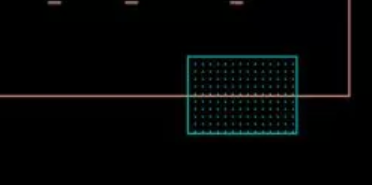

pGroup2会被摆放在partition edge 2上,并且pGroup2中pin会被assign在Metal5上。下图中白色区域就是Pin Guide。

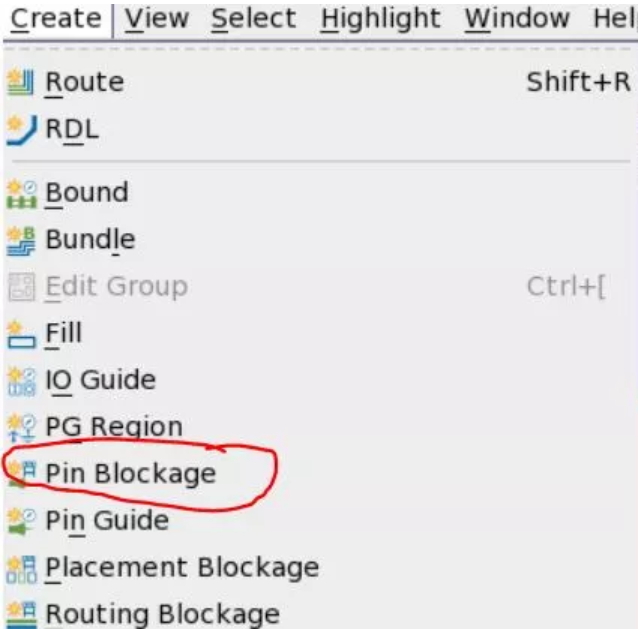

6. pin blockage

Pin Blockage(引脚阻碍物)。这是一种pin constraint,用于Pin assignment中。从名字中大家也能理解,带有pin blockage的区域,place pin时,不会将pin打在该区域。

需要注意的是Pin blockage只能打在module boundary的边界。下图中绿色部分就是pin blockage。该区域内,不允许放置pin。

使用方法:

命令:

create_pin_blockage -boundary {{100 100} {200 200}} -layers {M1 M2}

GUI

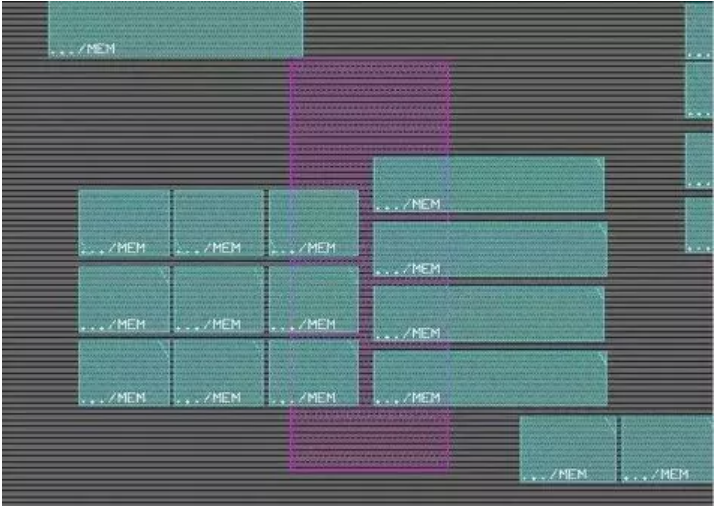

7. partition

中文名为划分,这是层次化设计中经常用到的一个概念。对于规模较大的设计,我们在物理上给予层次化器件一个物理约束(physical constraint),然后将具有物理约束的层次化器件定义为一个划分(partition),并切出整个设计,剩下的设计为顶层设计(Top)。顶层设计以及各个划分被视为单独的设计来做布局以及绕线,这样便可将一个超大规模的设计分为多个规模不是很大的设计,从而大大提高EDA软件对于设计的可容性和设计效率。

如下面示意图所示:我们将需要单独设计的module可以定义为partition,然后切分出去,在底层完成独立设计,最后再拼接回来。这就是partition的作用。

使用方法

definePartition

definePartition -hinst ctr_inst

-coreSpacing 0.56 0.56 0.0 0.0

-railWidth 0.0

-minPitchLeft 2 -minPitchRight 2

-minPitchTop 2 -minPitchBottom 2

-reservedLayer {1 2 3 4}

-pinLayerTop {2 4} -pinLayerLeft {3} -pinLayerBottom {2 4} -pinLayerRight {3}

-placementHalo 10.0 0.0 0.0 0.0 -routingHalo 10.0

-routingHaloTopLayer 7 -routingHaloBottomLayer 1

浙公网安备 33010602011771号

浙公网安备 33010602011771号