电平转换方法(一)

近日遇一3.3V转1.8V需求,起先使用电平转换芯片,然网络充斥各种电平转换芯片的天坑实例,因涉及核心功能,遂对主流的电平转换芯片做了筛选,整理总结,以备后用。

使用电平转换芯片案列。

1,MAX13013,用作PPS的电平转换,1.8V~3.0V,实际测试效果惨不忍睹,具体波形无,大致描述如:开始的上升沿OK,1ms的脉宽不断震荡,频率未知,pp值可能1V,均值能到3V,印象中如此,未确认。评估不可能能用。此为失败案列。最终采用比较器方案实现PPS输出。

通过PPS源端串接电阻,将上升时间拉长至100ns+,方可正常工作。但是,请记住,MAX13013的data rate标注为100MHz,one-shot。

------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

2018-5-8补充:

100MHz的data rate,10ns的周期,可支持1ns的上升沿波形,常规PPS一般为2ns上升沿,为什么不支持PPS。

------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

2,TXB0108,串口电平转换,应用成功。

3,MAX3375,串口电平转换,应用成功。

总结:电平转换芯片只在低速信号上应用成功,在高上升沿数据上未能验证,且有一失败案列。

说说最近两天的选型心得。

Maxim,即使MAX13013的前车之鉴就在眼前,可是好像也没有相关的资源信息了。使用MAX13055,8bit,100M data rate。物料也采购了,在核实原理图时,发现:不推荐上下拉信号。但是实际I2C与JTAG必然存在上下拉的情况,关键是one-shot的架构,确实让人望而却步,遂终止。不过貌似maxim家都是one shot加速。

TI,LSF0108,明确了既可以OD也可以push-pull,data rate 100MHz,Application包括GPIO,I2C,UART,SDIO,SDIO,理论上十几兆的信号肯定得没问题,而且结构为switch结构,不再是one-shot了,但是其实心里还是在打鼓。然而最终还是因为他的Application而选择了他,一切随缘吧。另做一套单向JTAG备选方案,因为JTAG确实不允许出任何差错。

Ti还有TXB0108,不过网上查到JTAG相关应用案列惨不忍睹,遂放弃。

Unidirection器件选型:主要是TI或者Nexperia。逻辑器件,很成熟,历史悠久系列并一直传承发展下来。常用的LVC,AVC系列。

此处的选型就不一一赘述了。

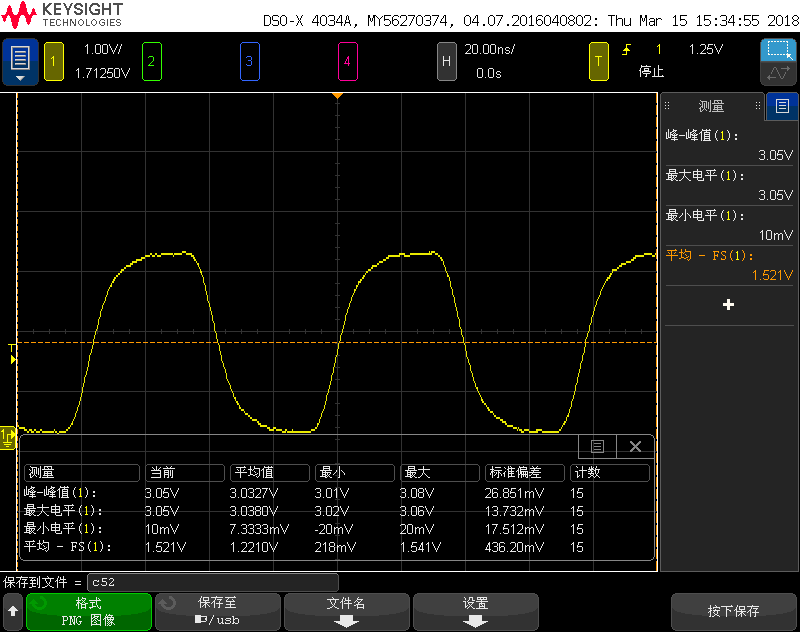

电阻分压方案详解。

3.3V转1.8V,想直接通过180R+150R的方式实现,已有成功案列。

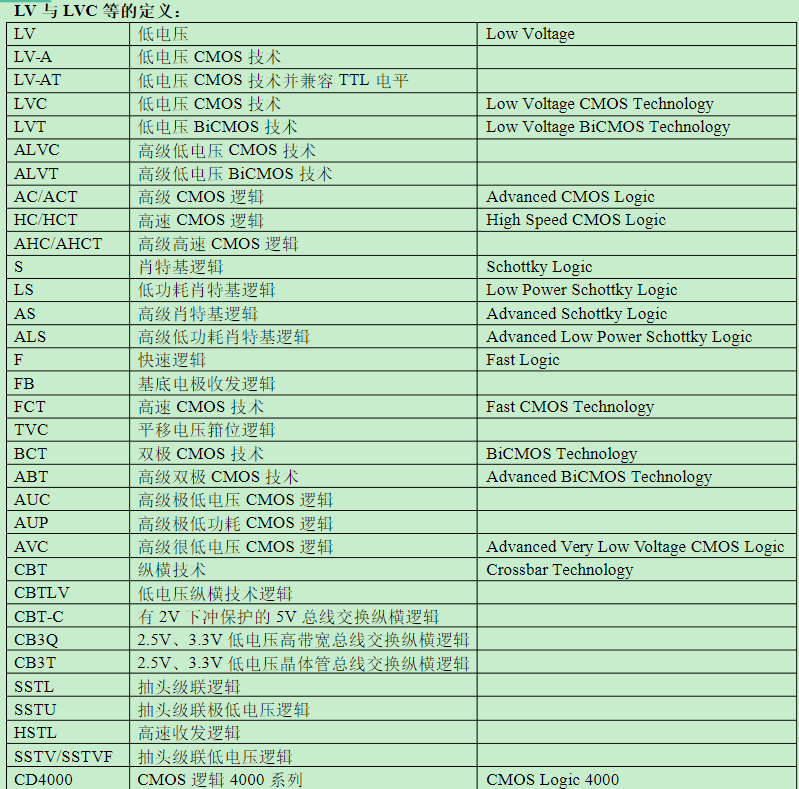

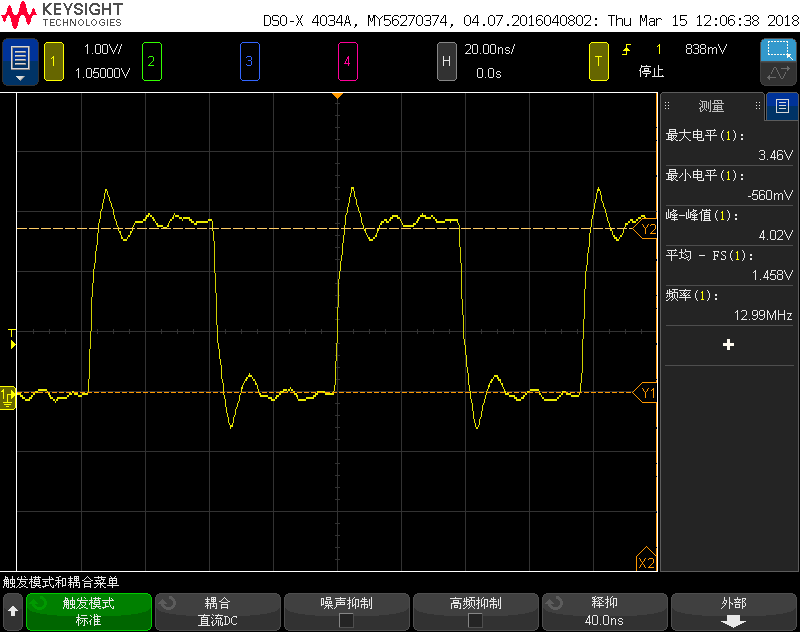

USB3318的CLK_OUT,CPU输出3.0V,电阻分压1.8V,电阻组合为180R+120R,实测波形如下。

3.0V,13MHz方波

1.8V 13MHz方便

直观上判断上升沿未有变化,100欧姆级别电阻分压在10MHz级别的频率下可行。

理论值上升时间增加为:假设负载电容为10pF。上升时间增加2.2RC=2.2X180X10X10e-12=4ns.

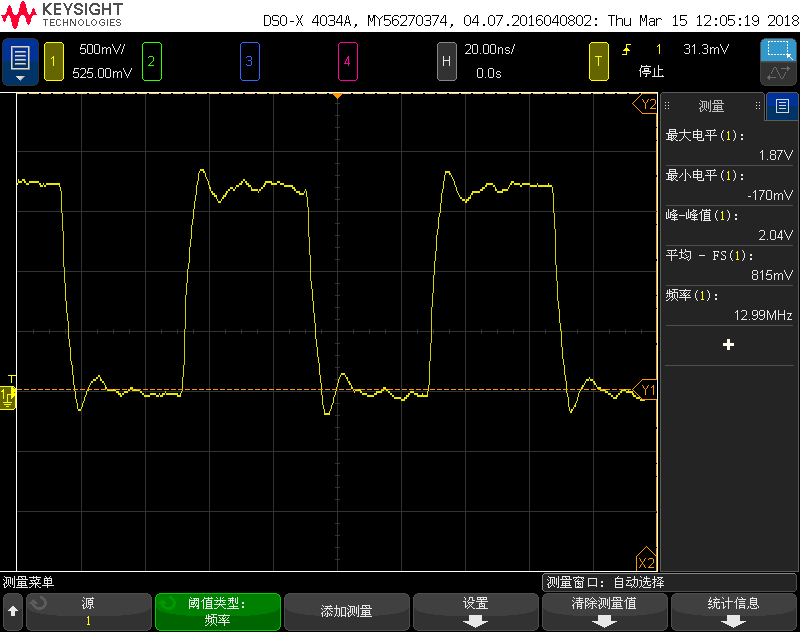

最初使用的1.8K+1.2K的组合是不生效的,pp值非常低,按照三角波的定义,设计上升时间为15ns~20ns,则需要串接电阻放大4~5倍。因受到实际电阻种类限制,电阻组合为880欧姆+390欧姆。理论增加上升时间19.5ns,实际测试波形如下。

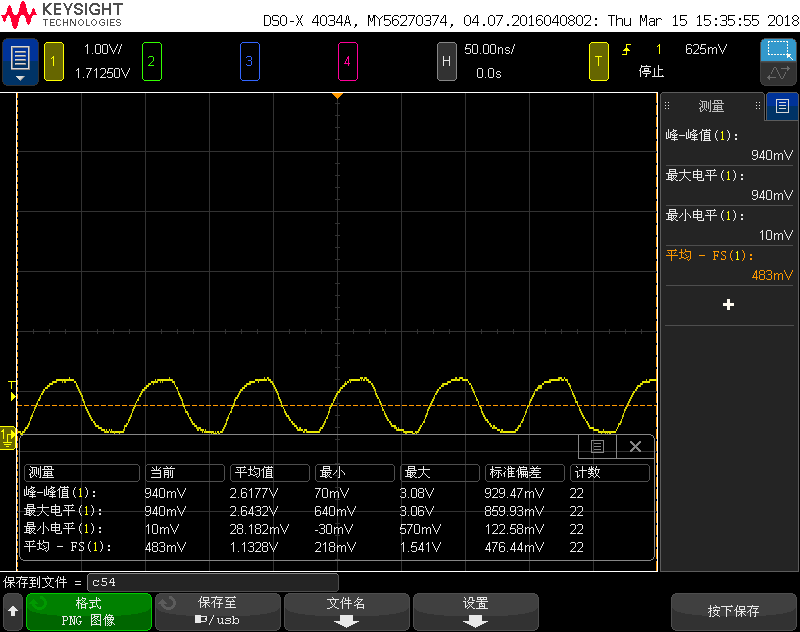

CPU输出波形:

理论上在880欧姆前端输入的波形应该是很好的方波才对,此处留一疑问。上升时间约为20ns,那么,负载端的10pF是不是设定得太巧了呢。

再缩小一些:

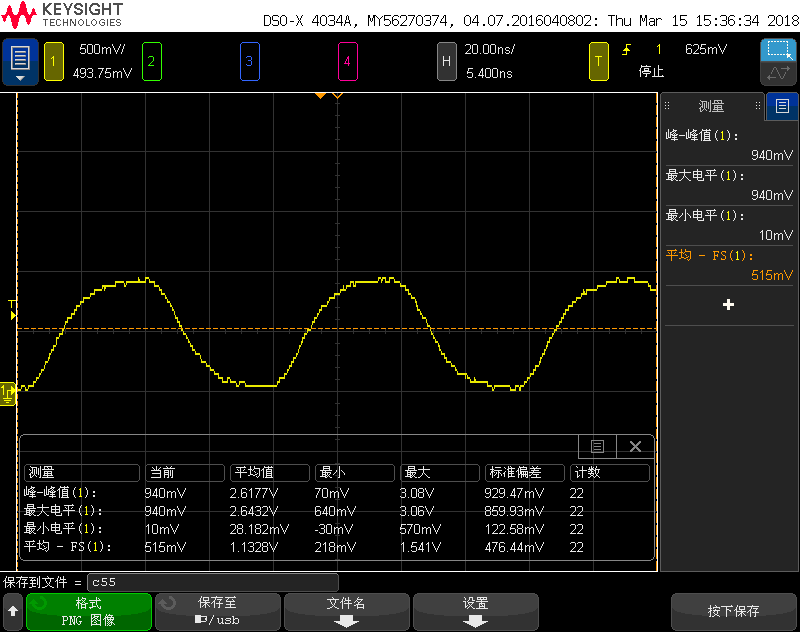

分压后的电压

大约为0.94V。与理论计算的结果一致,上升时间约为20ns。

放大一点:

基本上串接电阻对波形的影响与理论计算的结果是契合的。那么传输线的特征阻抗呢。

我是否能猜测当串接电阻大于传输线阻抗时,串接电阻为主要影响,串接电阻小于传输线阻抗时,传输线特征阻抗为主要影响。

此处可能需要结合信号完整性分析的部分章节去做验证。

摘自信号完整性第九章,有损线,上升边退化和材料特性。

50ps的信号经过FR4上36in,50Ω的trace之后,上升沿基本上退化到1ns。所以,对于上升沿大于1ns的信号,基本上可以忽略特征阻抗对上升沿的影响。

具体如何计算上升边沿损耗,涉及内容较多,尚待进一步研究。

假设源端串接22欧姆电阻,上升时间会增加0.5ns,对于100MHz以下的信号来说,可以忽略不计。