Sharc FLAGS I/O Register(flag0~3)

Core FLAG Pins Multiplexing

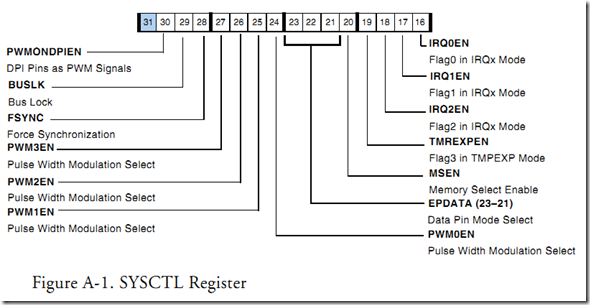

This module also includes the multiplexers of the FLAG0-3 pins shown in Figure 24-9. The FLAG0-2 pins can act as core FLAGS0-2 or IRQ0-2, or a memory

select MS2 (FLAG2 pin) and the FLAG3 pin can act as a core FLAG3 orthe TMREXP signal of the core timer or as a memory select MS3.

Flag pins (FLG3-0) are connected as input after reset.If more than four flags are required, they can multiplexed using the external port pins in the SYSCTL

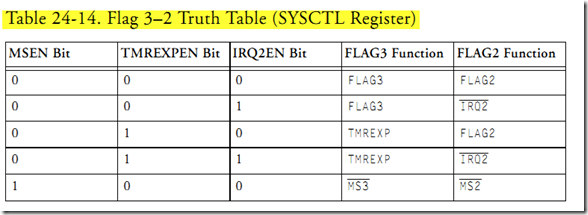

register or the DPI pins in the DPI registers.For a detailed flag description refer to the SHARC Processor Programming Reference. Table 24-14 provides

information on FLAG function based on the settings of the memory select enable, the flag timer expired and the FLAG2 interrupt bits in the system control register

code

#include <sysreg.h>

#include <def21489.h>

#include <cdef21489.h>

*pSYSCTL &= (~(MSEN|TMREXPEN|IRQ2EN));

sysreg_bit_set(sysreg_FLAGS, (FLG2O|FLG3O));

sysreg_bit_clr(sysreg_FLAGS, (FLG2|FLG3));

浙公网安备 33010602011771号

浙公网安备 33010602011771号