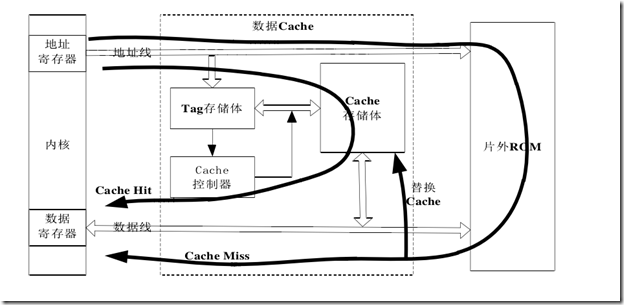

cache 基本原理

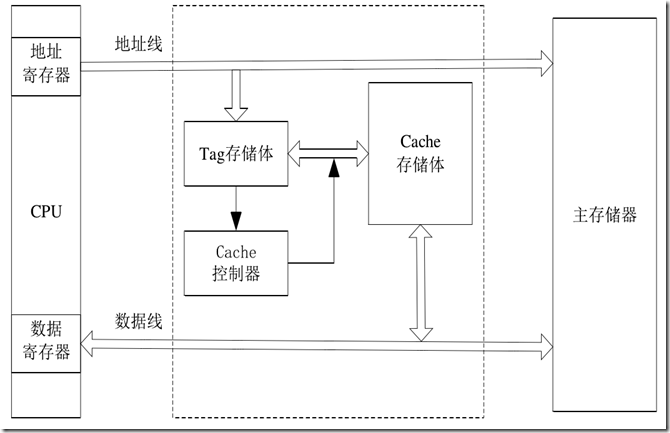

Cache 主要由 Cache Tag,Cache 存储体,Cache 控制模块组成。Cache Tag 主要用来记录 Cache 存储体中数据的位置和判断 Cache 内数据是否命中;

Cache 存储体主要用来存储片外数据,方便处理器直接调用;而 Cache 控制模块则控制整个Cache 的具体工作,它决定了 Cache 的工作效率。

cache基本结构图

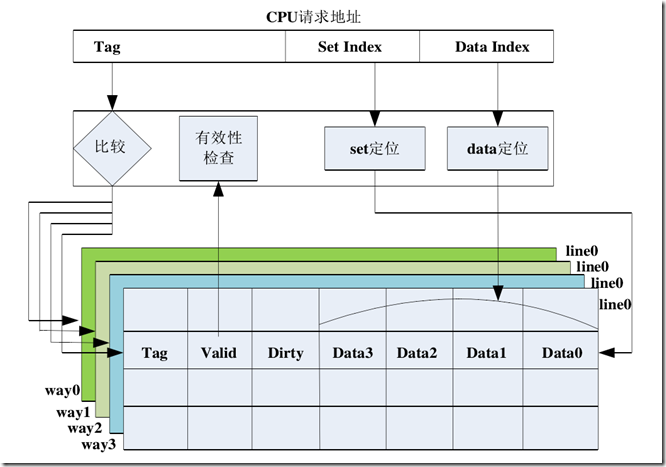

Cache 的组织结构

Cache 的状态信息位包括有效位,脏位,锁定位,只读位,LRU 位等等Cache 状态信息位记录该 Cache Line 的状态,比如有效位是用来判断该 Cache Line

是否有效的;而脏位是用来判断 Cache 数据是否与主存相同的;锁定位是用来强制保证 Cache 中该行不被修改的。本文描述的 Cache 使用了有效位和脏位。

当处理器返回修改过后的数据给 Cache 时,脏位就会置 1,表示已改变。当发生 Cache Line 被替换的事件时,Cache 控制器就会对脏位进行检测,若脏位

已经置 1 则该Cache Line 中的数据会被写入主存,保证 Cache 和主存数据的一致性

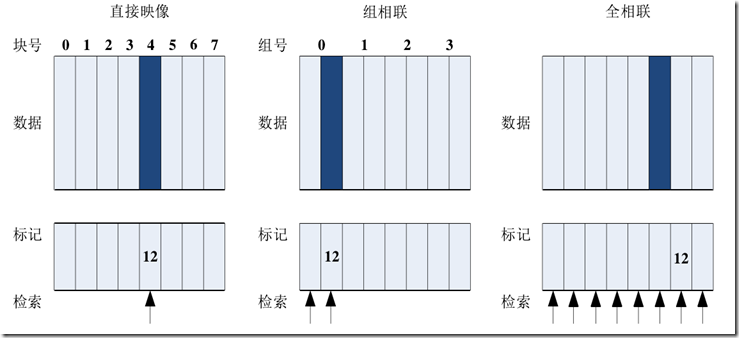

全相联映射中,主存中每个 Line 能映射到 Cache 中任意的一个 Line,其结是资源冲突少,命中率最高。缺点是电路比较复杂。因为在判断数据是否在 Cache

中时需要将当前地址和 SPRAM 中的所有地址一一进行比较,需要的比较器很多。另外会产生大量访问 Cache 的延迟,因此只能在较小的 Cache 中使用。

直接映射中,主存按照 Cache 空间大小分成若干容量相等的存储页,存储页中每个 Line 对应到 Cache 中固定的 Cache Line。主存地址对应 Cache Line 进行循

环分配。这种映射方式最容易实现,只需要将当前地址和 Cache 中的某一个地址进行比较,来判断是否命中。但是缺点比较明显,灵活性太差,空间利用率低,

Cache 中的资源冲突也很频繁,使得 Cache 命中下降。在高性能 DSP 中基本不采用该映射方式。

组相联映射是全相联映射方式和直接映射方式的结合。比如 4 路组相联就是将 Cache 分成 4 个相同的部分,每个部分都称为 Cache Way。主存分成若干容量相

等的存储页。而主存中每个 Line 都可以被存放在任意 Way 中的对应 Line。该实现方式复杂度比全相联方式低,Way 数目就是比较器所需数目。其映射方式也更加

灵活,从而资源冲突较少,命中率也较高。

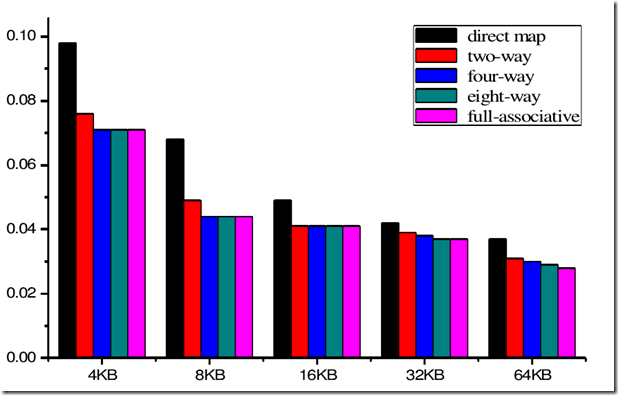

不同相联度的 Cache 中的缺失率

cache数据流向

浙公网安备 33010602011771号

浙公网安备 33010602011771号